ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

## **Reliability of Integrated Circuits and Semiconductor Devices**

# Dr. Lynn Fuller

Motorola Professor Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Fax (585) 475-5041 <u>LFFEEE@rit.edu</u> http://www.microe.rit.edu

Rochester Institute of Technology

Microelectronic Engineering

11-27-2003 Lec\_Reli.ppt

© 5 January, 2005 Dr. Lynn Fuller, Motorola Professor

#### **OUTLINE**

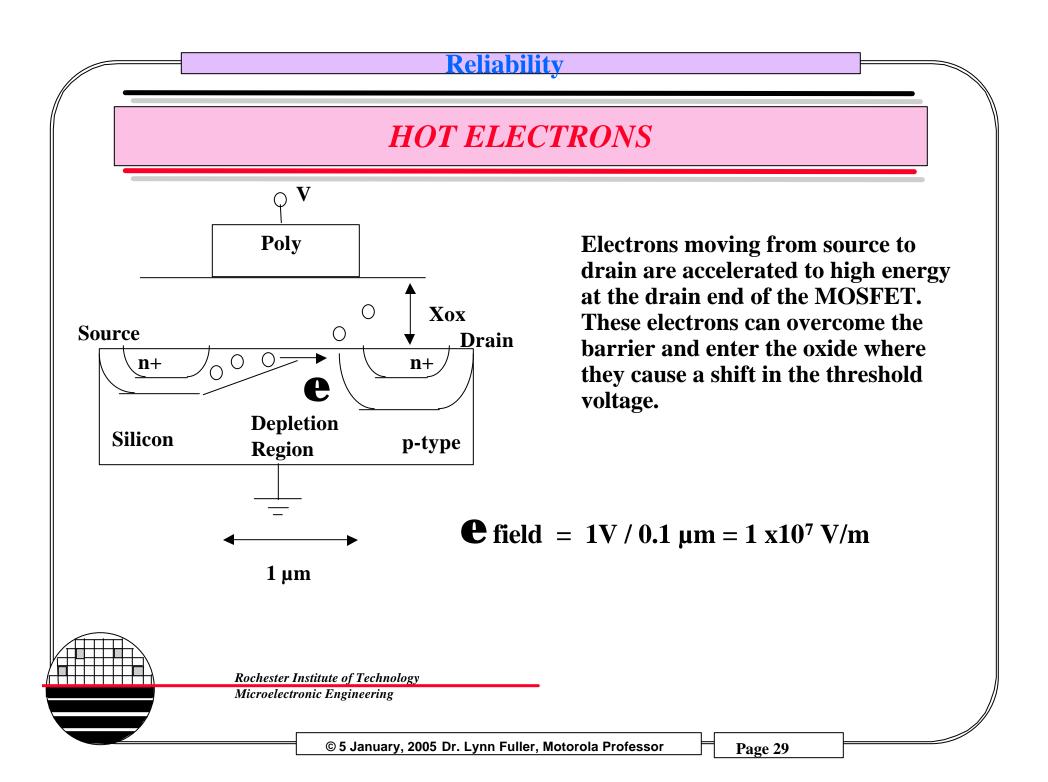

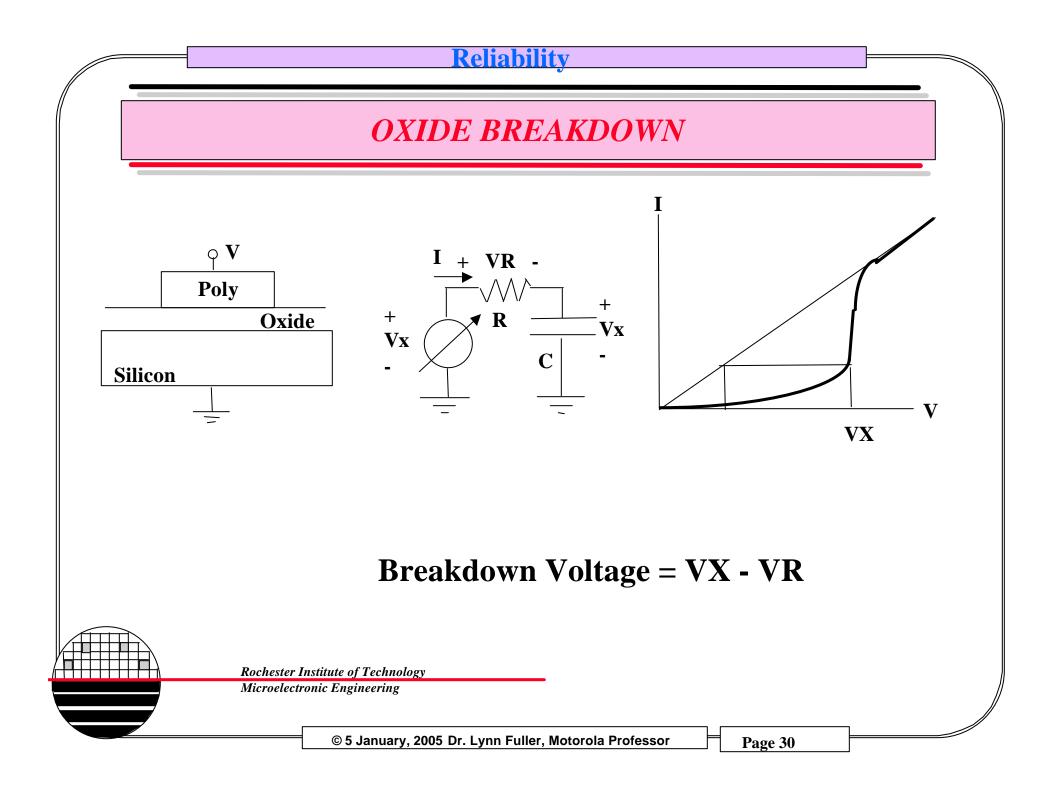

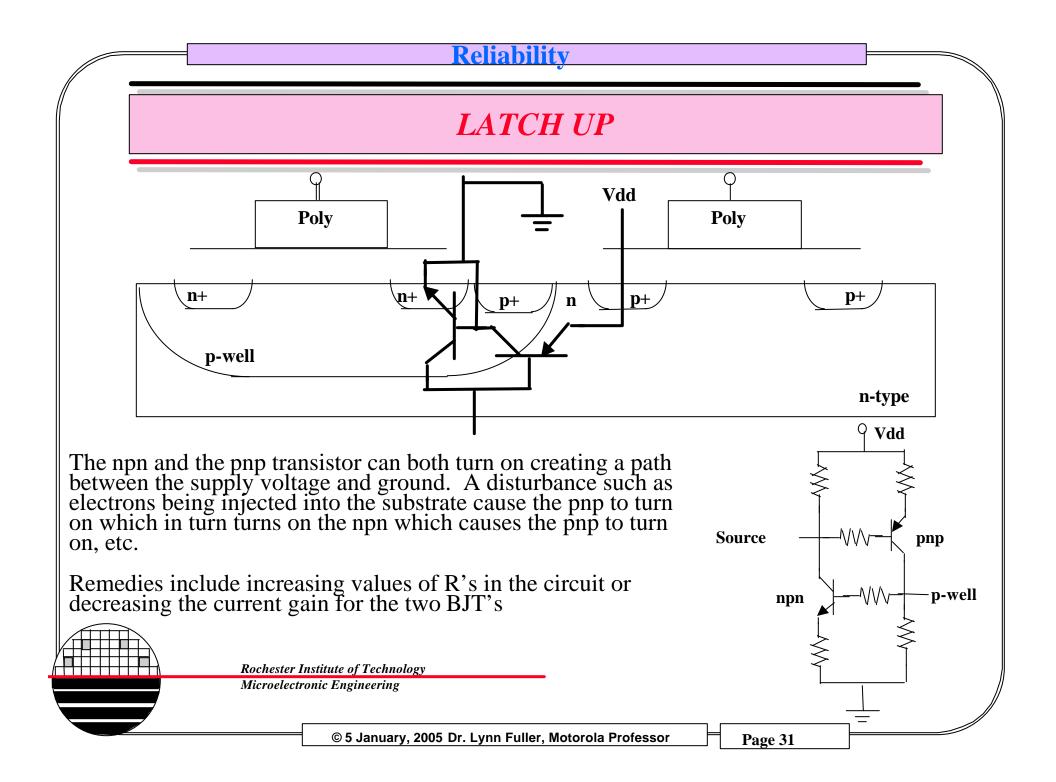

Introduction to Reliability Accelerated Testing Failure Mechanisms Electrostatic Discharge Alpha Particle Induced Soft Errors **Radiation Hard Devices** Aluminum Electromigration **Sodium Migration** Hot Electron Damage Oxide Breakdown Latch Up

Rochester Institute of Technology Microelectronic Engineering

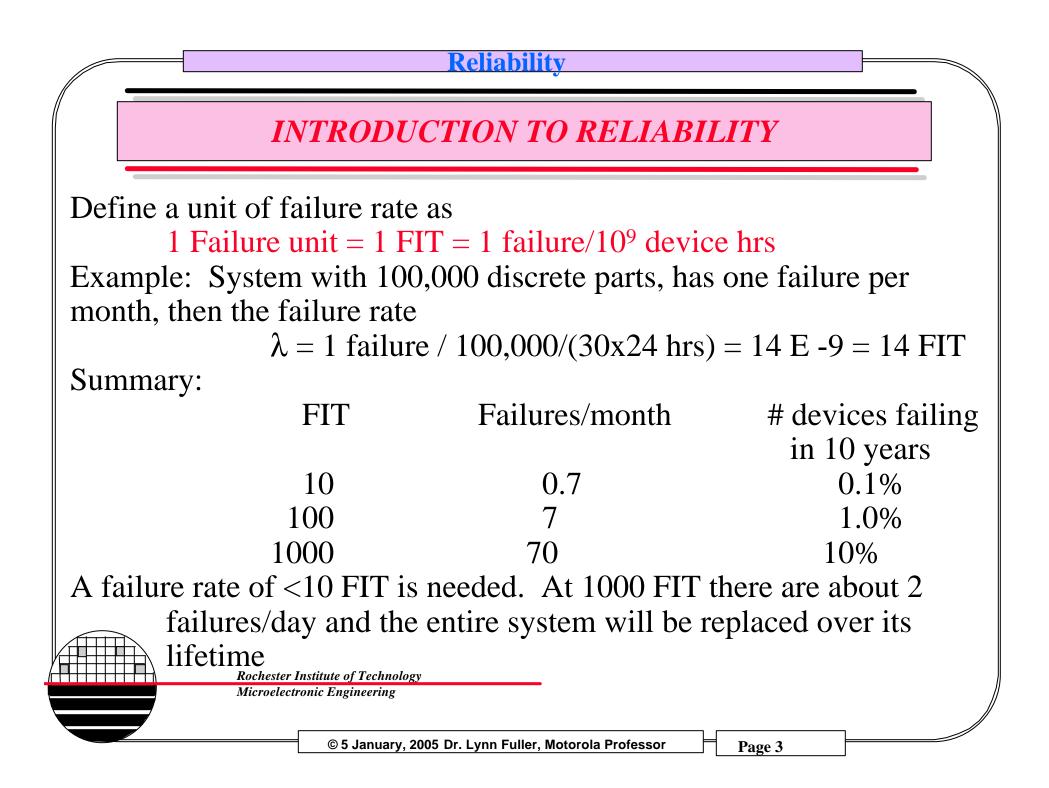

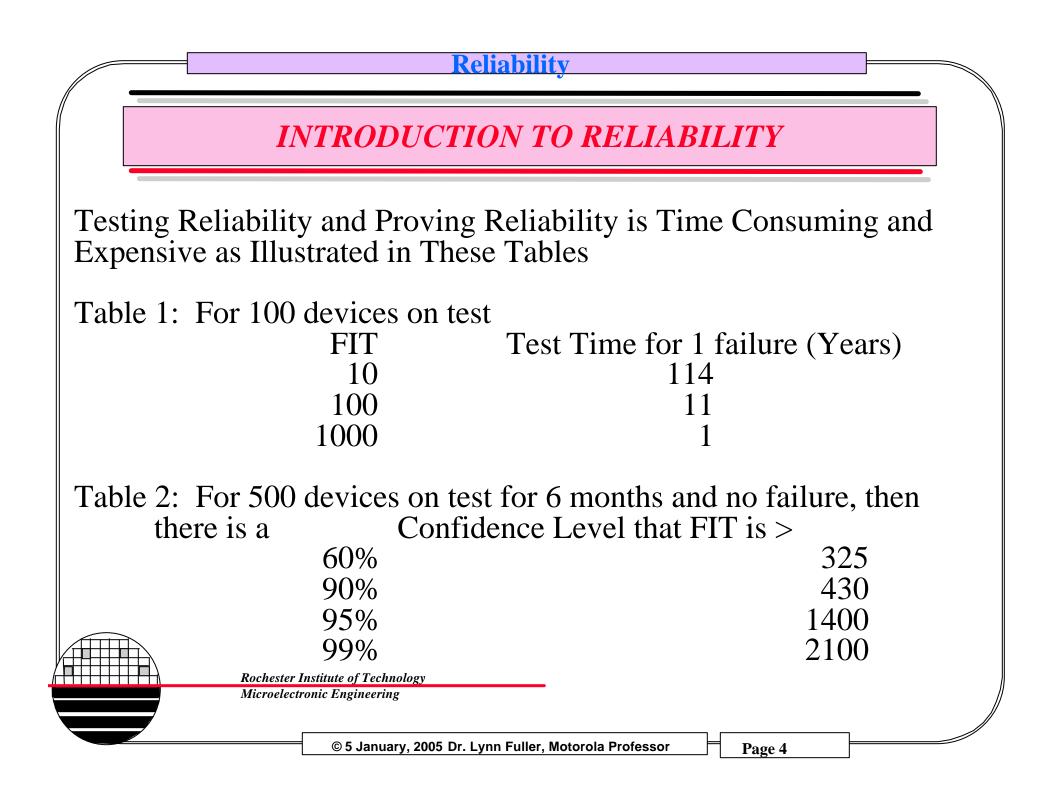

### **INTRODUCTION TO RELIABILITY**

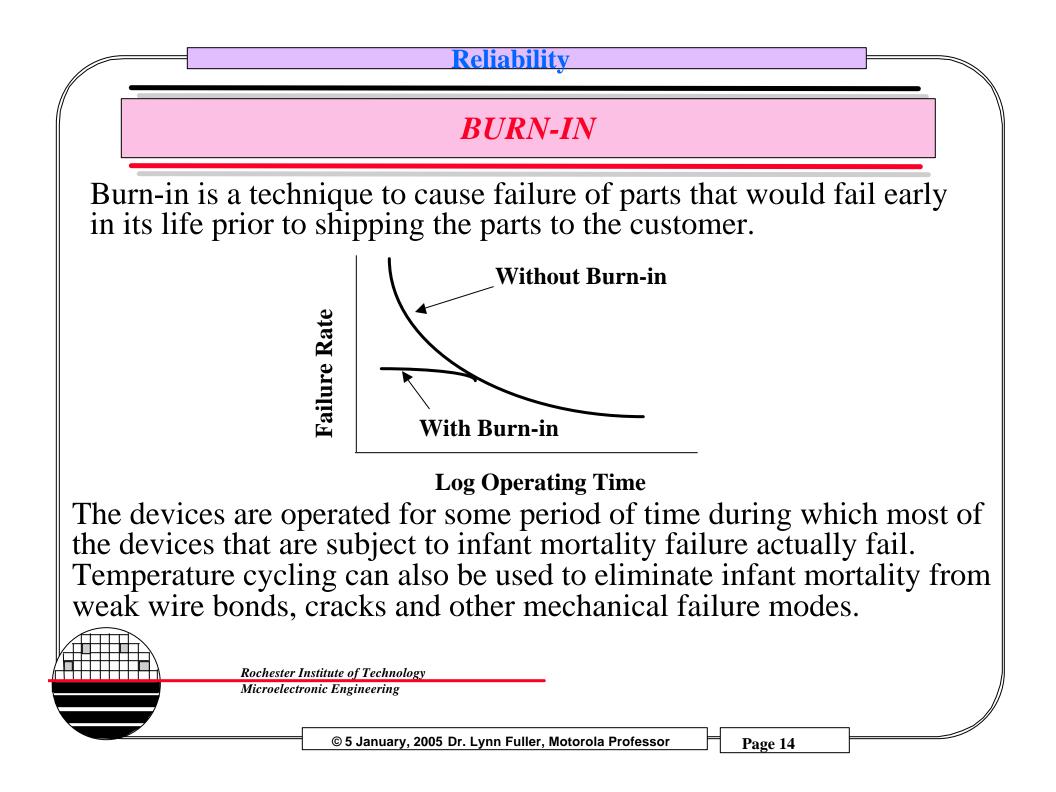

Testing is further complicated by the existence of more than one failure mechanism. Often one of the failure modes is characterized by a short median life and represents a small percentage of the total population, and represents the early failure mechanism. The remainder of the population has a longer median life and represents the steady-state failure mechanism. Burn in can find and eliminate the early failure devices.

## ACCELERATED TESTING

**Stresses are used to accelerate failure. For example temperature cycling is used to accelerate mechanical failure.**

- Temperature Acceleration

- Voltage Acceleration

- Current Acceleration

- Humidity Acceleration

Different failure mechanisms may be accelerated by different amounts for the same stress.

Rochester Institute of Technology Microelectronic Engineering

© 5 January, 2005 Dr. Lynn Fuller, Motorola Professor

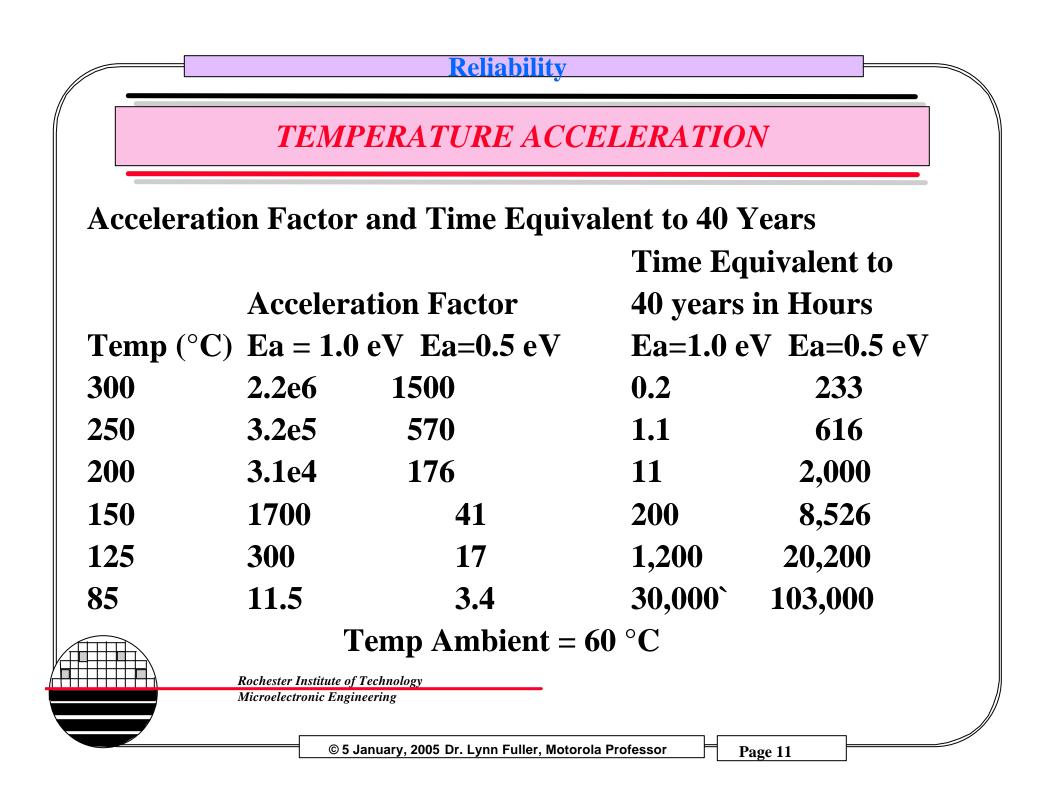

#### **TEMPERATURE ACCELERATION**

Temperature Acceleration can be used with many physical or chemical failure mechanisms. These mechanisms are often described by the Arrhenius Equation:

$\mathbf{R} = \mathbf{Ro} \exp \left[ \mathbf{Ea} / \mathbf{KT} \right]$

where R is the Response, Ro is the pre exponential term, Ea is the activation energy in electron volts, K is Boltzman constant (8.6e-5 eV/K) and T is temperature in degrees absolute.

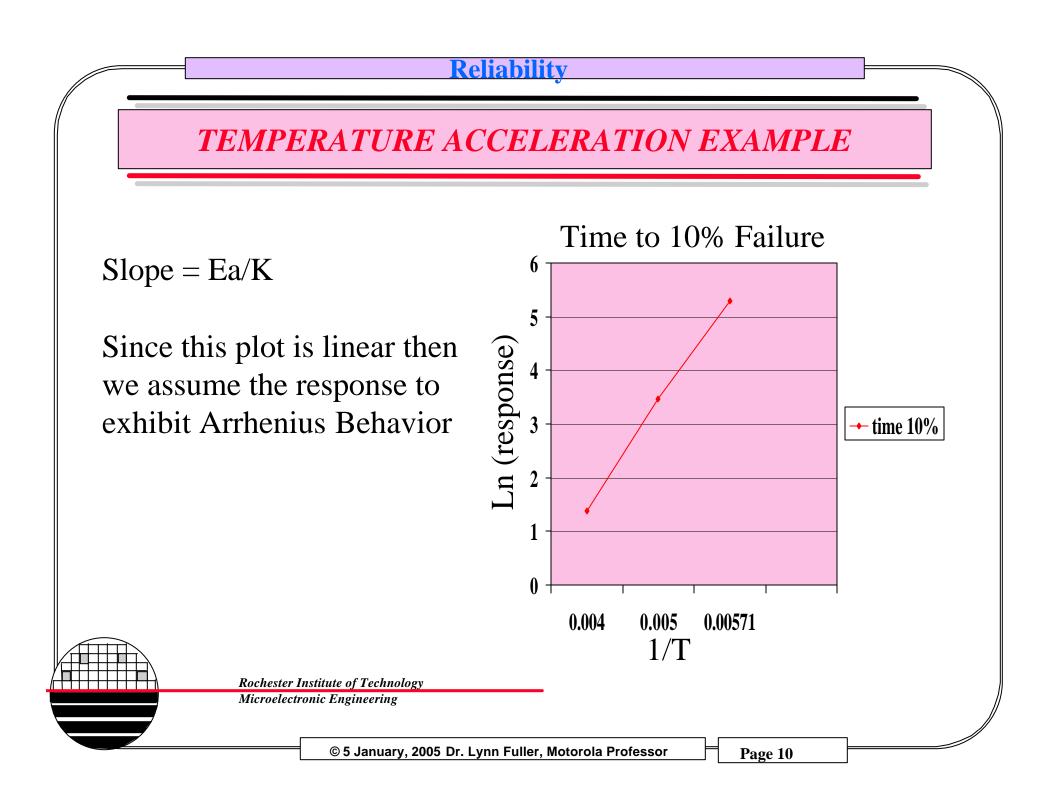

Plot the natural logarithm of the time to fail versus the inverse of the absolute temperature. The slope will give the activation energy.

#### **TEMPERATURE ACCELERATION EXAMPLE**

Example: 10% of metal lines fail due to electromigration failures in 200 hours at 175 C, in 32 hours at 200 C and in 4 hours at 250 C. Find the activation energy and pre exponential term, Ro. Plot the three points on ln(response) vs (1/T) plot.

Time for 10% failures = Ro exp[Ea/KT]

$$200 = \text{Ro exp} (\text{Ea/K}(273+175))$$

32 = Ro exp (Ea/K(273+200)) and K=8.6E-5 eV/K

## **VOLTAGE AND CURRENT ACCELERATION**

Most studies model voltage and current acceleration using voltage (or electric field) and current density raised to some power  $\gamma(T)$  that is a function of temperature.  $\gamma(T)$  usually has values between 1 and 5. Large increases in voltage can not be used because the integrated circuit will not function correctly but reliability measurements should be done at the extremes of allowed voltage.

$$\begin{split} R(T,V) &= Ro(T) V^{\gamma(T)} \\ R(T,J) &= Ro(T) J^{\gamma(T)} \text{ where } Ro(T) \text{ is a constant} \end{split}$$

Increasing voltage can accelerate dielectric breakdown, accumulation of interface charge, and corrosion. Increasing current density accelerates electromigration.

Rochester Institute of Technology Microelectronic Engineering

© 5 January, 2005 Dr. Lynn Fuller, Motorola Professor

#### HUMIDITY-TEMPERATURE ACCELERATION

Hermetic packages prevent water from reaching the integrated circuit. Only metal and ceramic packages are hermetic. Plastic packages are much less expensive but will allow water to quickly penetrate to the integrated circuit. Humidity (water vapor) accelerates corrosion and can cause metallization failure.

Testing of the seal integrity of Hermetic packages are called leak tests. Packages are first tested for gross leaks by immersing in hot flouroinert liquids and looking for bubble escaping from the package as the gas inside expands due to the increase in temperature. If the package passes the gross leak test it is given the helium leak test. The packaged devices are placed in a chamber that can withstand 2000 psi. The chamber is evacuated then back filled with helium at 2000 psi. and left for 1 hour. Any leaking packages will be filled with helium. The packages are removed and placed in a chamber attached to a helium leak detector. As the leak detector pumps on the chamber it can detect helium from packages that have leaks.

Rochester Institute of Technology

Microelectronic Engineering

#### FAILURE MECHANISMS IN SILICON DEVICES

| Device<br>Association  | Failure<br>Mechanism                                             | Relevant<br>Factors                       | Acceleration<br>Factors | ng Acceleration<br>Activation Energy                                        |

|------------------------|------------------------------------------------------------------|-------------------------------------------|-------------------------|-----------------------------------------------------------------------------|

| Oxide and<br>Interface | Surface Charge<br>Dielectric                                     | Mobile Ions,V,T<br>E,T                    | T<br>E,T                | Ea = 1.0-1.05<br>E <sup><math>\gamma</math></sup> , $\gamma$ , (T) = 1- 4.4 |

|                        | Breakdown<br>Charge Injection                                    | E,T,Qf                                    | E,T                     | Ea = 0.2 - 1.0  eV<br>Ea = 1.3  (trapping)<br>Ea = 1.0  (hot electron)      |

| Metal                  | Electromigration                                                 | T,J,A,<br>gradients of<br>T,J, grain size | T,J                     | Ea = 0.5-1.3 eV<br>J $\gamma$ , $\gamma$ , (T) = 1-4                        |

|                        | Corrosion                                                        | Contamination                             | H,V,T                   |                                                                             |

| Bonds                  | Intermetallics                                                   | T, impurities                             | Т                       | Ea = 1.0 - 1.05 eV                                                          |

| Hermaticity            | Seal Leaks                                                       | Pressure                                  | Pressure                |                                                                             |

|                        | Rochester Institute of Technology<br>Microelectronic Engineering |                                           |                         |                                                                             |

|                        | © 5 January, 2005                                                | Dr. Lynn Fuller, Motorola Pro             | ofessor                 | Page 15                                                                     |

**EXAMPLES OF FAILURE MECHANISMS**

Electrostatic Discharge Alpha-Particle-Induced Soft Errors Radiation Hard Devices Metal Electromigration Sodium Metal Migration in Gate Oxide Hot Electrons Oxide Breakdown Latch Up in CMOS Circuits

Rochester Institute of Technology Microelectronic Engineering

© 5 January, 2005 Dr. Lynn Fuller, Motorola Professor

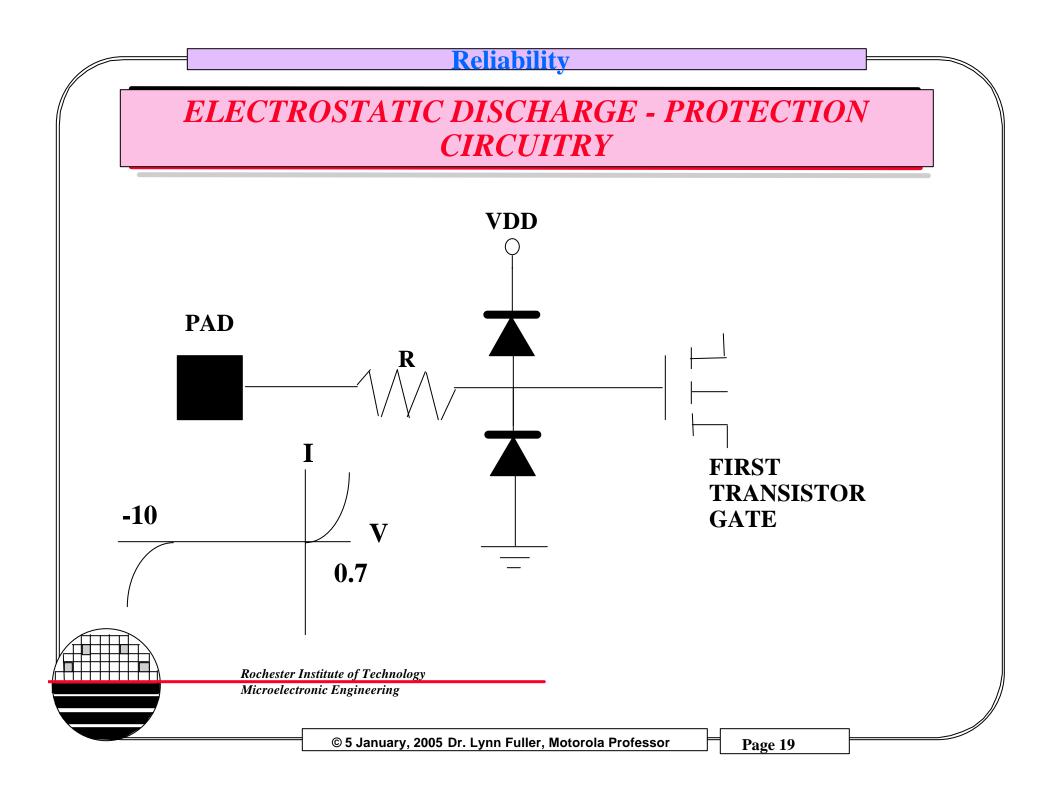

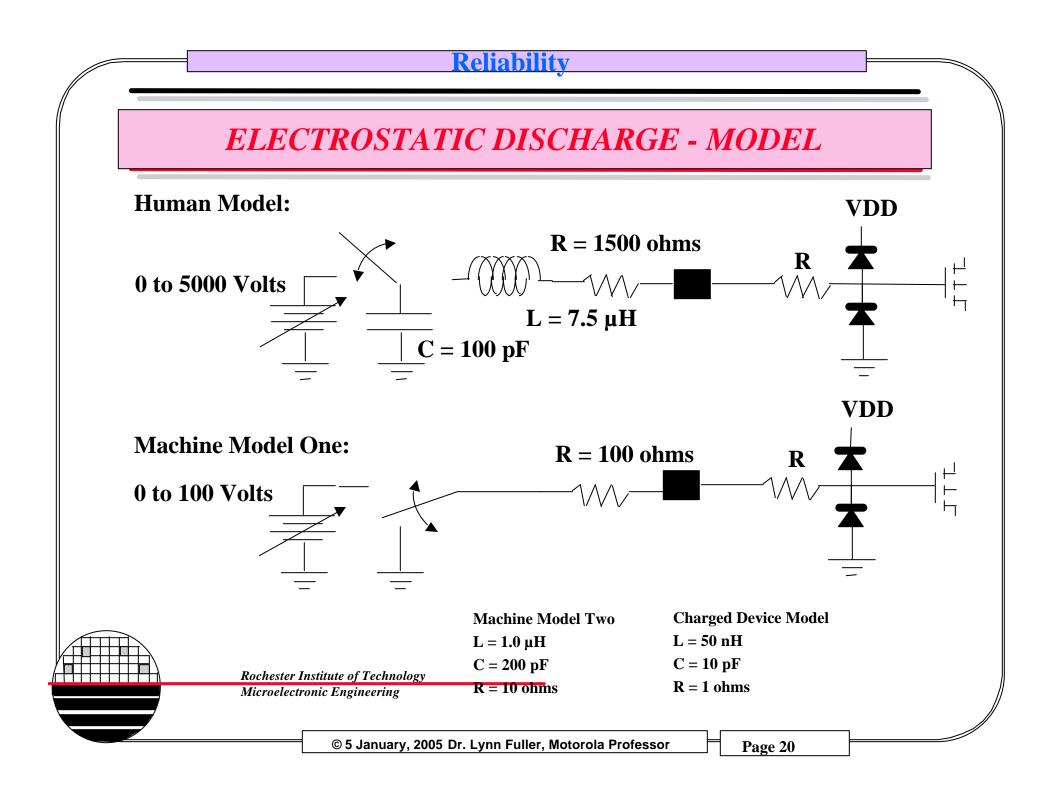

#### ELECTROSTATIC DISCHARGE

**Electrostatic Discharge (ESD)**

Dielectric Breakdown Strength of SiO2 is approximately 8 E6 V/cm, thus a 250 Å gate oxide will not sustain voltages in excess of 20 V

Triboelectricity (electricity produced by rubbing two materials together) can generate high voltages. A person walking across a room can generate 20,000 Volts and if discharged into an IC can cause immediate failure or damage that will reduce operating life. Even with proper handling several hundred volts can be applied to the IC. Therefore, protection circuitry is needed to provide a safe path for discharge of this electricity.

Rochester Institute of Technology Microelectronic Engineering

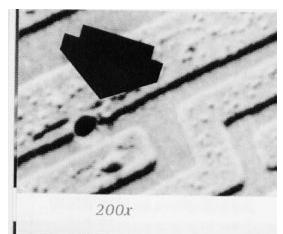

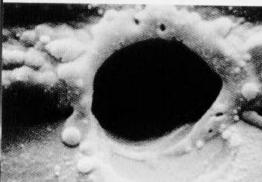

# Reliability ESD DAMAGE Rochester Institute of Technology Microelectronic Engineering © 5 January, 2005 Dr. Lynn Fuller, Motorola Professor Page 18

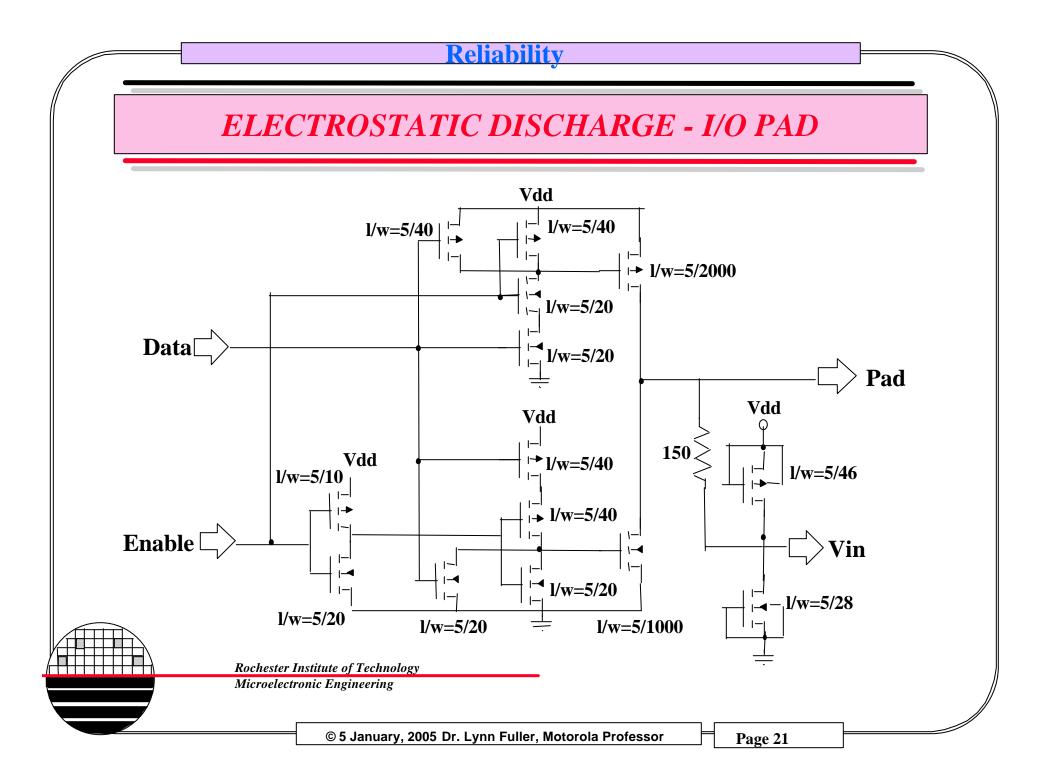

#### ELECTROSTATIC DISCHARGE - I/O PAD

### ALPHA PARTICLE INDUCED SOFT ERRORS

Radioactive elements, such as uranium or thorium, are naturally occurring impurities in IC packaging materials. The alpha particles emitted by these materials can cause soft errors in the ICs. The term "soft error" refers to a random failure not related to a physically defective device. The penetration of an alpha particle into the silicon causes the generation of an electron-hole plasma along the path of the particle. The generated carriers can cause the loss of information stored in the memory cells of a dynamic memory or stored in the depletion region of the drains of devices making up circuits such as dynamic shift registers or other logic units. The adsorption of a 4 MeV alpha particle can generate 10e6 electron hole pairs, which is equal to or greater than the charge stored in a dynamic memory cell.

## ALPHA PARTICLE INDUCED SOFT ERRORS

To illustrate the seriousness of the problem, a typical soft error rate in a memory system containing 1000 16K memory devices may be on the order of one soft error per 1000 hour, corresponding to a device failure rate of 1000 FIT.

The incidence of soft errors can be reduced by surrounding or coating the IC chip with a material having a very low density of radioactive contamination. For example, alpha particles with an energy up to 8 MeV are completely absorbed in 50  $\mu$ m of silicon rubber, and this material does not emit any significant amount of alpha particles

Military and Space Applications Need Radiation Hardened CMOS Integrated Circuits (See Harris Radiation Hard Data Book)

Radiation Damage Causes Vt Shifts Reduced Mobility (lower gm) Degradation of Field Vt Latch-up

Radiation Hardened Devices Use SOS or SIMOX Technology Thin Gate Oxides, Shallow Devices n-MOS Rich Circuit Designs P-Well Technology with Guard Rings

Rochester Institute of Technology

Microelectronic Engineering

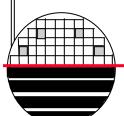

## **ALUMINUM ELECTROMIGRATION**

Electromigration is the process whereby a flow of electrons moves aluminum atoms in the direction of the flow. Since these atoms are about 20,000 times heavier than electrons, they must be thermally activated and the current density must be high. High current density occurs wherever a thinning of the metal trace occurs, either a design error, step coverage problem, scratch, void or point defect. Larger grains are harder to move than fine grains and grain size is proportional to the film thickness. Covering the aluminum with a passivation layer can reduce electromigration by a factor of 10, using a 2 to 8% mixture of copper in the aluminum can reduce electromigration by another factor of ten.

#### $\mathbf{MTF} = \mathbf{C} \mathbf{Area} / \mathbf{J}^2 \mathbf{exp} \mathbf{-Ea} / \mathbf{KT}$

Rochester Institute of Technology Microelectronic Engineering where C is a constant, J is Current Density, and Ea is the activation energy

## SUMMARY FOR RELIABILITY

The trend in modern VLSI technology will make the problems of maintaining high yield and high reliability more difficult.

Small Dimensions Higher Electric Fields, Larger Current Densities, Larger chip size Higher Power Dissipation, More Temperature Stress More complex processes New Materials Systems and New Failure Mechanisms

New Process Development must include identification and characterization of these failure mechanisms.

#### **EXAMPLE**

The gate oxide used in this CMOS process was studied through TDDB (Time Dependent Dielectric Breakdown) by aging large area (0.1 cm2) capacitors at 100 C and 150 C. Time to failure data were collected using both temperature and electric field as acceleration variables to characterize extrinsic and intrinsic failure modes. The extrinsic or defect mode is the primary source for oxide degradation on devices and results from localized weak spots induced from the manufacturing process. The intrinsic failure mechanism is related to the robustness of the technology and normally occurs well past the intended product live. Both linear (pessimistic) and reciprocal (optimistic) electric field acceleration models were used. The projected test structure extrinsic failure rates for 3.3 V and 80 C operation are 1 FIT for the linear model and <10- 4 FIT for the reciprocal model. Intrinsic oxide life was determined from measurements taken at 7 and 8 MV/cm and 150 C. Extrapolating to 3.3V and 80 C use conditions, the median time to failure for intrinsic life is 5.6E8 hours using the linear model and 1.1E16 hours using the reciprocal model.

**Rochester Institute of Technology**

Microelectronic Engineering

## HOMEWORK - RELIABILITY

1. What is the definition of the FIT?

2. Calculate the voltage that corresponds to breakdown electric field for 150 Å SiO2 gate oxide.

Rochester Institute of Technology Microelectronic Engineering

© 5 January, 2005 Dr. Lynn Fuller, Motorola Professor