ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

# **SPICE Examples**

# **Dr. Lynn Fuller**

Electrical and Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Fax (585) 475-5041 Dr. Fuller's Webpage: <u>http://people.rit.edu/lffeee</u> Email: Lynn.Fuller@rit.edu

Dept Webpage: <u>http://www.microe.rit.edu</u>

Rochester Institute of Technology

Microelectronic Engineering

1-2-2014 SPICE\_Examples.ppt

© January 2, 2014 Dr. Lynn Fuller

# **ADOBE PRESENTER**

This PowerPoint module has been published using Adobe Presenter. Please click on the Notes tab in the left panel to read the instructors comments for each slide. Manually advance the slide by clicking on the play arrow or pressing the page down key.

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

# **OUTLINE**

Introduction **Text Input Files** DC, Transient, AC Analysis LC Filter Inverters, NMOS, PMOS, CMOS Rise Time, Fall Time, Gate Delay **Ring Oscillator** Combinatorial Logic, NOR, 4 to 1 MUX Inverter with Hysteresis Oscillators 2 Phase Non Overlapping Clocks Analog Switch Op Amps, CMOS, BJT Waveform Generator **Operational Transconductance Amplifier (OTA) AM** Receiver References Homework

Microelectronic Engineering

# **INTRODUCTION**

SPICE (Simulation Program for Integrated Circuit Engineering) is a general-purpose circuit simulation program for non-linear DC, nonlinear transient, and linear AC analysis. Circuits may contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, transmission lines, switches, and several semiconductor devices: including diodes, BJTs, JFETs, MESFETs, and MOSFETs. Circuits with large numbers of all types of components can be simulated.

SPICE input files and output files are simple text files (e.g. name.txt)

Input files include a TITLE, circuit description NET LIST, analysis directives (COMMANDS), and lists of other text files to include (INC) such as model libraries (LIB) and an END command.

**Rochester Institute of Technology**

Microelectronic Engineering

# **INTRODUCTION**

PSpice Lite 9.2 is one of the OrCAD family of products, from Cadence Design Systems, Inc., offering a complete suite of electronic design tools. It is free and includes limited versions of OrCAD Capture, for schematic capture, PSpice for analog circuit simulation and Pspice A/D for mixed analog and digital circuit simulation. PSpice Lite 9.2 is limited to 64 nodes, 10 transistors, two operational amplifiers and 65 primitive digital devices. See page 35 (xxxv) of the PSpice Users Guide.

LT SPICE – is a free SPICE simulator with schematic capture from Linear Technology. It is quite similar to PSpice Lite but is not limited in the number of devices or nodes. Linear Technology (LT) is one of the industry leaders in analog and digital integrated circuits. Linear Technology provides a complete set of SPICE models for LT components.

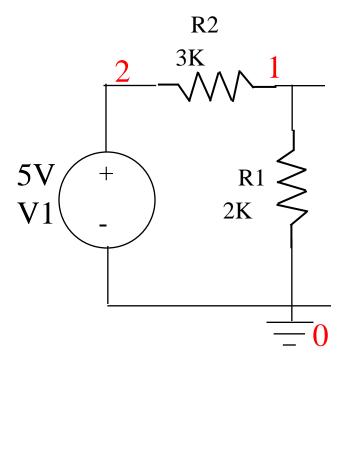

**CREATING THE INPUT FILE**

The input file can be generated from a schematic capture program, or just typed in a text editor such as "Notepad" or "WordPad"

\*Simple Resistor Divider R1 1 0 2K R2 2 1 3K V1 2 0 DC 5 .DC V1 0 5 .1 .END

Rochester Institute of Technology

Microelectronic Engineering

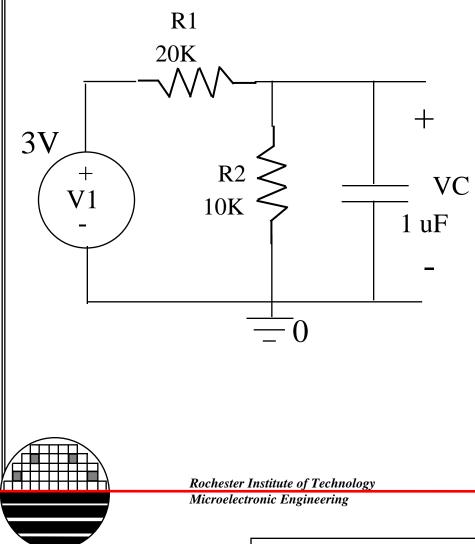

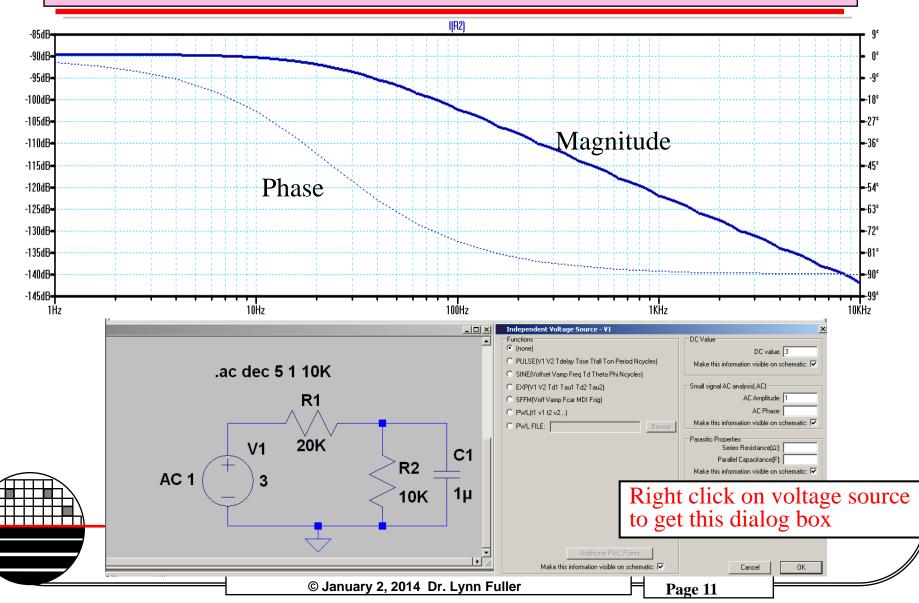

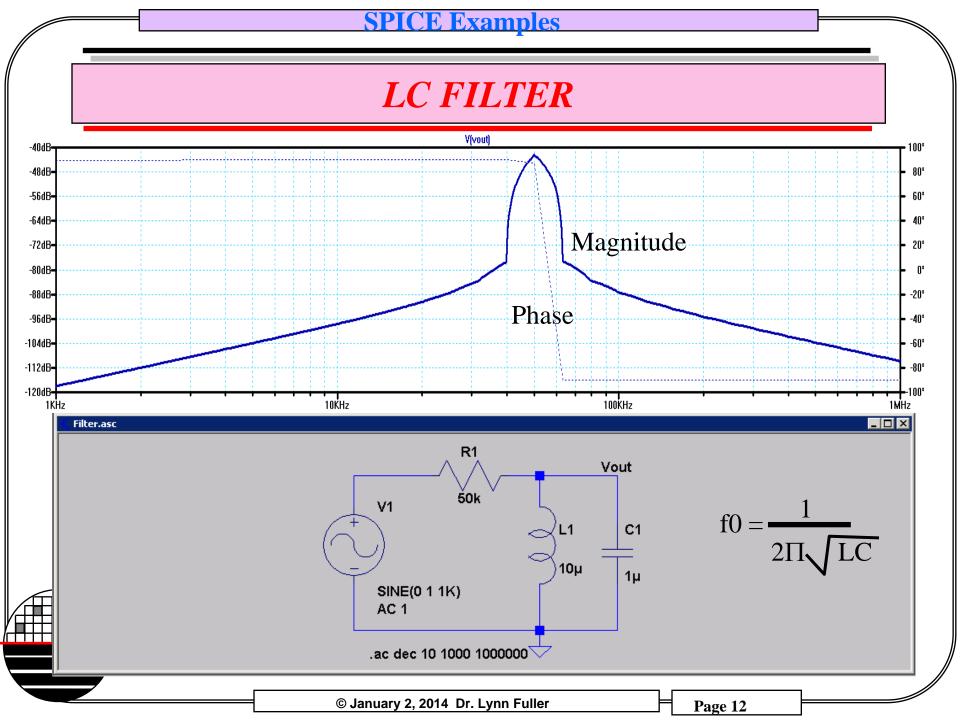

# **RC DIVIDER CIRCUIT**

Calculate VC as the voltage V1 is swept from 0 to 3 volts

Change the V1 to a 3 volt pulse function and plot VC versus time.

Change the voltage V1 to an AC voltage source and plot VC versus frequency

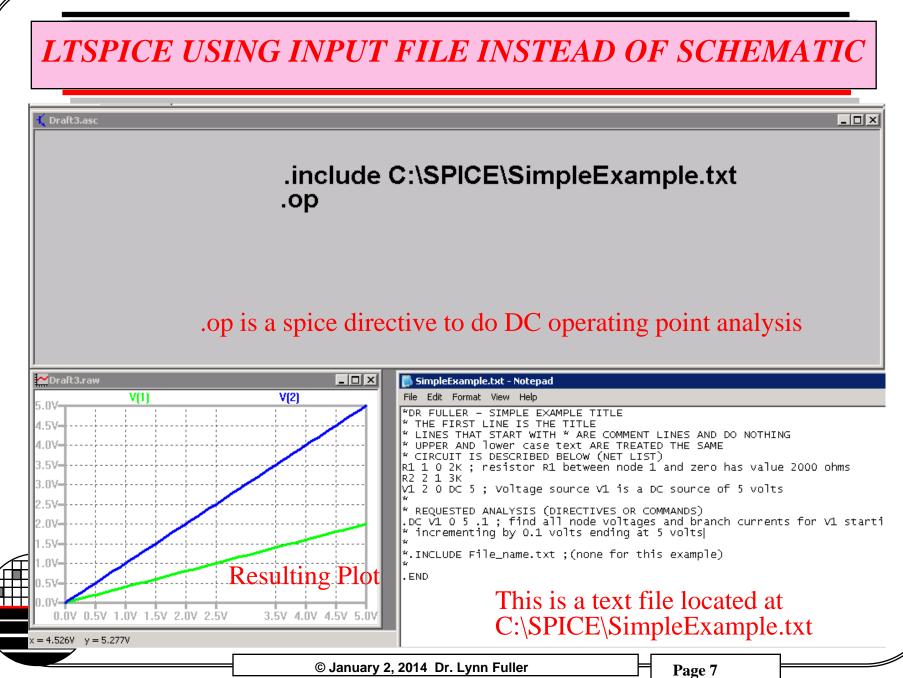

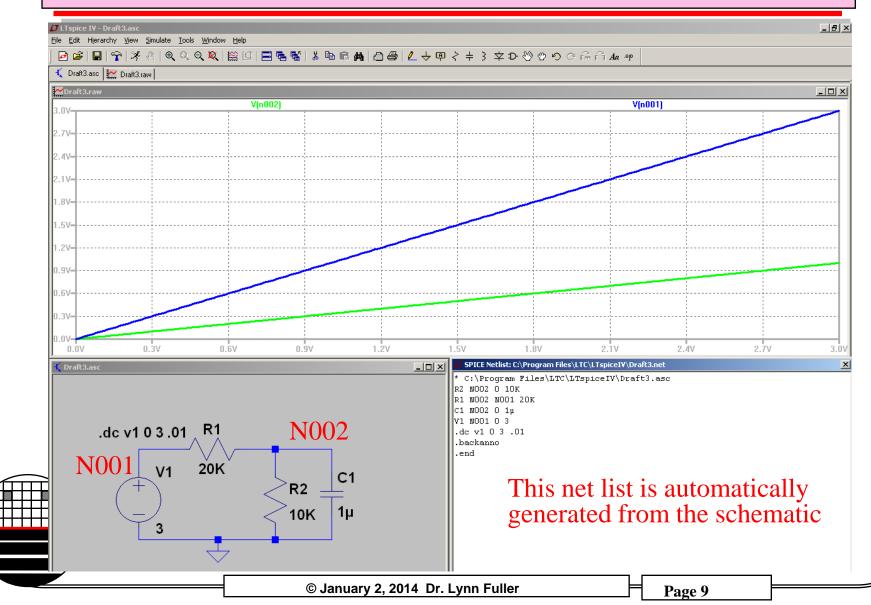

**DC SPICE ANALYSIS USING LTSPICE**

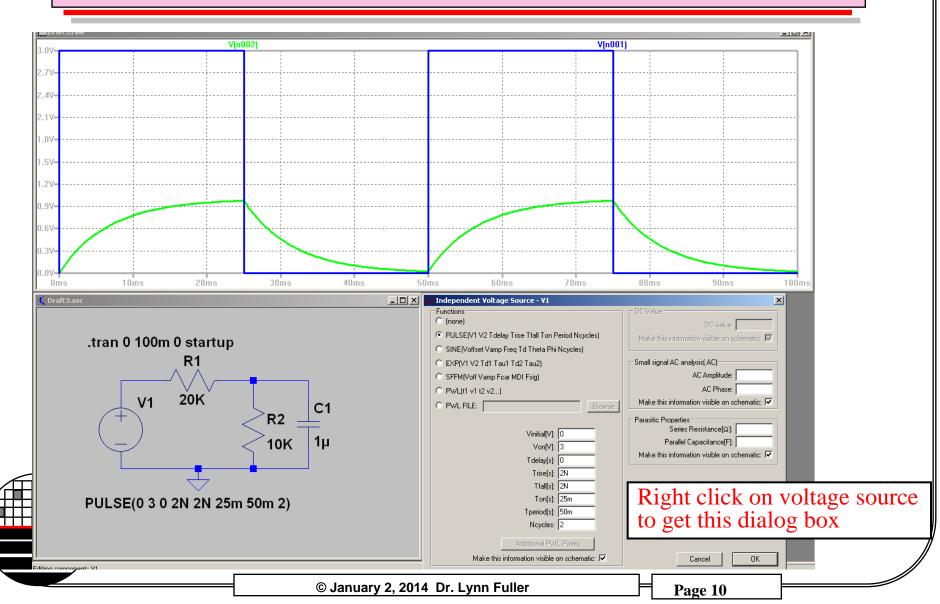

TRANSIENT ANALYSIS USING LTSPICE

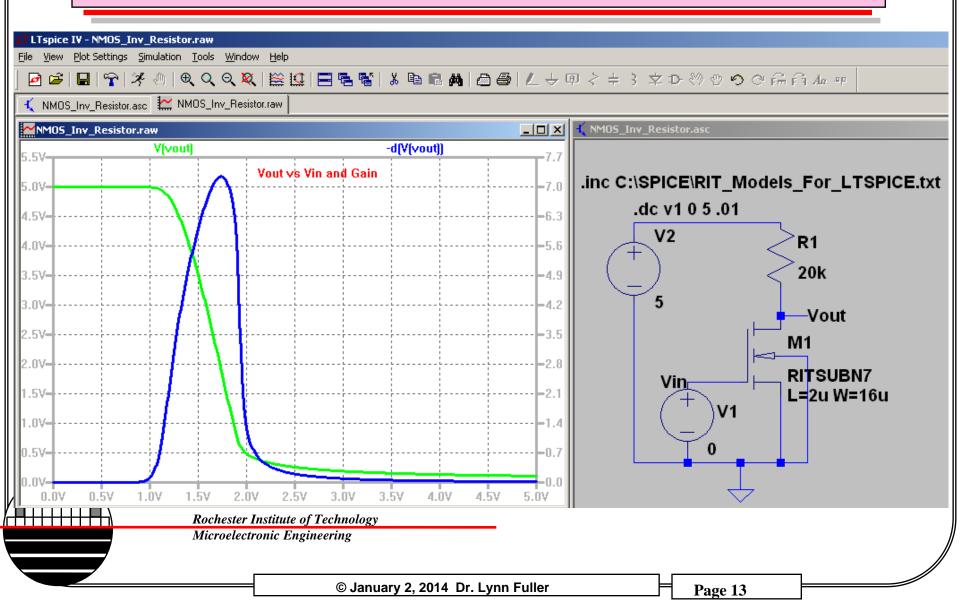

NMOS INVERTER WITH RESISTER LOAD

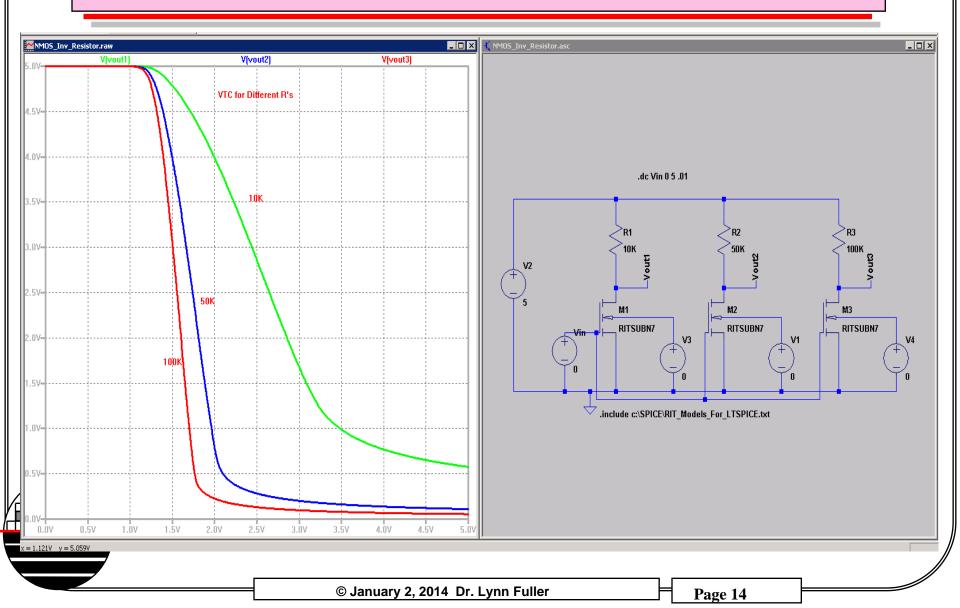

# **NMOS INVERTER RESISTIVE LOADS**

### **SPICE Examples NMOS INVERTER WITH NMOS LOAD** LTspice IV - NMOS\_Inv1.raw View Plot Settings Simulation Tools Window Help File 🧭 🎽 🔨 NMOS Inv1.asc 🔛 NMOS\_Inv1.raw MMO5\_Inv1.raw NMOS Inv1.asc - D X V(vout) -d(V(vout)) $3.6V_{2}$ L=16u W=4u Vout vs Vin and Voltage Gain 3.3V 6.0 M2 3.0V RITSUBN7 4.8-Vout Vin .4\ M1 2.1\ 3.6**V1** V2 3.0 1.8V RITSUBN7 L=2u W=16u .5V .2V 5 0 0.9V 0.61 0.6 .INC C:\SPICE\RIT Models For LTSPICE.txt 0.3\ 0.0 .dc v2 0 5 .1 1.014 -0.6 2.5V 3.0V 3.5V 4.0V 4.5V 5.0V 0.5V 1.0V 1.5V 2.0V V0.0 **Rochester Institute of Technology** Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

© January 2, 2014 Dr. Lynn Fuller

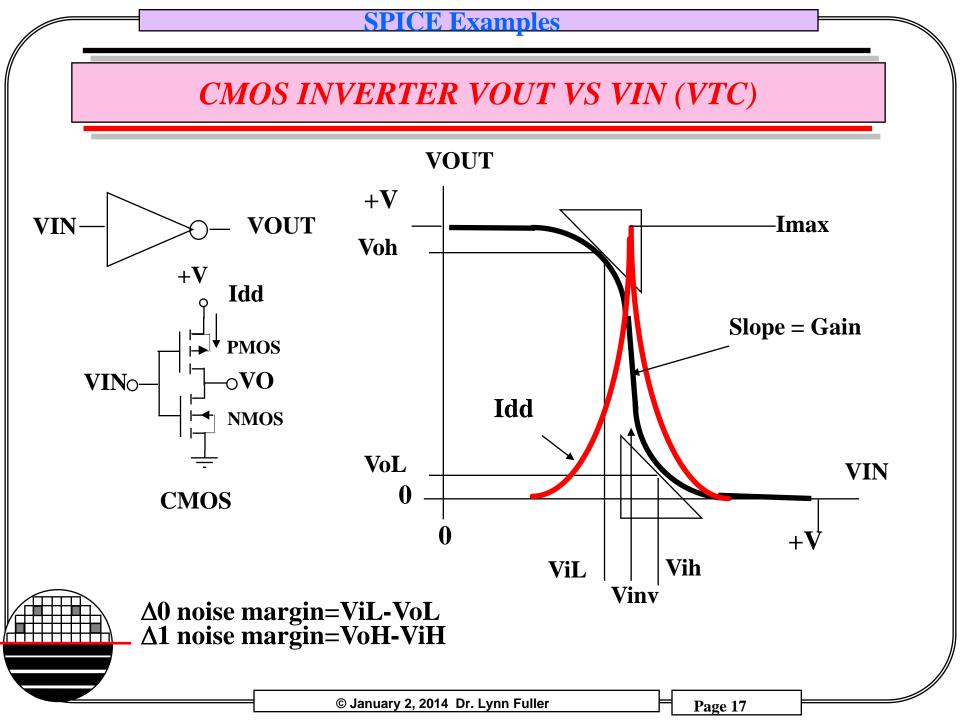

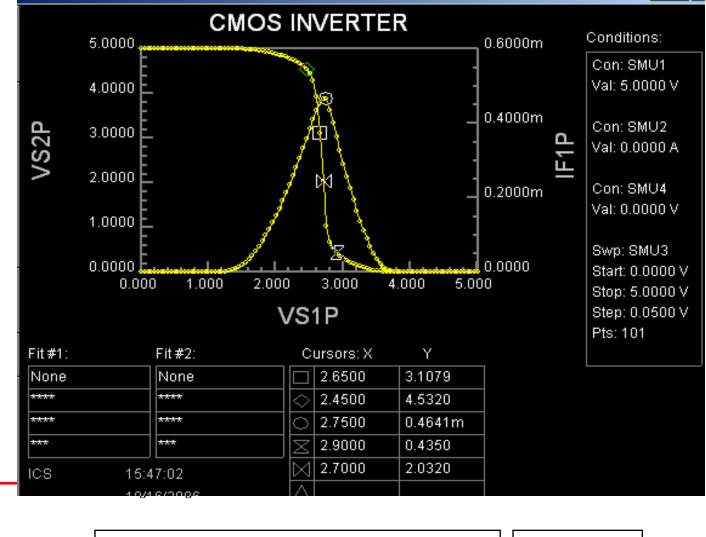

# MEASURED CMOS INVERTER VOUT & I VS VIN

© January 2, 2014 Dr. Lynn Fuller

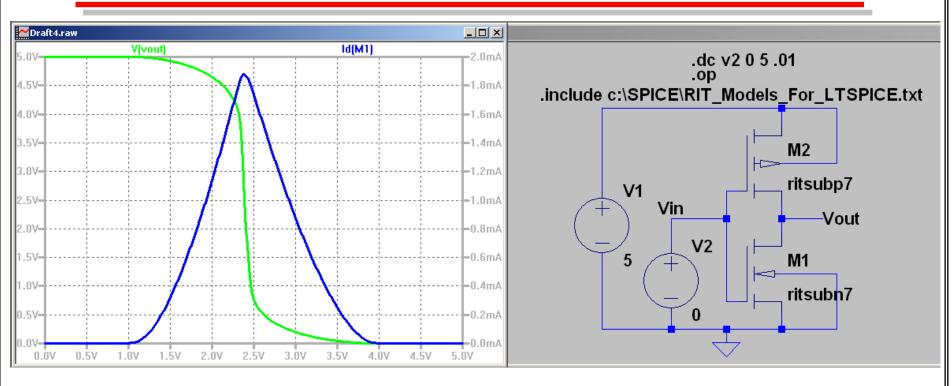

**DC SIMULATION OF INVERTER VOUT & I VS VIN**

What happens to the voltage transfer curve (VTC) and noise margins when one of the threshold voltages is changed by 0.3 volts? What happens when width of transistors is changed.

**Rochester Institute of Technology**

Microelectronic Engineering

# SIMPLE AND ADVANCED SPICE MODEL

```

* From Electronics II EEEE482 FOR ~100nm Technology

.model EECMOSN NMOS (LEVEL=8

+VERSION=3.1 CAPMOD=2 MOBMOD=1

+TOX=5E-9 XJ=1.84E-7 NCH=1E17 NSUB=5E16 XT=5E-8

+VTH0=0.4 U0= 200 WINT=1E-8 LINT=1E-8

+NGATE=5E20 RSH=1000 JS=3.23E-8 JSW=3.23E-8 CJ=6.8E-4 MJ=0.5 PB=0.95

+CJSW=1.26E-10 MJSW=0.5 PBSW=0.95 PCLM=5

+CGSO=3.4E-10 CGDO=3.4E-10 CGBO=5.75E-10)

* From Electronics II EEEE482 FOR ~100nm Technology

.model EECMOSP PMOS (LEVEL=8

+TOX=5E-9 XJ=0.05E-6 NCH=1E17 NSUB=5E16 XT=5E-8

+VTH0=-0.4 U0= 100 WINT=1E-8 LINT=1E-8

+NGATE=5E20 RSH=1000 JS=3.51E-8 JSW=3.51E-8 CJ=5.28E-4 MJ=0.5 PB=0.94

+CJSW=1.19E-10 MJSW=0.5 PBSW=0.94 PCLM=5

+CGSO=4.5E-10 CGDO=4.5E-10 CGBO=5.75E-10)

*

* From Electronics II EEEE482 SIMPLE MODEL

.model EENMOS

NMOS (VTO=0.4 KP=432E-6 GAMMA=0.2 PHI=.88)

* From Electronics II EEEE482 SIMPLE MODEL

.model EEPMOS

PMOS (VTO=-0.4 KP=122E-6 GAMMA=0.2 PHI=.88)

```

© January 2, 2014 Dr. Lynn Fuller

**CMOS INVERTER WITH LEVEL 1 SPICE MODEL**

| CMOS_Inverter_100nm.asc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |  | Onm.raw | r_10 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|---------|------|

| Id[M1]<br>91µA<br>0dµA<br>77µA<br>70µA<br>63µA<br>63µA<br>63µA<br>63µA<br>42µA<br>22µA<br>22µA<br>21µA<br>14µA<br>77µA<br>77µA<br>70µA<br>63µA<br>63µA<br>63µA<br>63µA<br>63µA<br>70µA<br>63µA<br>70µA<br>63µA<br>70µA<br>63µA<br>70µA<br>63µA<br>70µA<br>63µA<br>70µA<br>63µA<br>70µA<br>63µA<br>70µA<br>70µA<br>63µA<br>70µA<br>70µA<br>63µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µA<br>70µ | 91µ<br> |  |         |      |

**CMOS INVERTER WITH LEVEL 8 SPICE MODEL**

J LTspice IV - CMOS Inverter 100nm.asc \_ 8 × Eile Edit Hierarchy View Simulate Tools Window Help ☞☞|■|〒|茅||●|●、ヘヘベ||※□||■●●||▲●●||▲●●||▲→甲>+3 文ひ ⑳ ♡ ♡ ♡ ☆☆☆ 🐛 CMOS\_Inverter\_100nm.asc 🗽 CMOS\_Inverter\_100nm.raw - 🗆 × CMOS\_Inverter\_100nm.asc \_ 🗆 🗡 CM05\_Inverter\_100nm.raw V(vout) Id(M1) 91µ/ .dc v2 0 1.5 .001 .op .include c:\SPICE\RIT\_Models\_For\_LTSPICE.txt L=0.1u W=.7u M2 H>> **EECMOSP V1** Vin -Vout **V2** 1.5 M1 +EECMOSN L=0.1u W=.4u 0 /H -14µA 0.4V 0.6V 0.87 0.0V 0.2V 1.07 1.2V 1.4V © January 2, 2014 Dr. Lynn Fuller Page 22

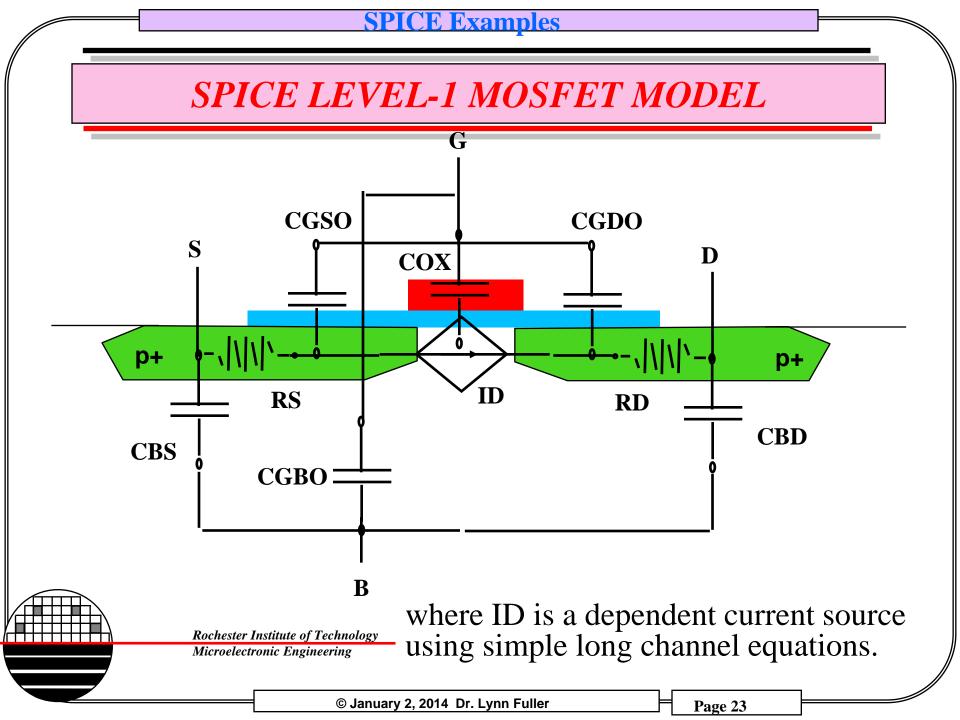

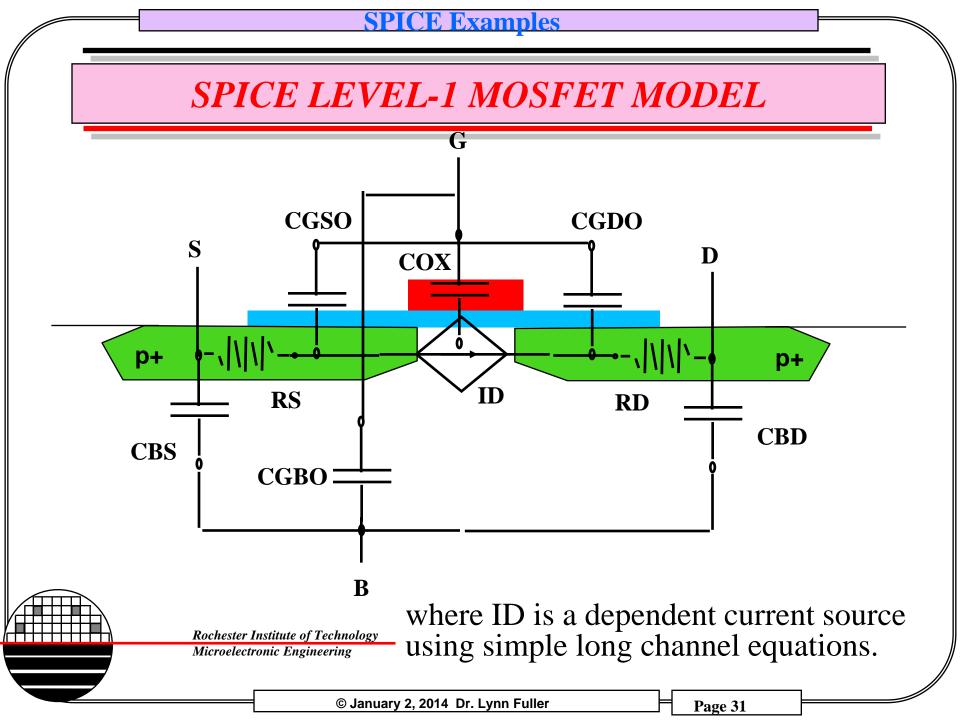

# **AC MODEL FOR MOSFETS**

The SPICE model parameters that effect the AC response of a MOSFET are the resistance and capacitance parameters shown here:

| RS,RS     | Source/Drain Series Resistance, ohms                  |

|-----------|-------------------------------------------------------|

| RSH       | Sheet Resistance of Drain/Source, ohms                |

| CGSO,CGDO | Zero Bias Gate-Source/Drain Capacitance, F/m of width |

| CGBO      | Zero Bias Gate-Substrate Capacitance, F/m of length   |

| CJ        | DS Bottom Junction Capacitance, F/m2                  |

| CJSW      | DS Side Wall Junction Capacitance, F/m of perimeter   |

| MJ        | Junction Grading Coefficient, 0.5                     |

| MJSW      | Side Wall Grading Coefficient, 0.5                    |

These are combined with the transistors properties to obtain the internal resistance and capacitance values for each transistor.

| L, W    | Length and Width                     |

|---------|--------------------------------------|

| AS,AD   | Area of the Source/Drain             |

| PS,PD   | Perimeter of the Source/Drain        |

| NRS,NRD | Number of squares Contact to Channel |

| -       | 1                                    |

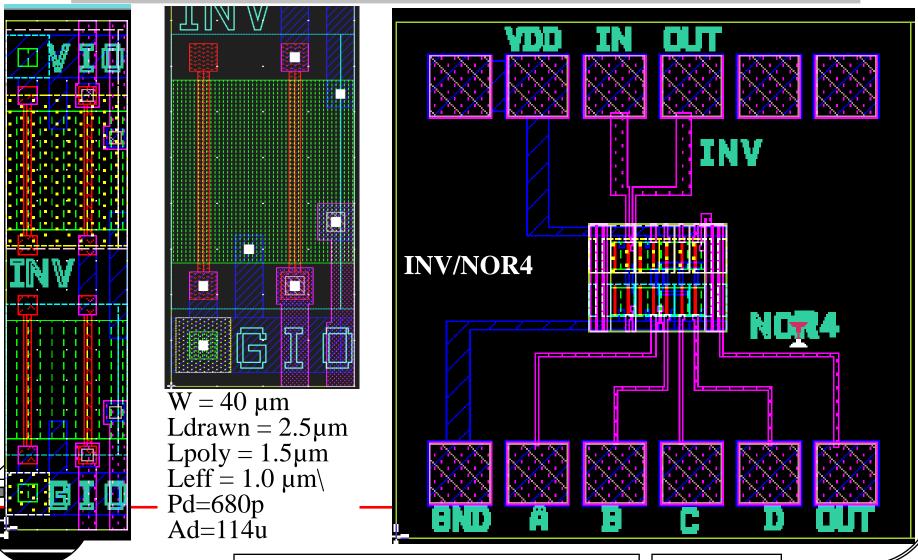

# **INVERTER LAYOUT**

© January 2, 2014 Dr. Lynn Fuller

# FIND DIMENSIONS OF THE TRANSISTORS

| Inverter |                  |                  |  |

|----------|------------------|------------------|--|

|          | NMOS             | PMOS             |  |

| L        | 1.5u             | 1.5u             |  |

| W        | 40u              | 40u              |  |

| AD       | 17ux40u=680p     | 17ux40u=680p     |  |

| AS       | 17ux40u=680p     | 17ux40u=680p     |  |

| PD       | 2x(17u+40u)=114u | 2x(17u+40u)=114u |  |

| PS       | 2x(17u+40u)=114u | 2x(17u+40u)=114u |  |

|          |                  |                  |  |

|          |                  |                  |  |

Right mouse click on each transistor and add these values to the properties.

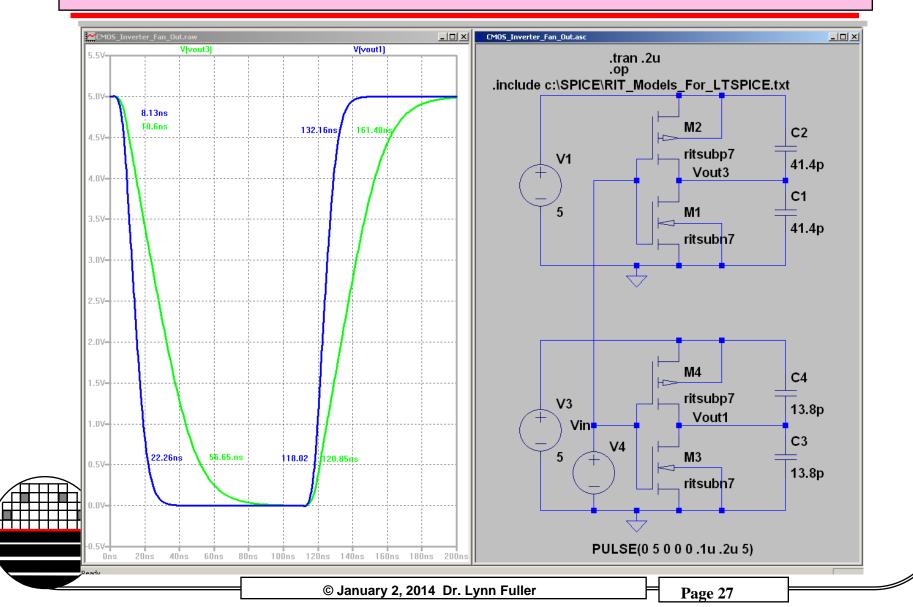

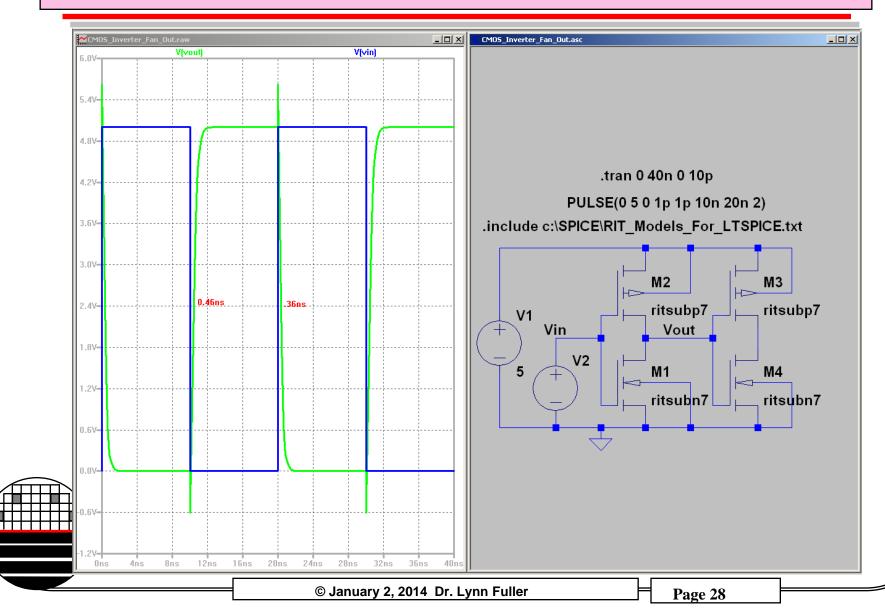

# **RISE TIME AND FALL TIME LTSPICE SIMULATION**

# SIMULATION OF GATE DELAY IN SINGLE INVERTER

<u>SPICE Examples</u>

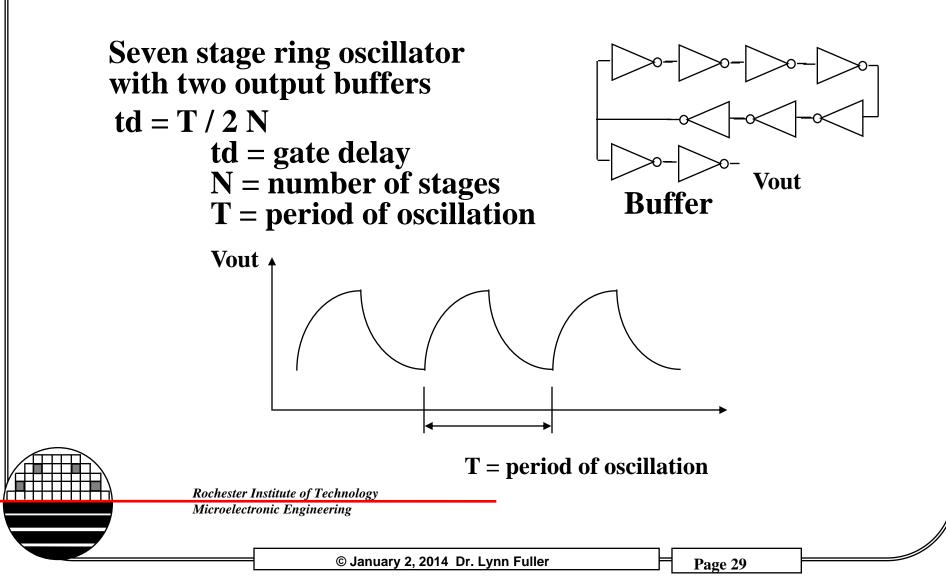

# **RING OSCILLATOR, td, THEORY**

# **MEASURED RING OSCILLATOR OUTPUT**

CH1 500 MV" A 20ns -62.5 MV? VERT

104.80ns

td = 104.8 ns / 2(73) = 0.718 ns

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

# **AC MODEL FOR MOSFETS**

The SPICE model parameters that effect the AC response of a MOSFET are the resistance and capacitance parameters shown here:

| RS,RS     | Source/Drain Series Resistance, ohms                  |

|-----------|-------------------------------------------------------|

| RSH       | Sheet Resistance of Drain/Source, ohms                |

| CGSO,CGDO | Zero Bias Gate-Source/Drain Capacitance, F/m of width |

| CGBO      | Zero Bias Gate-Substrate Capacitance, F/m of length   |

| CJ        | DS Bottom Junction Capacitance, F/m2                  |

| CJSW      | DS Side Wall Junction Capacitance, F/m of perimeter   |

| MJ        | Junction Grading Coefficient, 0.5                     |

| MJSW      | Side Wall Grading Coefficient, 0.5                    |

These are combined with the transistors properties to obtain the internal resistance and capacitance values for each transistor.

| L, W    | Length and Width                     |

|---------|--------------------------------------|

| AS,AD   | Area of the Source/Drain             |

| _ PS,PD | Perimeter of the Source/Drain        |

| NRS,NRD | Number of squares Contact to Channel |

|         | *                                    |

**MOSFETS IN THE INVERTER OF 73 RING OSCILLATOR**

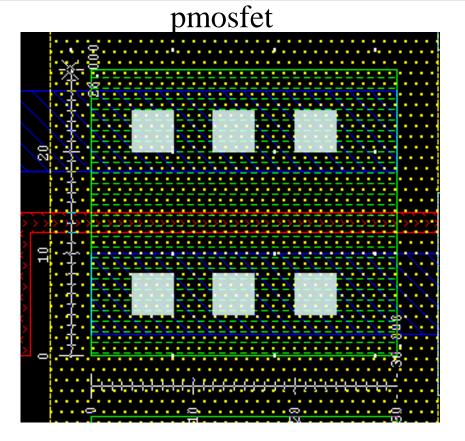

# nmosfet

# 73 Stage Ring Oscillator

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

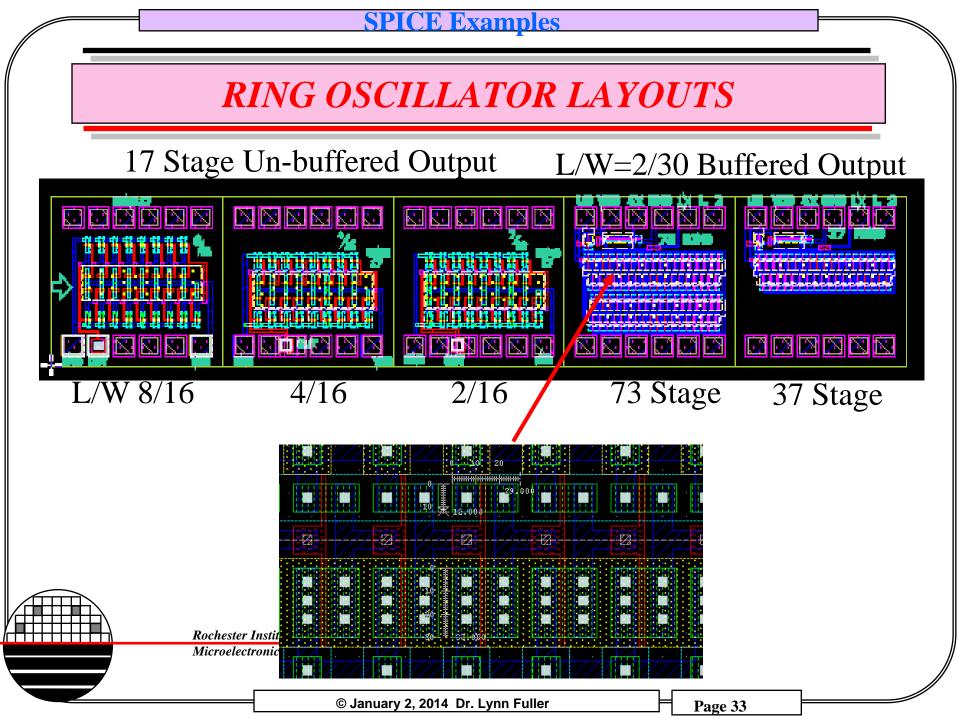

# FIND DIMENSIONS OF THE TRANSISTORS

|     | NMOS            | PMOS            | 73 Stage |

|-----|-----------------|-----------------|----------|

| L   | 2u              | 2u              |          |

| W   | 12u             | 30u             |          |

| AD  | 12ux12u=144p    | 12ux30u=360p    |          |

| AS  | 12ux12u=144p    | 12ux30u=360p    |          |

| PD  | 2x(12u+12u)=48u | 2x(12u+30u)=84u |          |

| PS  | 2x(12u+12u)=48u | 2x(12u+30u)=84u |          |

| NRS | 1               | 0.3             |          |

| NRD | 1               | 0.3             |          |

Right mouse click on each transistor and add these values to the properties.

# *LEVEL* = 7

\*2-15-2009

.MODEL RITSUBN7 NMOS (LEVEL=7

+VERSION=3.1 CAPMOD=2 MOBMOD=1

+TOX=1.5E-8 XJ=1.84E-7 NCH=1.45E17 NSUB=5.33E16 XT=8.66E-8 NSS=3E11

+VTH0=1.0 U0= 600 WINT=2.0E-7 LINT=1E-7

+NGATE=5E20 RSH=50 JS=3.23E-8 JSW=3.23E-8 CJ=6.8E-4 MJ=0.5 PB=0.95

+CJSW=1.26E-10 MJSW=0.5 PBSW=0.95 PCLM=5

+CGSO=3.4E-10 CGDO=3.4E-10 CGBO=5.75E-10)

\*

\*2-17-2009

.MODEL RITSUBP7 PMOS (LEVEL=7 +VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=2.26E-7 NCH=7.12E16 NSUB=3.16E16 XT=8.66E-8 NSS=3E11 PCLM=5 +VTH0=-1.0 U0= 376.72 WINT=2.0E-7 LINT=2.26E-7 NGATE=5E20 +RSH=50 JS=3.51E-8 JSW=3.51E-8 CJ=5.28E-4 MJ=0.5 PB=0.94 +CJSW=1.19E-10 MJSW=0.5 PBSW=0.94 +CGSO=4.5E-10 CGDO=4.5E-10 CGBO=5.75E-10)

**Rochester Institute of Technology**

Microelectronic Engineering

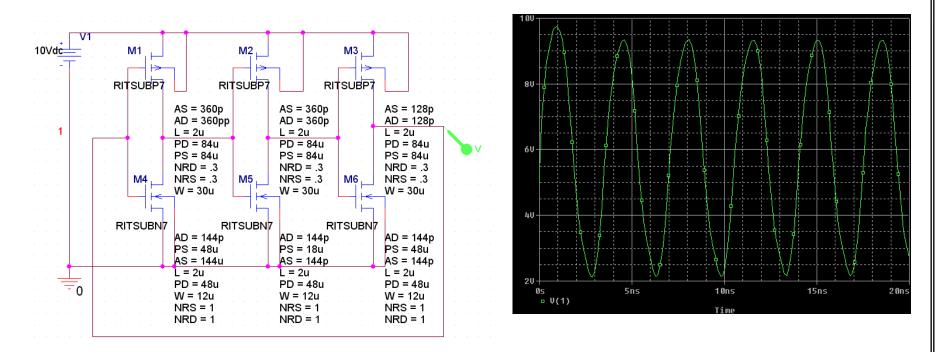

SIMULATED OUTPUT AT 10 VOLTS

Three Stage Ring Oscillator with Transistor Parameters for 73 Stage Ring Oscillator and Supply of 10 volts

Rochester Institute of Technology

Microelectronic Engineering

td = T / 2N = 3.5nsec / 2 / 3 td = 0.583 nsec

© January 2, 2014 Dr. Lynn Fuller

Page 37

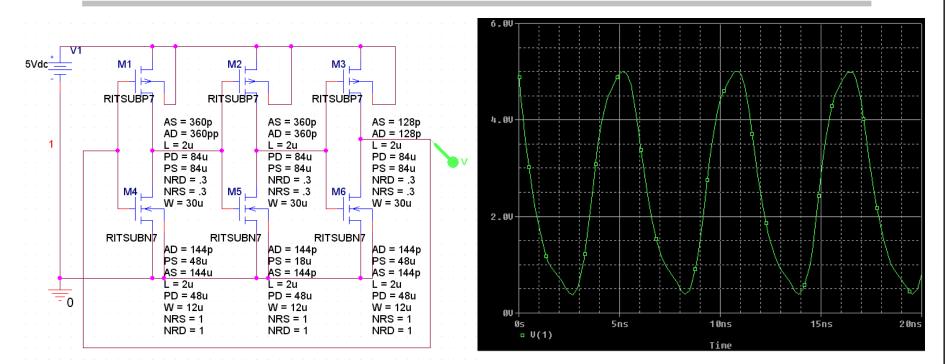

# **SIMULATED OUTPUT AT 5 VOLTS**

**SPICE Examples**

Three Stage Ring Oscillator with Transistor Parameters for 73 Stage Ring Oscillator and Supply of 5 volts

td = T / 2N = 5.5nsec / 2 / 3td = 0.92 nsec © January 2, 2014 Dr. Lynn Fuller Page 38

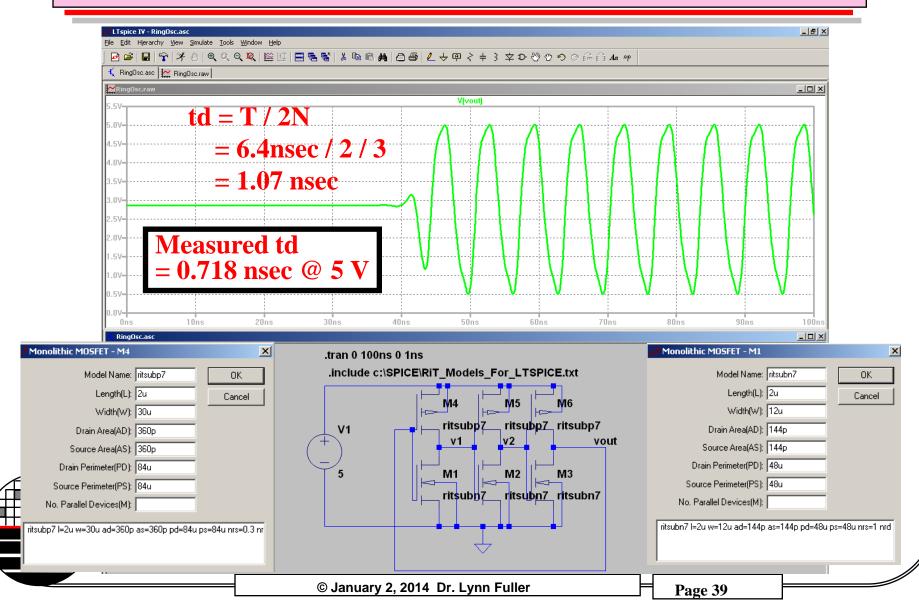

# **RING OSCILLATOR USING LTSPICE**

# **CONCLUSION**

Since the measured and the simulated gate delays, td are close to correct, then the SPICE model must be close to correct. The inverter gate delay depends on the values of the internal capacitors and resistances of the transistor.

Specifically: RS, RS, RSH CGSO, CGDO, CGBO CJ, CJSW

| These are c | ombined with the transistors         |

|-------------|--------------------------------------|

| L, W        | Length and Width                     |

| AS,AD       | Area of the Source/Drain             |

| PS,PD       | Perimeter of the Source/Drain        |

| f NRS,NRD   | Number of squares Contact to Channel |

|             | Rochester Institute of Technology    |

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

Page 40

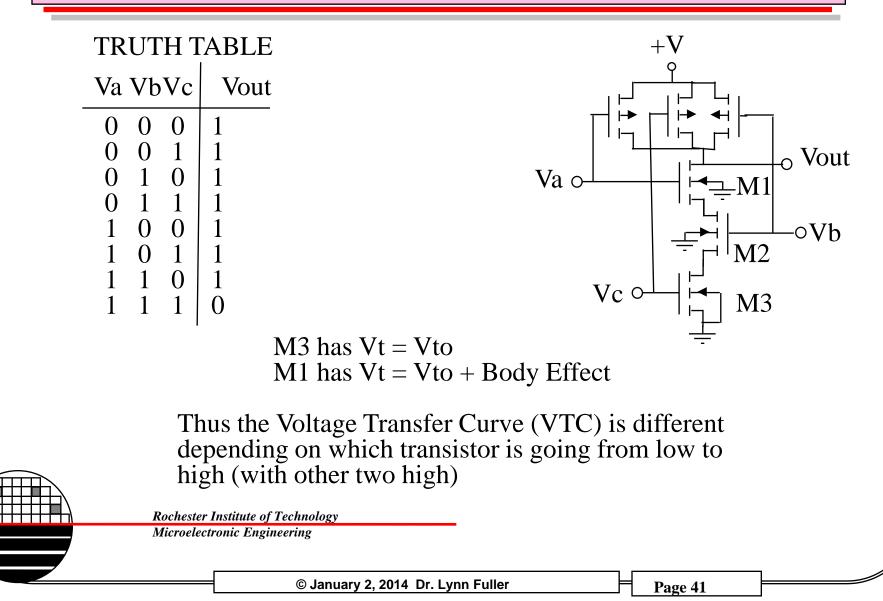

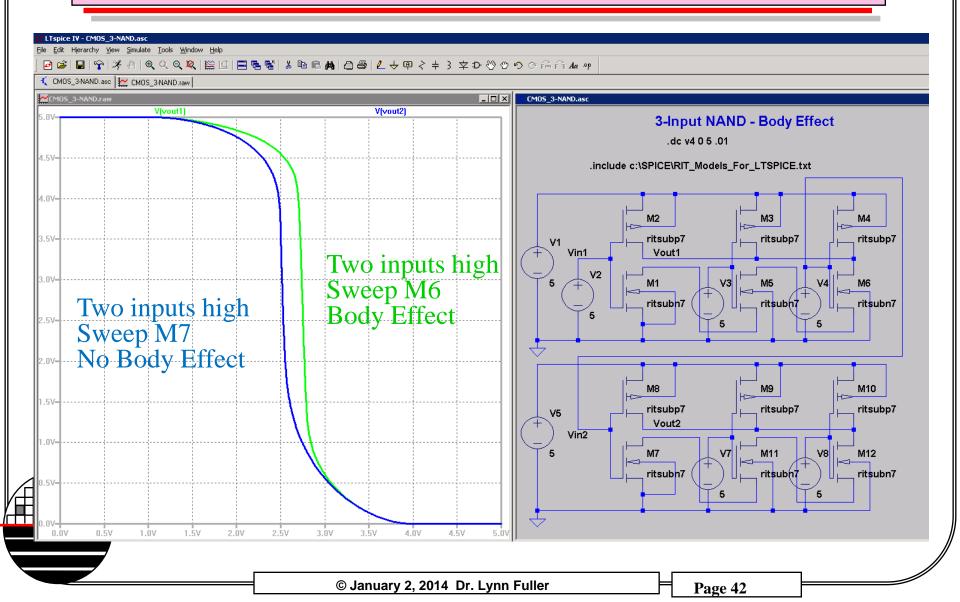

## **VTC FOR THREE INPUT NAND GATE**

## **3-INPUT NAND- BODY EFFECT**

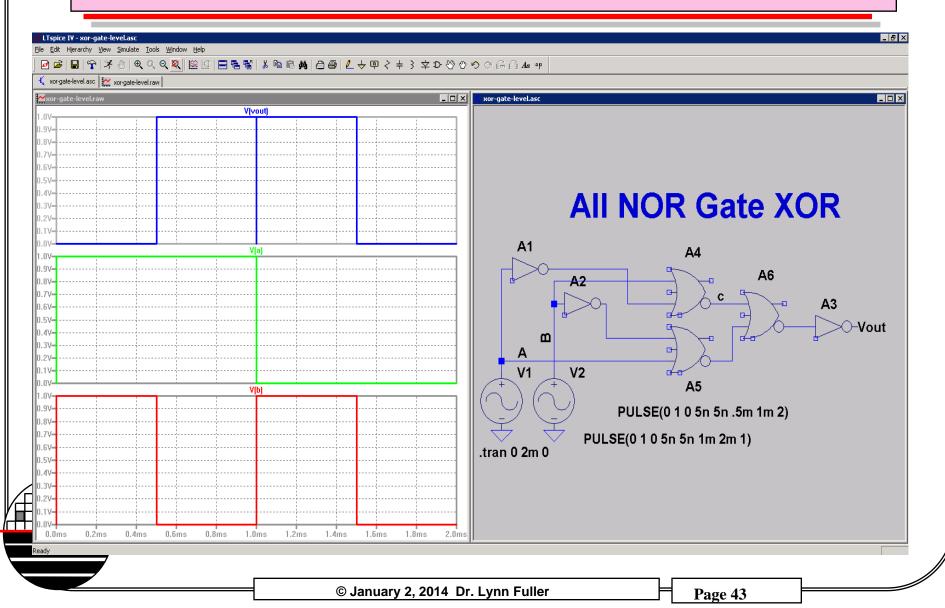

GATE LEVEL SIMULATION OF XOR – ALL/NOR

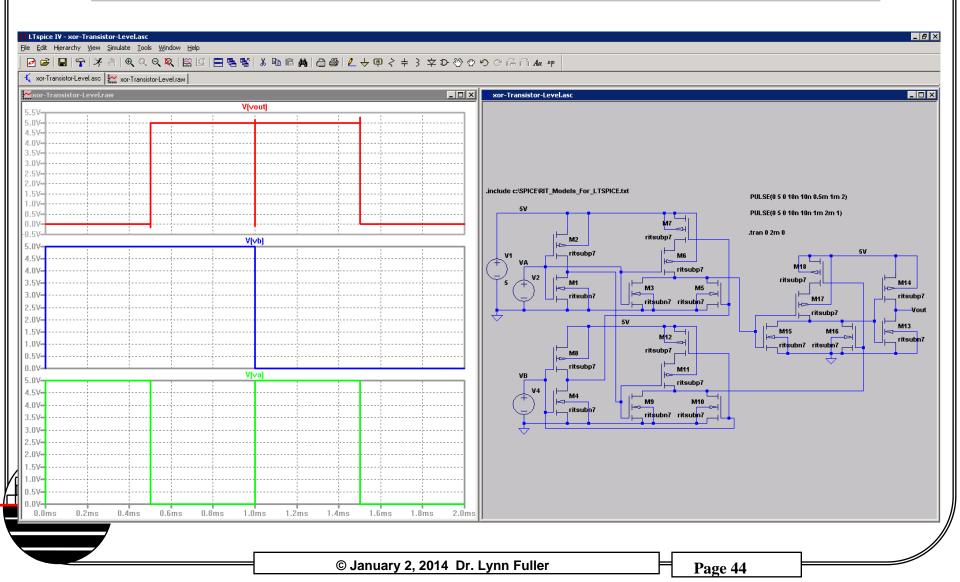

**TRANSISTOR LEVEL SIMULATION OF XOR – ALL/NOR**

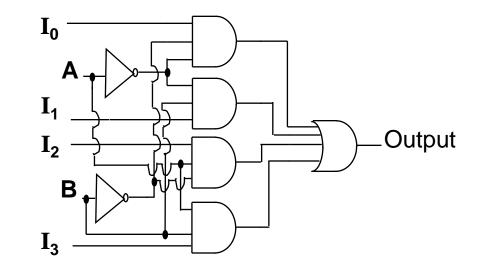

# 4 TO 1 MULTIPLEXER

Digital signals A and B control which of the four inputs is directed to the output

A

B

Out

0

0

I0

0

1

I1

1

0

I2

1

1

I3

Rochester Institute of Technology

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

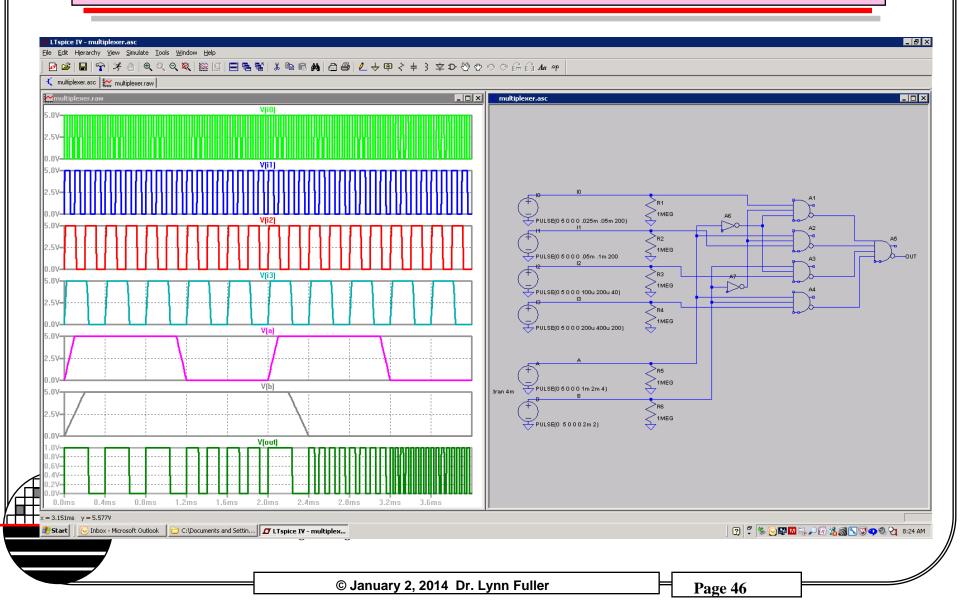

**4 TO 1 MUX - GATE LEVEL SIMULATION**

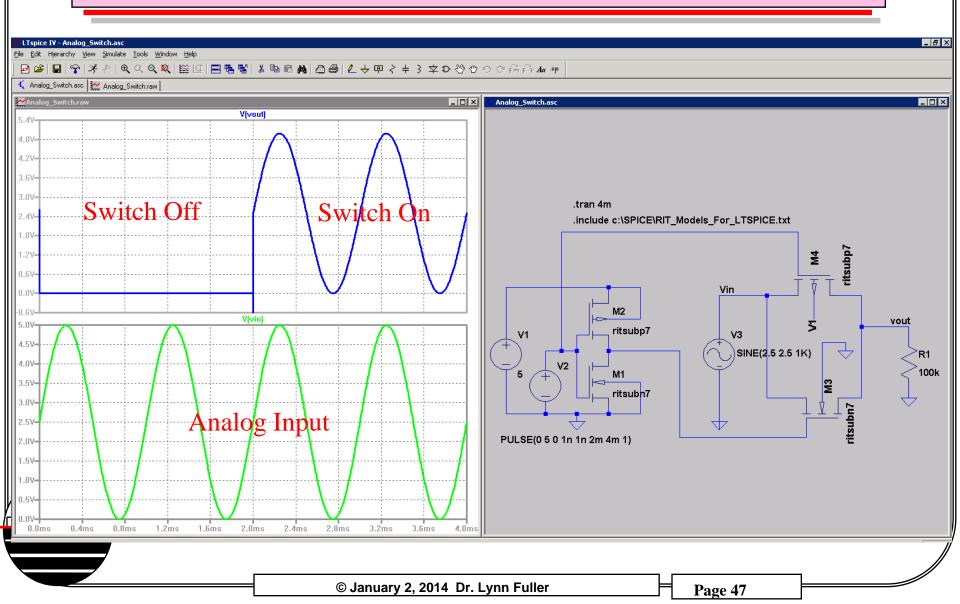

# **ANALOG SWITCH**

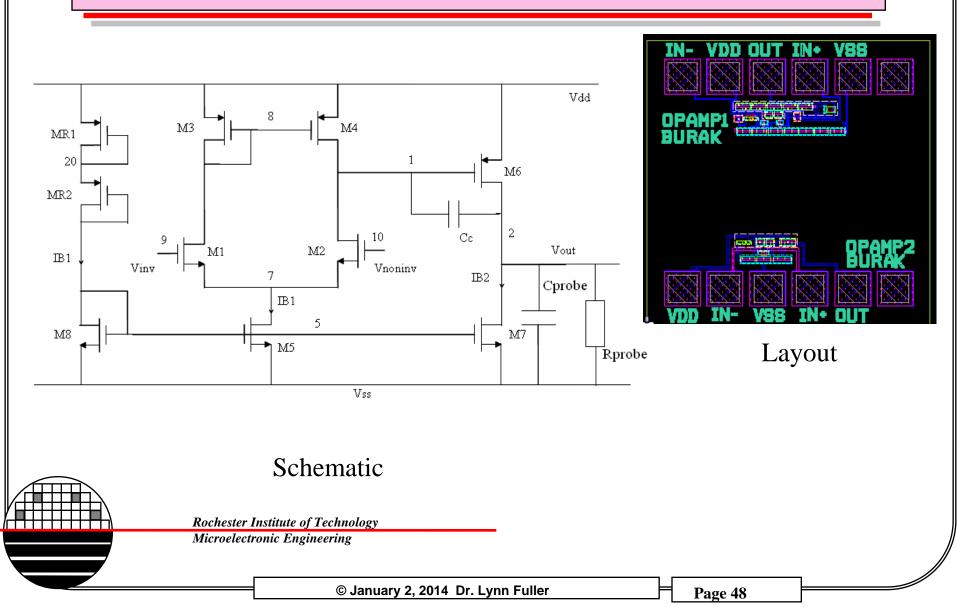

**BASIC TWO STAGE OPERATIONAL AMPLIFIER**

## SPICE ANALYSIS OF OP AMP

.incl rit\_sub\_param.txt m1 8 9 7 6 cmosn w=9u l=5u nrd=1 nrs=1 ad=45p pd=28u as=45p ps=28u m2 1 10 7 6 cmosn w=9u l=5u nrd=1 nrs=1 ad=45p pd=28u as=45p ps=28u m3 8 8 4 4 cmosp w=21u l=5u nrd=1 nrs=1 ad=102p pd=50u as=102p ps=50u m4 1 8 4 4 cmosp w=21u l=5u nrd=1 nrs=1 ad=102p pd=50u as=102p ps=50u m5 7 5 6 6 cmosn w=40u l=5u nrd=1 nrs=1 ad=205p pd=90u as=205p ps=90u m6 2 1 4 4 cmosp w=190u l=5u nrd=1 nrs=1 ad=950p pd=400u as=950p ps=400u m7 2 5 6 6 cmosn w=190u l=5u nrd=1 nrs=1 ad=950p pd=400u as=950p ps=400u m8 5 5 6 6 cmosn w=40u l=5u nrd=1 nrs=1 ad=205p pd=90u as=205p ps=90u vdd 4 0 3 vss 6 0 - 3 cprobe 2 0 30p Rprobe 2 0 1 meg cc 1 2 0.6p mr1 20 20 4 4 cmosp w=6u l=10u nrd=1 nrs=1 ad=200p pd=60u as=200p ps=60u mr2 5 5 20 4 cmosp w=6u l=10u nrd=1 nrs=1 ad=200p pd=60u as=200p ps=60u

BASIC TWO STAGE OP AMP - LOADING

| Amp_Two_Stage.asc 🔛 CMOS_Op |    |             |     |     |     | _   |      | CMO5_Op_Amp | Two Stage.asc                | _                  | _            |           | _              |          |         |                     | -        |

|-----------------------------|----|-------------|-----|-----|-----|-----|------|-------------|------------------------------|--------------------|--------------|-----------|----------------|----------|---------|---------------------|----------|

|                             |    | -d(V(vout)) |     |     |     |     |      |             |                              |                    |              |           |                |          |         |                     |          |

| <br>                        |    |             |     | ·   |     |     |      |             |                              |                    |              |           |                |          |         |                     |          |

| <br>                        |    |             |     |     |     |     |      | .i          | include c:\SPIC              | :E\RIT Mode        | els For LTSI | PICE.txt  |                |          |         |                     |          |

| <br>                        |    |             |     |     |     |     |      |             |                              | -<br>dc v2 5 -5 .0 |              |           |                | <b>;</b> |         |                     |          |

| <br>                        |    |             |     |     |     |     |      |             | - T T                        |                    | •            |           | ••             | -        | <b></b> |                     |          |

| <br>                        |    |             |     |     |     |     |      |             | M6                           | -1                 |              |           |                |          |         | 0                   |          |

| <br>                        |    |             |     |     |     |     |      |             | ritsubp7                     | => <br>            | M2<br>subp7  |           | M5<br>ritsubpi | ,        | HC> M1  | 9<br>subp7          |          |

| <br>                        |    |             |     |     |     |     |      | V1          | +                            |                    |              | ]         | nauh           |          |         | ասիլ                |          |

| <br>                        |    |             |     |     |     |     |      | (-)         |                              |                    |              |           |                |          |         |                     |          |

| <br>                        |    |             |     |     |     |     |      | 5           | V2 47                        |                    |              |           | +              |          |         |                     |          |

|                             |    | V(vout)     |     |     |     |     | - 11 |             | $\langle \gamma \rangle = 1$ |                    |              |           |                |          | •       | /out                |          |

|                             |    |             |     | _   |     |     | ⊐∥◄  | ₽           | ╵╵┙                          |                    | M1           | I         | M3             |          |         | R1                  | -        |

| <br>                        |    |             |     |     |     |     |      | ×3          | 0                            |                    | ritsub       | n7 ritsub | n7 L           |          |         | < <sup>&gt;1M</sup> | EG       |

| <br>                        |    |             |     |     |     |     |      | 5           |                              |                    |              |           |                |          | M2      | .0                  | <b>.</b> |

| <br>                        |    |             |     |     |     |     |      | Ŭ           |                              |                    | •            |           |                | <u> </u> |         | subn7               | $\sim$   |

| <br>                        |    |             |     |     |     |     |      |             | ل                            | M7                 | I IF         |           |                |          |         |                     |          |

| <br>                        |    |             |     |     |     |     |      |             | =>                           | viz<br>ritsubn7    | -            | ⊐ritsubn7 |                |          |         |                     |          |

| <br>                        |    |             |     |     |     |     |      |             |                              |                    |              |           |                |          |         |                     |          |

| <br>                        |    |             |     |     |     |     |      |             | •                            |                    |              |           | •              | 7        |         |                     |          |

|                             |    |             |     |     |     |     |      |             |                              |                    |              |           |                |          |         |                     |          |

|                             |    |             |     |     |     |     |      |             |                              |                    |              |           |                |          |         |                     |          |

| <br>                        |    | J           |     | ·   |     |     |      |             |                              |                    |              |           |                |          |         |                     |          |

| 4V 3V 2V                    | 1V | OV          | -1V | -2V | -3V | -4V |      |             |                              |                    |              |           |                |          |         |                     |          |

| 2.06V                       |    |             |     |     |     |     | P    |             |                              |                    |              |           |                |          |         |                     |          |

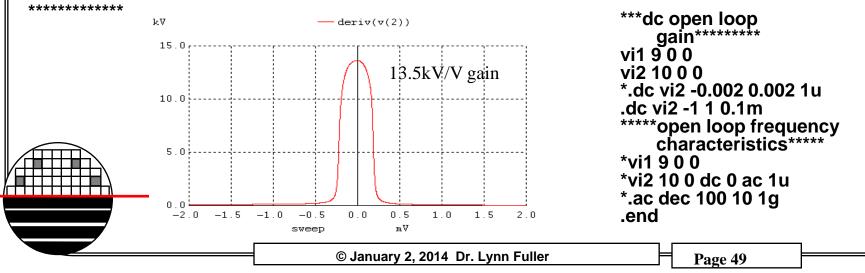

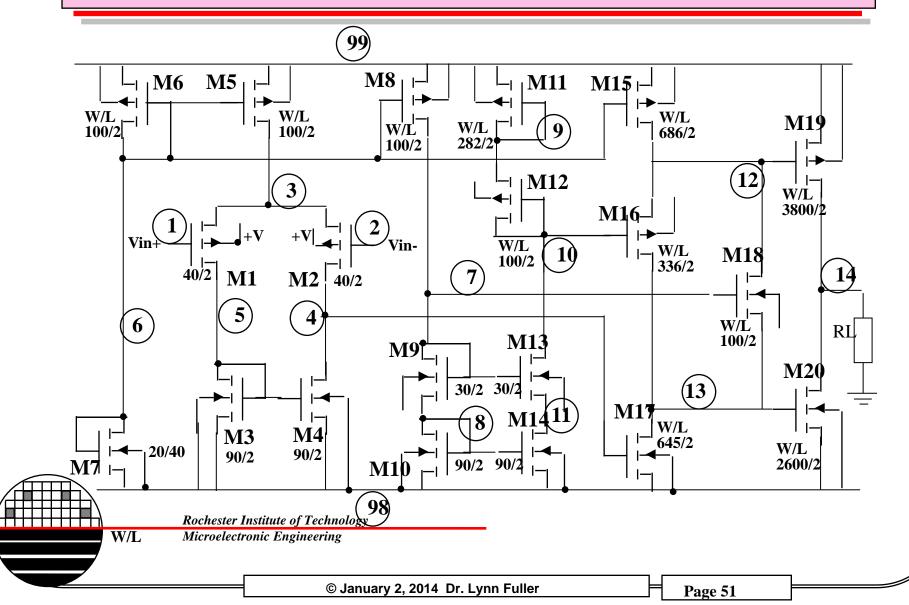

**RIT OP AMP WITH OUTPUT STAGE – W/L**

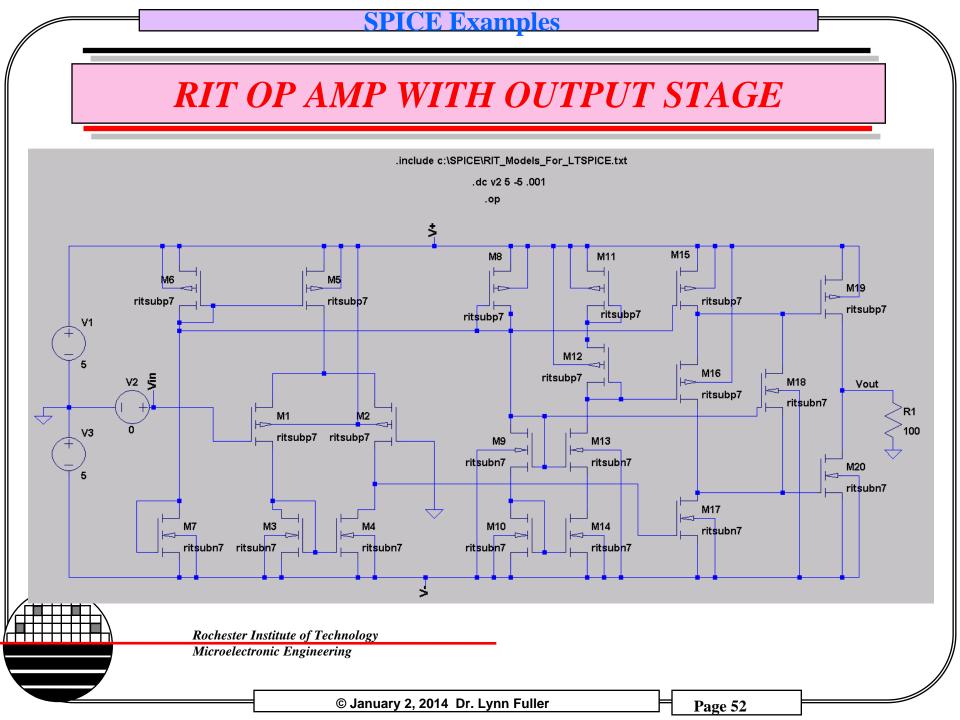

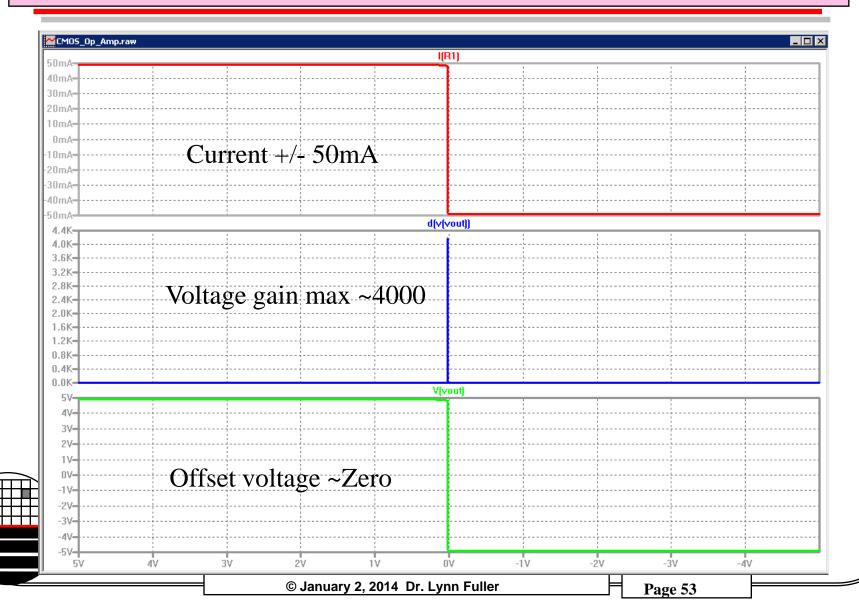

# **RIT OP AMP WITH OUTPUT STAGE – RL=100**

## **OTHER RESULTS**

Voltage Gain for 1 MEG Load Voltage Gain vs RL Output Resistance Gain versus Frequency (Gain Bandwidth Product) Lowest Supply Voltage Single Supply Operation Rail-to-Rail Operation Offset Voltage Effect of variation of Vt, temperture more

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

Page 54

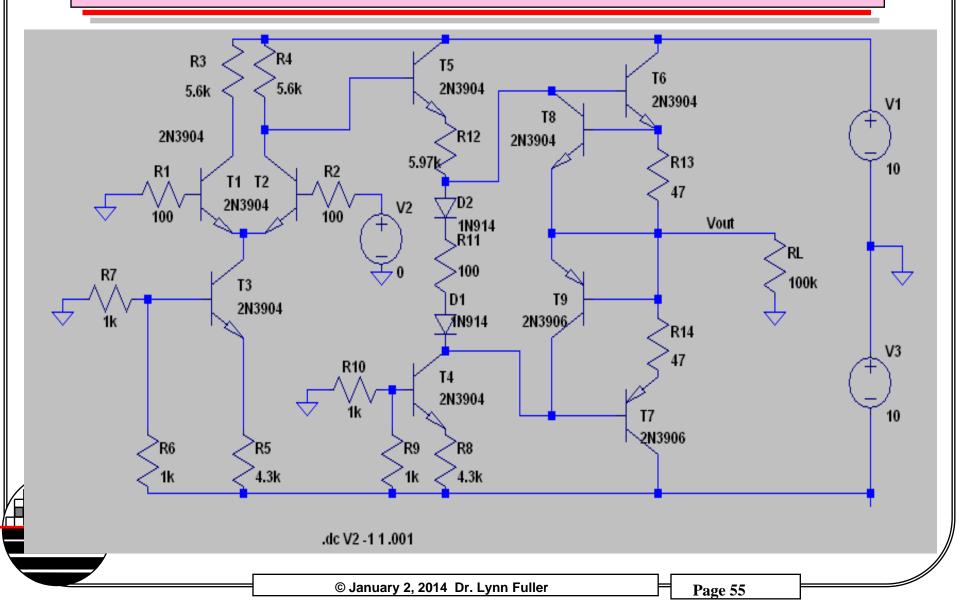

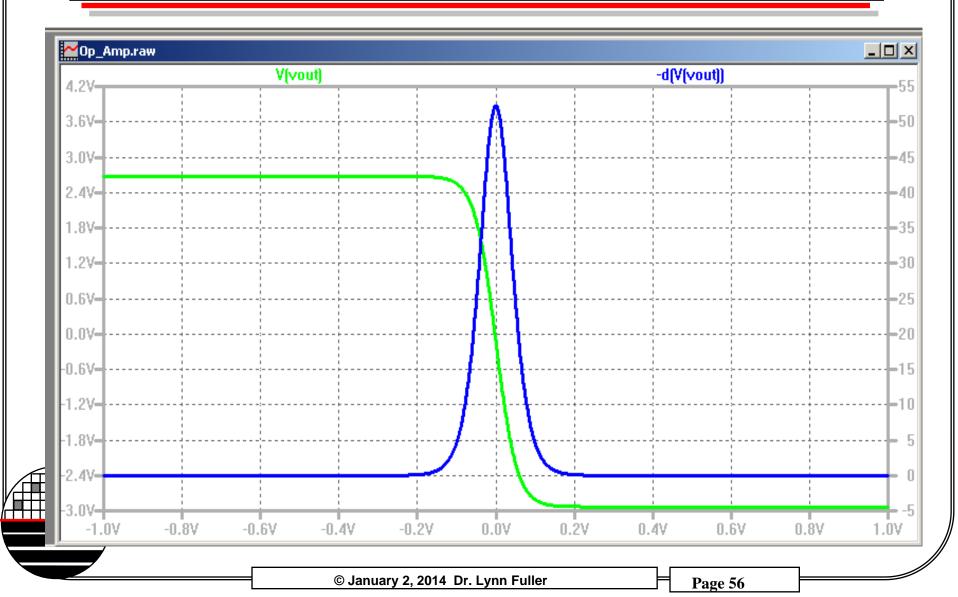

# SIMPLE BJT OP AMP

# SIMPLE BJT OP AMP

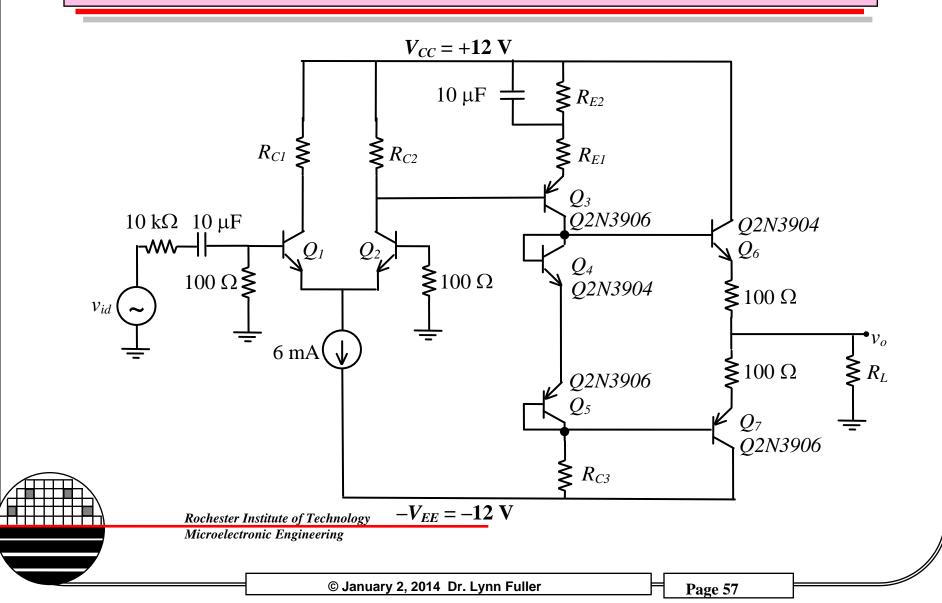

**BJT OP AMP USE IN ELECTRONICS LAB**

## **BJT OP AMP SPICE SIMULATION**

## Electronics II Lab Assignment

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

Page 58

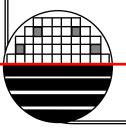

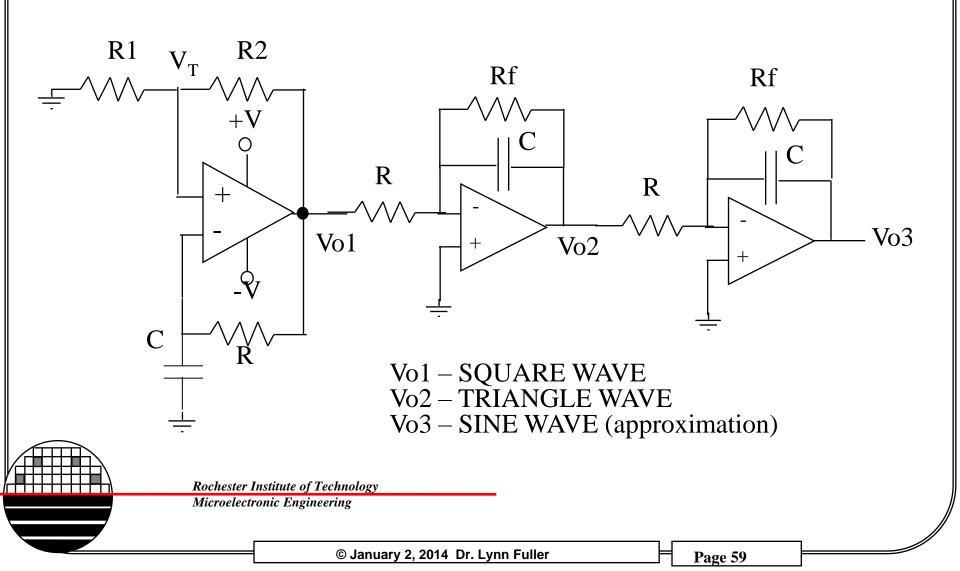

WAVEFORM GENERATOR

# WAVEFORM GENERATOR

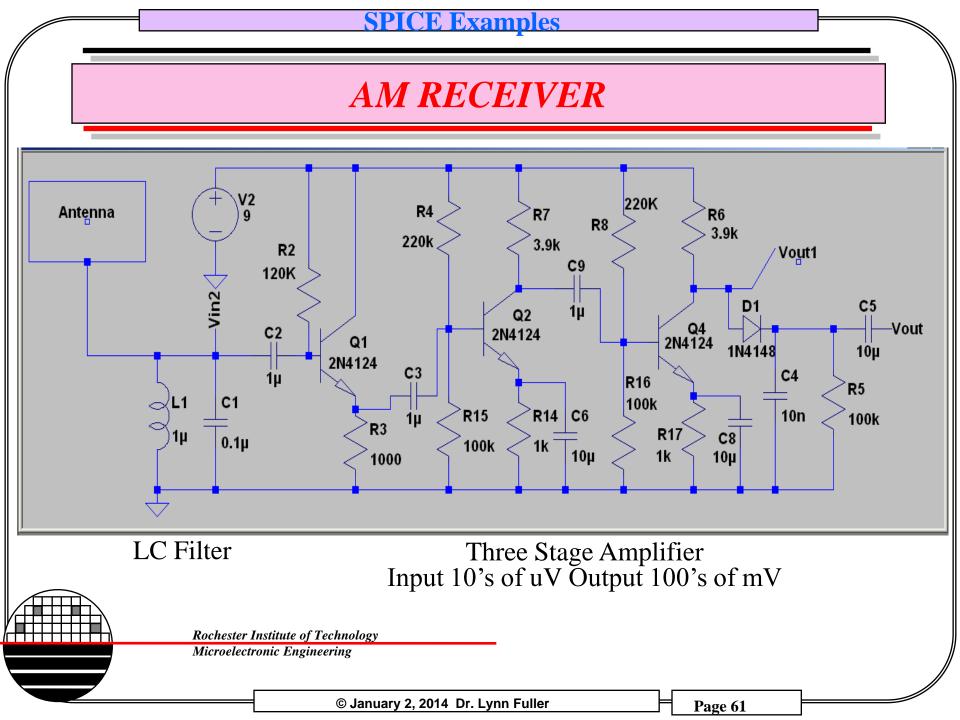

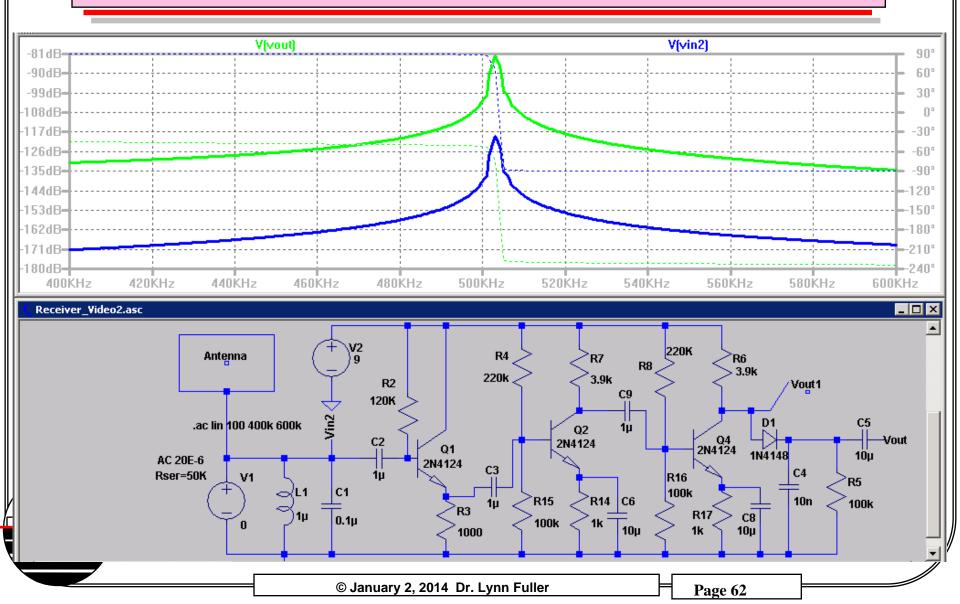

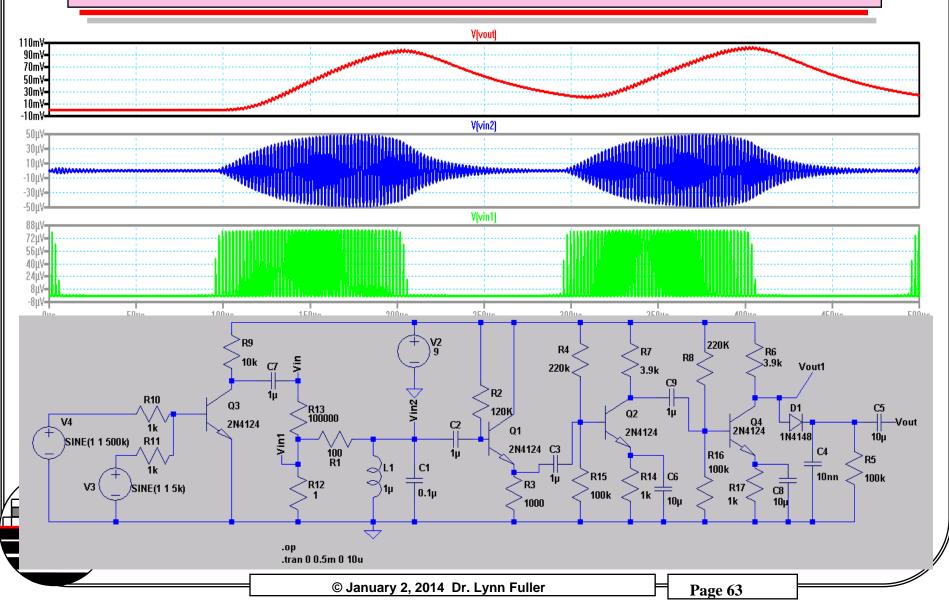

# **AM RECEIVER SIMULATION**

**AM RECEIVER SIMULATION**

# **REFERENCES**

- 1. <u>MOSFET Modeling with SPICE</u>, Daniel Foty, 1997, Prentice Hall, ISBN-0-13-227935-5

- 2. <u>Operation and Modeling of the MOS Transistor</u>, 2nd Edition, Yannis Tsividis, 1999, McGraw-Hill, ISBN-0-07-065523-5

- 3. <u>UTMOST III Modeling Manual-Vol.1</u>. Ch. 5. From Silvaco International.

- 4. <u>ATHENA USERS Manual</u>, From Silvaco International.

- 5. <u>ATLAS USERS Manual</u>, From Silvaco International.

- 6. Device Electronics for Integrated Circuits, Richard Muller and Theodore Kamins, with Mansun Chan, 3<sup>rd</sup> Edition, John Wiley, 2003, ISBN 0-471-59398-2

- 7. ICCAP Manual, Hewlet Packard

- 8. PSpice Users Guide.

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

2. Do a SPICE simulation for a completely different circuit not shown in this document.

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2014 Dr. Lynn Fuller

Page 65