ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

# Process Improvement Projects May 2006

# Dr. Lynn Fuller

Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Fax (585) 475-5041 Dr. Fuller's Webpage: <u>http://www.rit.edu/~lffeee</u> Email: <u>LFFEEE@rit.edu</u> Dept Webpage: <u>http://www.microe.rit.edu</u>

Rochester Institute of Technology

Microelectronic Engineering

8-29-2006 projects2006.ppt/

© August 29, 2006 Dr. Lynn Fuller

#### **OUTLINE**

Selective STI CMP Process Using Ceria Slurry Resist Removal After Chlorine Plasma Etch Ti Deposition in Perkin Elmer 2400 Ti Deposition in CVC Evaporator Improved SPC Improved CMOS Testing Use of Drytek Quad as Backup for Lam 490

**Rochester Institute of Technology**

Microelectronic Engineering

© August 29, 2006 Dr. Lynn Fuller

#### **PROCESS IMPROVEMENT FOR STI CMP**

Motivation: Past attempts at doing CMP for shallow trench (STI) using a generic oxide slurry (silica and high pH slurry) gave unsatisfactory results. Uniformity was especially poor. Wafer edge always over polished and wafer center was incomplete. The rate of removal of TEOS trench fill was low and the selectivity was low, ie. rate of polish of densified TEOS trench fill and rate of polish of nitride polish stop seemed to be equal.

A new slurry (**Rodel Corp., CeO2, KOH, ph=10**) made especially for STI was investigated. Excellent results were obtained and a new process was developed.

> Rochester Institute of Technology Microelectronic Engineering

Peng Xie and Mike Aquilino

# **PROCESS FLOW**

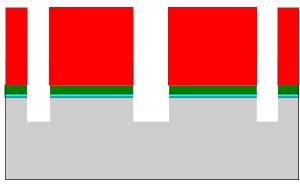

§ Grow 500A Pad Oxide (thermal)§ Deposit 1500A Si3N4 by LPCVD

§ Level 1 Lithography to protect Active areas with photoresist

§ STI Trench Etch

§ RIE in Drytek Quad

§ Target: 4000A Si Trench

Rochester Institute of Technology Microelectronic Engineering Peng Xie and Mike Aquilino

# **PROCESS FLOW**

- **§ Remove photoresist**

- § Grow 500A Liner Oxide (thermal)

- **§** Repair damage to sidewalls

- § Deposit 6500A TEOS SiO2 by PECVD in Applied Materials P5000

- § CMP TEOS with Westech 372

- § Nitride is stopping layer

Rochester Institute of Technology Microelectronic Engineering

Peng Xie and Mike Aquilino

© August 29, 2006 Dr. Lynn Fuller

# TOOLS AND MATERIAL

Rochester Institute of Technology Microelectronic Engineering

- § Westech 372 Wafer Polisher

- § Tencor SpectraMap SM300

- § Nanospec

- § Ceria-based slurry (CeO<sub>2</sub>)

© August 29, 2006 Dr. Lynn Fuller

#### **PROCESS VARIABLES (TOOL SETTINGS)**

- **§** Slurry (Rodel Corp., CeO<sub>2</sub>, KOH, ph=10)

- **§** Slurry flow rate (60 mL/min)

- § Back pressure

- § Carrier speed

- **§** Platen Speed

- § Down force

- § Temperature (80°C)

- **§** Polish time (2 min)

- **§** Pad conditioning (1min per 4 wafers)

P.S. Down Force/Wafer Pressure is controlled by gauge on side of tool. 80 PSI on gauge is 500 lbs of down force distributed over the area of 6" wafer (28.26 sq. in.) Thus Wafer Pressure = 0.2211 \* Gauge Pressure

Rochester Institute of Technology Microelectronic Engineering Peng Xie and Mike Aquilino

| © August | : 29, 20 | 006 Dr. | Lynn | Fuller |

|----------|----------|---------|------|--------|

|----------|----------|---------|------|--------|

| Page | e 7 |

|------|-----|

|      |     |

| Back<br>Pressure<br>(PSI) | Carrier<br>Speed<br>(RPM) | Platen<br>Speed<br>(RPM) | Down<br>Force (PSI) |

|---------------------------|---------------------------|--------------------------|---------------------|

| 0                         | 10                        | 70                       | 4                   |

| 1.5                       | 30                        | 100                      | 8                   |

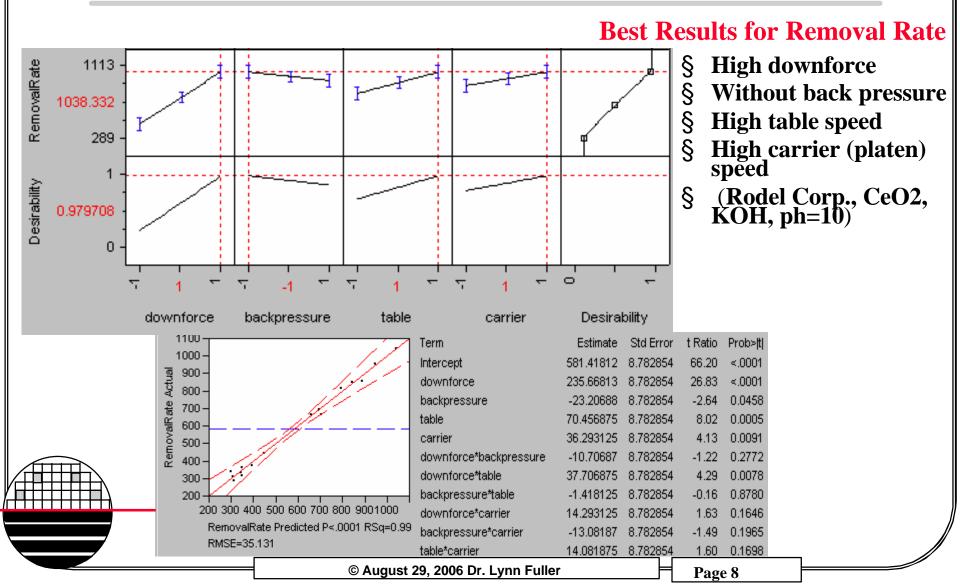

# DOE RESULTS (JUMP)

#### **BLANK WAFER RESULTS USING BEST TOOL SETTINGS**

## **Tool Settings**

- § Carrier speed: 30 RPM

- § Platen speed: 100 RPM

- **§** Without back pressure

- § 8 PSI down force

- § Slurry (Rodel Corp., CeO<sub>2</sub>, KOH, ph=10)

- § Slurry flow rate (60 mL/min)

## Results

- § Oxide etch rate: 1040 A/min

- § Nitride etch rate: 192 A/min

- § Giving selectivity of 5.4:1

- § Edge etches slower than the center!

- § Poor uniformity (46%)

Rochester Institute of Technology Microelectronic Engineering Peng Xie and Mike Aquilino

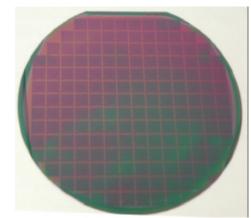

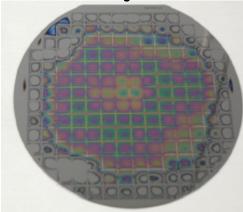

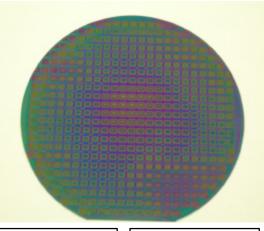

**ACTUAL FACTORY WAFER F050905**

**F050905** (oxide thickness = 6542 A)

CMP for 2 min 30sec

Slurry (Rodel Corp., CeO<sub>2</sub>, KOH, ph=10)

Slurry flow rate (60 mL/min)

Clear all the dies except at the very edge two dies

Nitride etch rate: 170 A/min

Oxide etch rate: >3271 A/min

Selectivity: >19:1

Small dishing: 4493 A at 2 min

**Observation: Higher selectivity and etch rate observed on patterned** wafers (because effective down pressure is higher)

**CMP** is highly pattern related!!!

Rochester Institute of Technology Microelectronic Engineering Peng Xie and Mike Aquilino

**ACTUAL FACTORY WAFER F051010**

F051010 (oxide thickness = 5286 A) CMP for 2 min 15sec

Slurry (Rodel Corp., CeO<sub>2</sub>, KOH, ph=10)

Slurry flow rate (60 mL/min)

Clear almost every die even at the edge

Nitride etch rate: 170 A/min

Oxide etch rate: >2350 A/min

Selectivity: >14:1

Small dishing: 3800 A at 2 min 30sec

**Observation: Higher selectivity and etch rate observed on patterned wafers (because effective down pressure is higher)**

**CMP** is highly pattern related!!!

Rochester Institute of Technology Microelectronic Engineering Peng Xie and Mike Aquilino

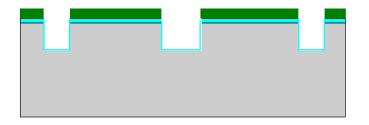

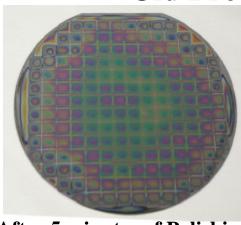

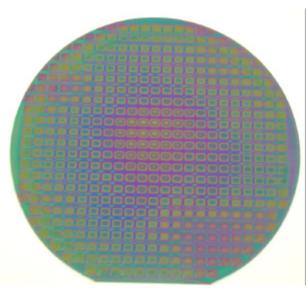

COMPARISON BETWEEN OLD CMP SLURRY AND PROCESS AND NEW SLURRY AND PROCESS

# **Old Process and Slurry**

#### Wafer before CMP

After 5 minutes of Polishing Center not done

f Polishing done After 9.5 minutes of Polishing Center done, Edges Bare New Process and Slurry

After 2.25 minutes of Polishing Clear almost every die Even edge die

© August 29, 2006 Dr. Lynn Fuller

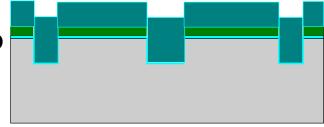

## **NEW FACTORY STI PROCESS (FACTSTI)**

- § Carrier speed: 30 RPM

- § Platen speed: 100 RPM

- § Without back pressure

- § 8 PSI down force (36 PSI on the gauge)

- § Slurry (Rodel Corp., CeO<sub>2</sub>, KOH, ph=10)

- § Slurry flow rate (60 mL/min)

- § Pad conditioning: before every run

- § Temperature: 80°C

- § Polishing time: 2min 30 sec for 6500A oxide

Rochester Institute of Technology Microelectronic Engineering Peng Xie and Mike Aquilino

# **CMP SLURRY**

Eminess Technologies, Inc. 1620 West fountainhead Pkwy, Suite 510 Tempe, AZ 85282 Tel (408)505-3409, 888-899-1942, fax (480)951-3842

Darlene Werkmeister Dwerkmeister@eminess.com http://www.EMINESS.com http://www.electronicmaterials.rohmhaas.com

1/05/06 Order:N-2350-P Nalco 2350, 5 gal pail \$166 each, Mfg by Rohm and Haas, Silica, 70-100nm particle size, weight % 28, KOH, pH 11.4-12.4

R-10027556 Klebosol 1501-50 Colloidal Silica 5 gal pail \$255 each, Mfg AZ Electronic Materials, Clariant's Klebosol line of silica slurrys,50nm particles, KOH pH 10.9 50% solids

R-10087555 EXP CELEXIS CX94S Single Component Slurry, 20Liter pail \$235 each, Mfg by Rohm and Haas Ceria 20nm particles, STI, pH ~7

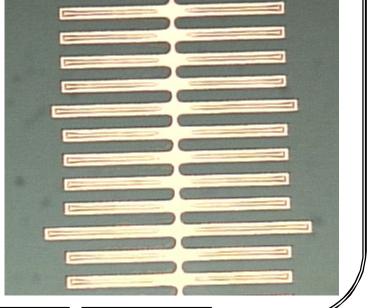

**RESIST REMOVAL POST CHLORINE RIE ALUMINUM ETCH**

**Problem:** Photoresist is hardened (and chemically changed) in Chlorine RIE during Aluminum etch and ashing is ineffective in removing the resist.

**Solution:** Use a Solvent based photoresist stripper process. (similar to Baselinc CMOS process at U of California at Berkeley)

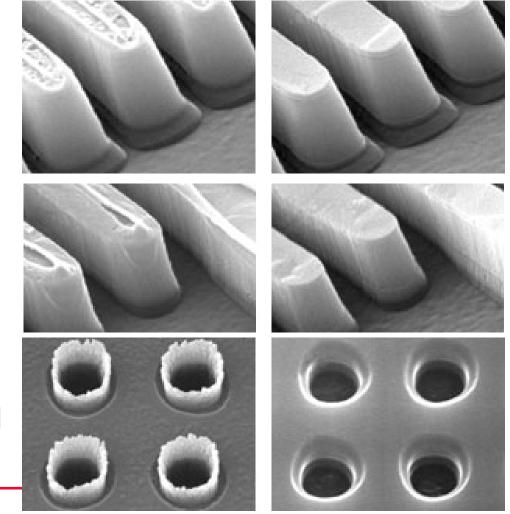

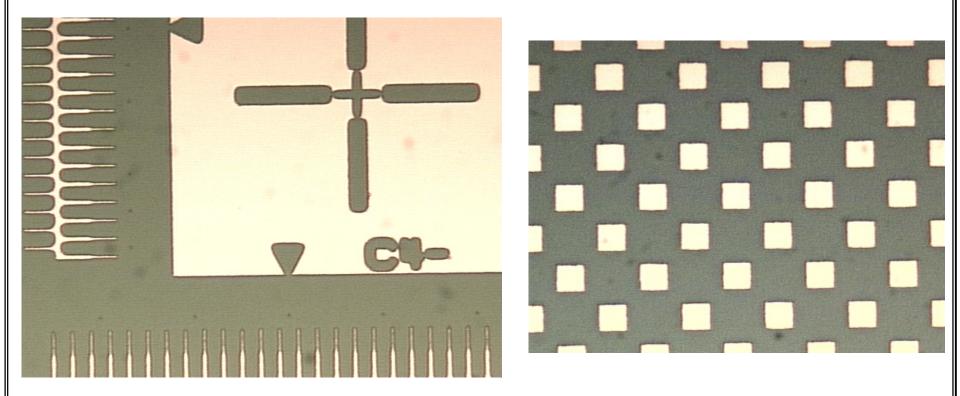

Picture of aluminum wafers post chlorine RIE and after ashing. Note resist remaining on aluminum. Even very long ashing (60 min.) does not remove residue.

#### Germain Fenger

Rochester Institute of Technology

Microelectronic Engineering

© August 29, 2006 Dr. Lynn Fuller

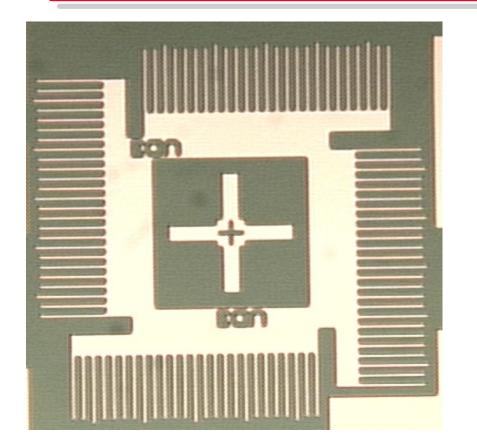

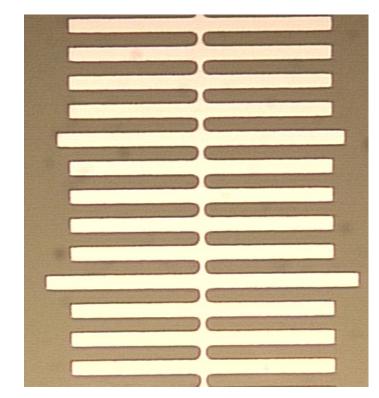

#### **MORE PICTURES OF RESIST SCUM PROBLEM**

Pictures on left show resist residue after ashing. Pictures on right show effectiveness of ACT 935 solvent strip process.

#### From: [ACT-CMI Data Sheet]

Rochester Institute of Technology Microelectronic Engineering

© August 29, 2006 Dr. Lynn Fuller

#### **EXPERIMENT**

**Deposit TEOS** Deposit Aluminum Metal Litho Metal Etch **Resist Strip** ACT-CMI, 75C for 15 or 30 min or PRS2000, 90C for 30 min Plasma Ash 6" Factory Recipe or 6" Descum Recipe

Germain Fenger

Rochester Institute of Technology

Microelectronic Engineering

© August 29, 2006 Dr. Lynn Fuller

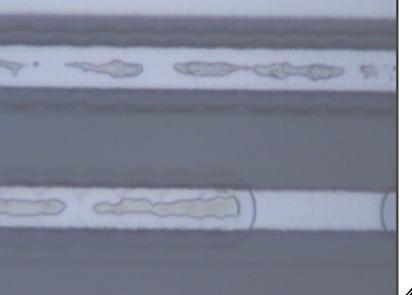

#### **RESULTS FOR ACT CMI 75C for 15 or 30 min**

Longer time did not make a difference

Rochester Institute of Technology

Microelectronic Engineering

Germain Fenger

© August 29, 2006 Dr. Lynn Fuller

**RESULTS for Post Solvent Strip PLUS 6'' Factory Plasma Ash**

Rochester Institute of Technology

Microelectronic Engineering

Germain Fenger

© August 29, 2006 Dr. Lynn Fuller

#### **RESULTS FOR PRS2000 90C for 30min**

Rochester Institute of Technology

Microelectronic Engineering

Germain Fenger

© August 29, 2006 Dr. Lynn Fuller

# **RECOMMENDATIONS**

#### **OBSERVATIONS:**

- § A solvent based photoresist stripper followed by a plasma ash is effective at removing Cl burn resist

- § The PRS2000 strips resist better than the ACT-CMI solvent stripper and is currently in use in the solvent stripper bench

# **RECOMMENDED PROCESS:**

- § PRS2000 at 90C for 15 min

- § Follow up with 6" Factory ash on the Branson Asher

Rochester Institute of Technology

Microelectronic Engineering

Germain Fenger

© August 29, 2006 Dr. Lynn Fuller

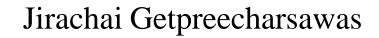

Ti DEPOSITION USING P&E 2400B

# **OBJECTIVE**

# To develop a Ti Deposition process using Perkin Elmer 2400B sputtering tool (a factory backup process for CVC 601 tool)

Ti DEPOSITION USING P&E 2400B

# RESULTS

- § Sputtering Power: 500 W for 158 Å/min

- § Base Pressure: < 5 x 10<sup>-6</sup> Torr

- § Sputtering Pressure: 8 mTorr (Argon flow:15 sccm)

- § Deposition Time: 380 Seconds to get 1000Å Thickness

- § Thickness standard deviation 4% (30 Å)

- **§ Pre-Sputtering: 5 minutes same power**

Rochester Institute of Technology

Microelectronic Engineering

Shrinivas J Pandharpure

© August 29, 2006 Dr. Lynn Fuller

**PHYSICAL PROPERTIES OF TI AND W**

§ Titanium (Ti) : Melting point,  $T_{melt} = 1675 \ ^{\circ}C$

| Vapor Pressure (Torr) | T <sub>vapor</sub> (°C) |

|-----------------------|-------------------------|

| 10-4                  | 1453                    |

| 10-6                  | 1235                    |

| 10-8                  | 1067                    |

99.995% pure 0.108 gram/pellet

Note: Ti sublimes since **Tvapor < Tmelt**

§ Tungsten (W): Melting point ,  $T_{melt} = 3410 \ ^{\circ}C$

**Rochester Institute of Technology**

Microelectronic Engineering

© August 29, 2006 Dr. Lynn Fuller

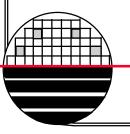

#### **Ti DEPOSITION USING CVC EVAPORATOR**

| Pressure                      | 1 Pelle                                   | t of Ti | 2 Pellets of Ti |        |  |

|-------------------------------|-------------------------------------------|---------|-----------------|--------|--|

| (Torr)                        | Mean (Å)                                  | STD     | Mean (Å)        | STD    |  |

| 3.4 × 10 <sup>-6</sup>        | 321.67                                    | 176.16  | 469.44          | 138.48 |  |

| <b>1.6</b> × 10 <sup>-6</sup> | 340.00                                    | 84.84   | 1366.67         | 163.58 |  |

|                               | © August 29, 2006 Dr. Lynn Fuller Page 26 |         |                 |        |  |

<u>Process Improvement Projects 2006</u>

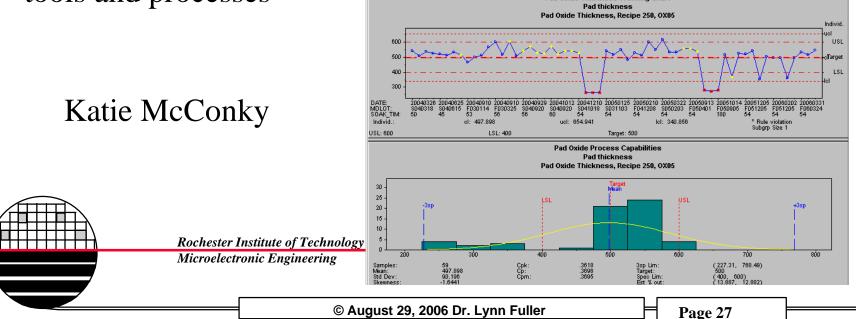

# **IMPROVED SPC**

**Problem:** SPC charts are that can be accessed from inside MESA need to be revised for the new processes (SMFL-CMOS and ADV-CMOS)

**Solution:** The SPC charts have been updated and a detailed document on how to create and edit SPC charts has been posted on Dr. Fullers webpage at <u>http://www.rit.edu/~lffeee</u> from the link for tools and processes

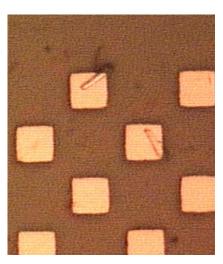

**IMPROVED CMOS TESTING**

**Problem:** Documentation for wafer testing of completed CMOS devices is inadequate.

**Solution:** A complete, very detailed, set of instructions have been developed for basic testing of CMOS wafers. This document is available on Dr. Fullers webpage at <u>http://www.rit.edu/~lffeee</u> from the link for tools and processes

David Pawlik

Rochester Ins Microelectron

© August 29, 2006 Dr. Lynn Fuller

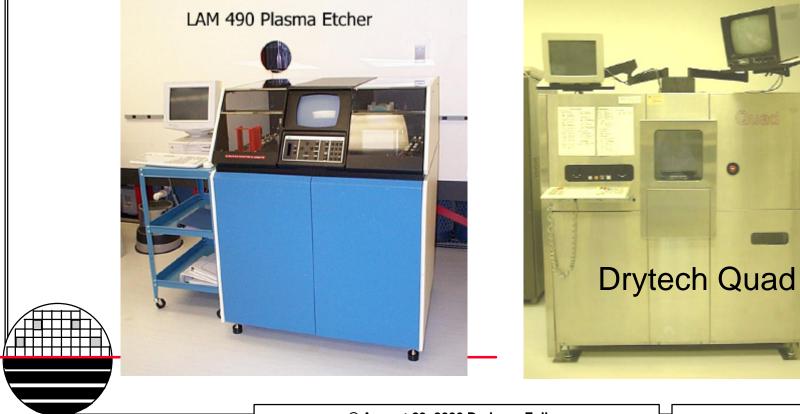

**USING THE DRYTEC QUAD AS A BACKUP FOR LAM 490**

**Problem:** When the Lam490 is down wafers can be etched in the Drytech Quad however etch recipes giving similar etch rates and selectivity's need to be developed.

**USING THE DRYTEC QUAD AS A BACKUP FOR LAM 490**

**Solution:** Recipes have been developed and have been published in a document (Quad\_recipes.ppt). This document is available on Dr. Fullers webpage at <u>http://www.rit.edu/~lffeee</u> from the link for tools and processes