ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

# **PMOS Integrated Circuit Test Results**

# **Dr. Lynn Fuller**

Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Fax (585) 475-5041

Dr. Fuller's Webpage: <u>http://people.rit.edu/~lffeee</u> Email: <u>lffeee@rit.edu</u>

Dept Webpage: http://www.microe.rit.edu

Rochester Institute of Technology

Microelectronic Engineering

11-16-2007 PMOS\_IC\_Test.ppt/

© November 16, 2007 Dr. Lynn Fuller

# **OUTLINE**

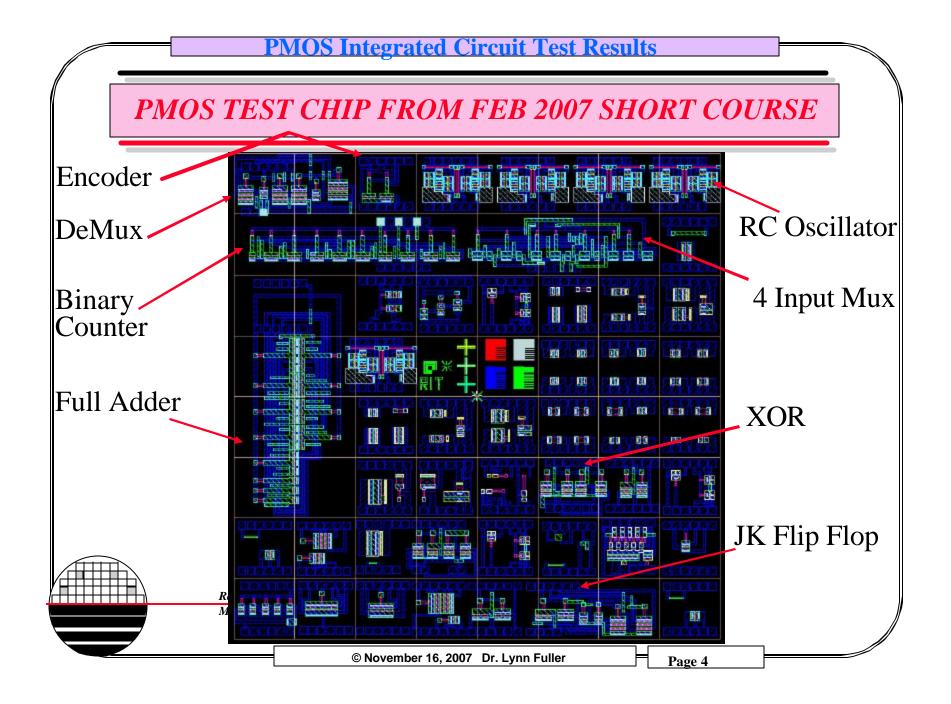

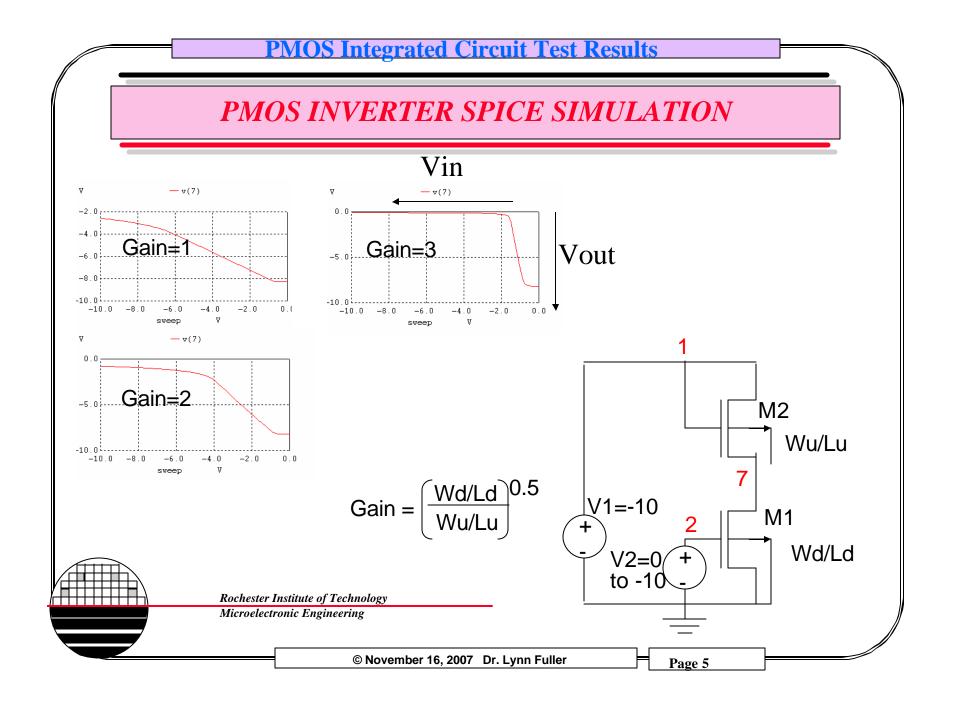

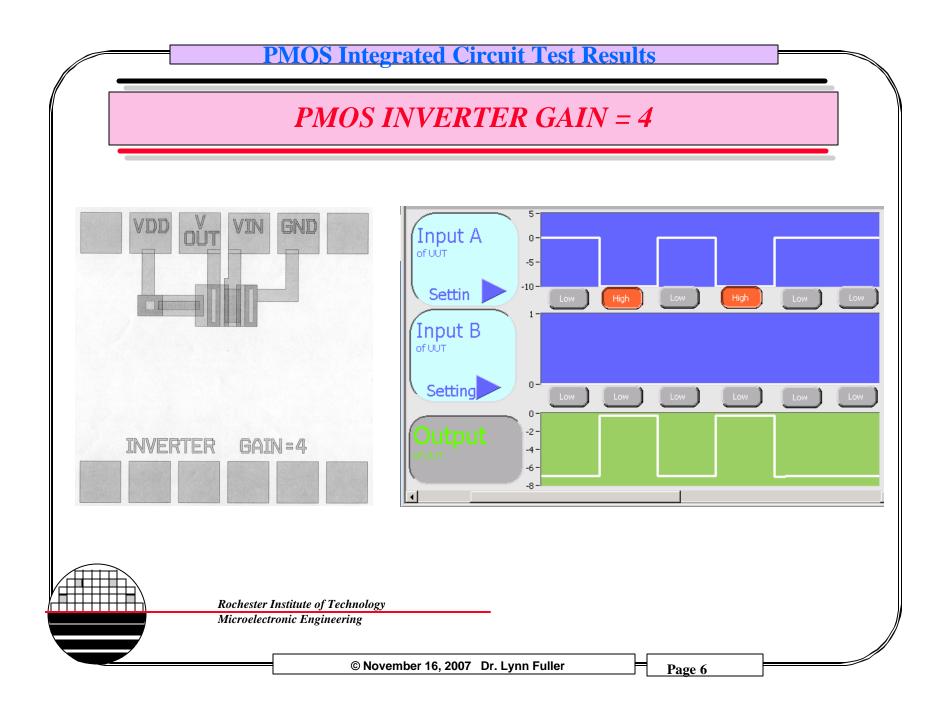

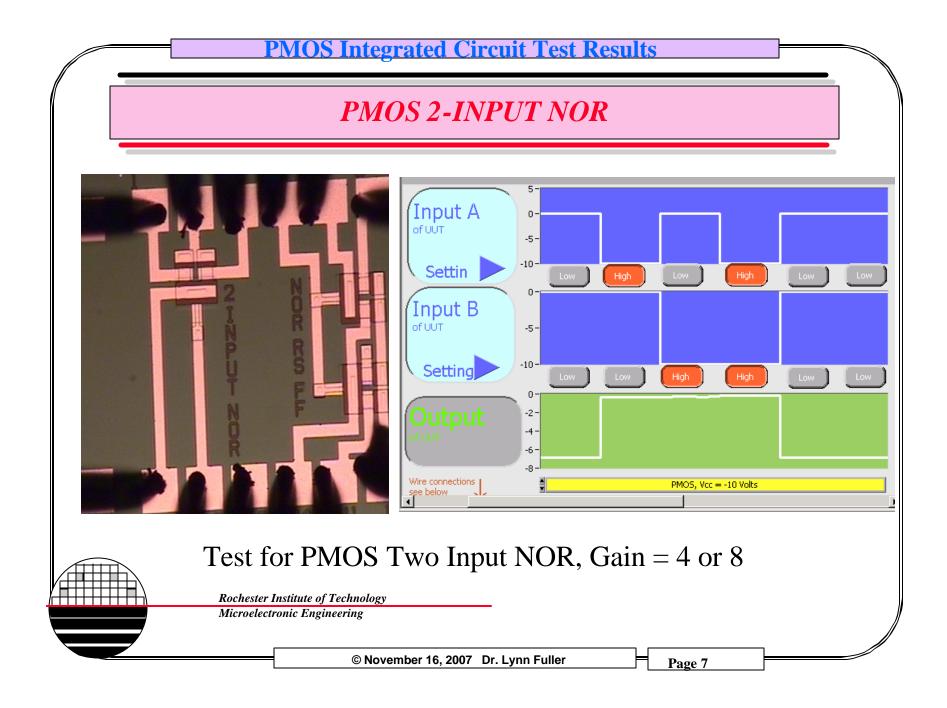

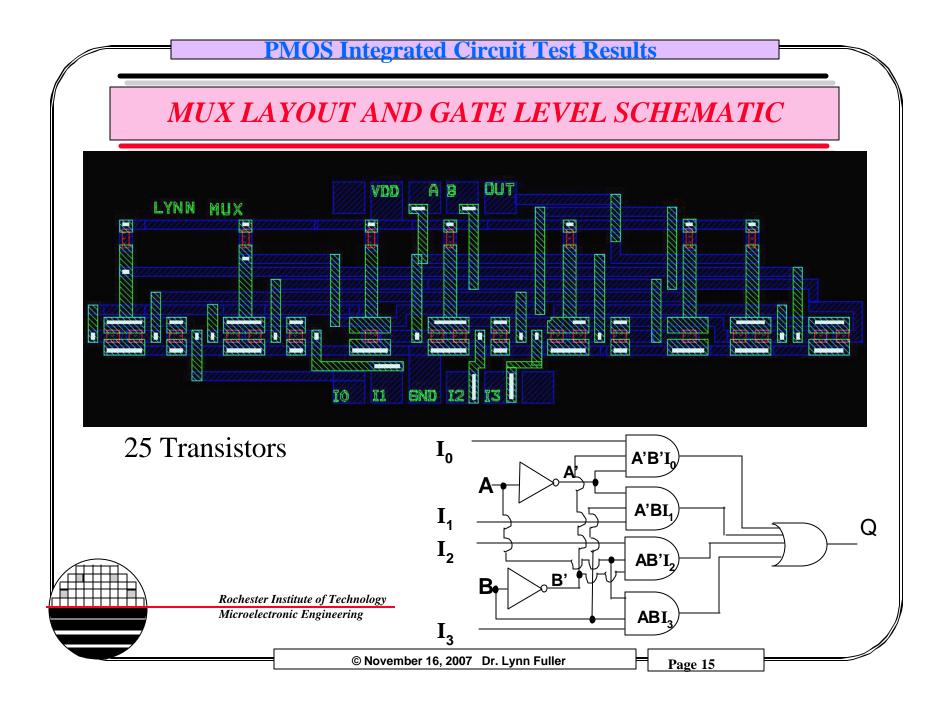

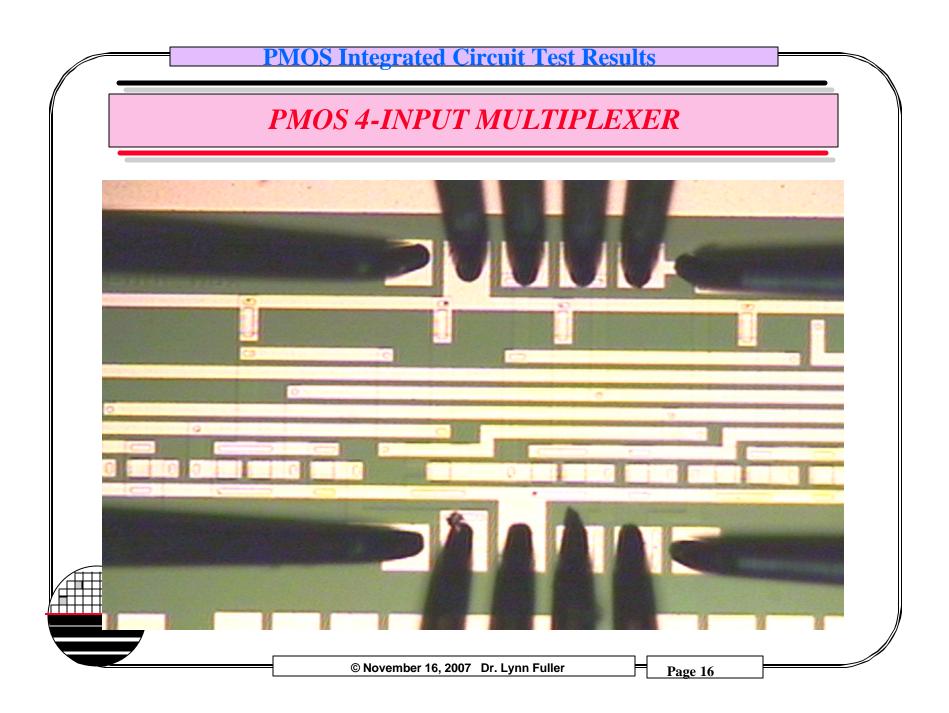

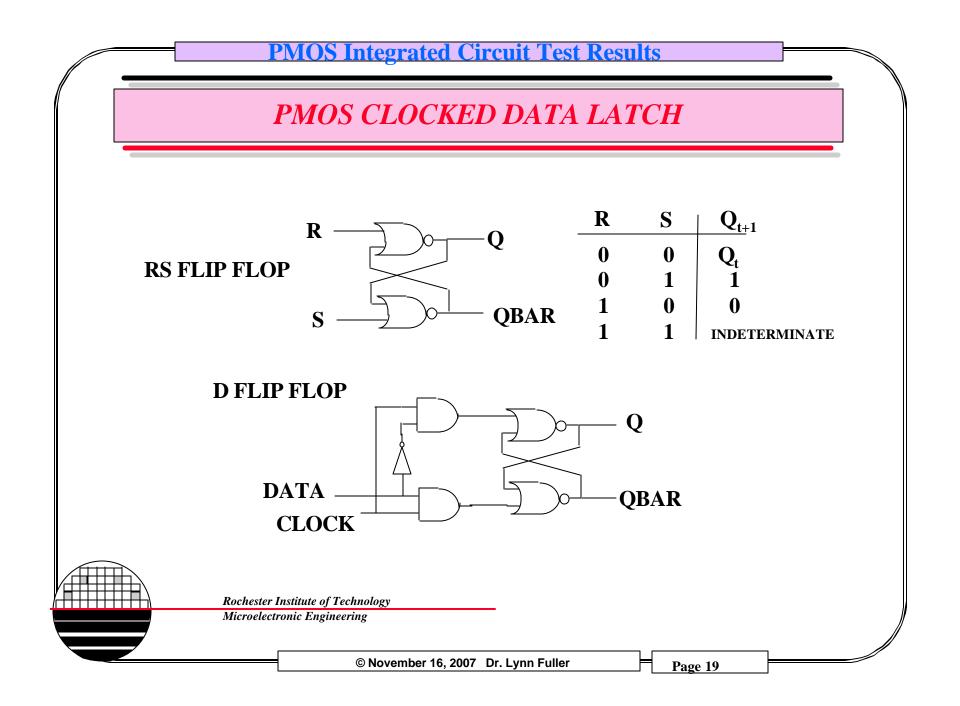

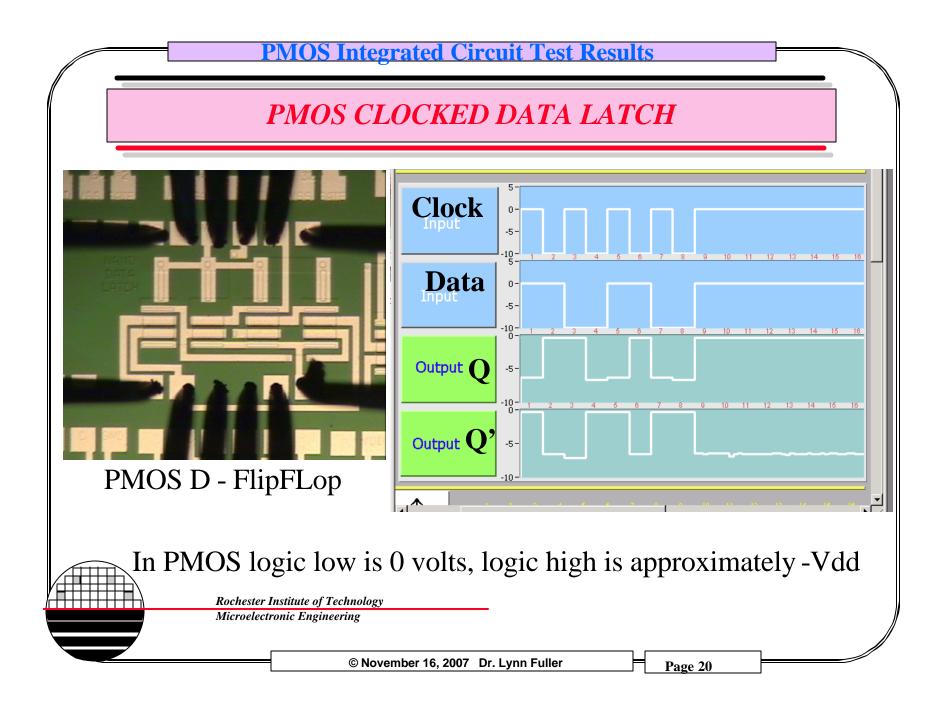

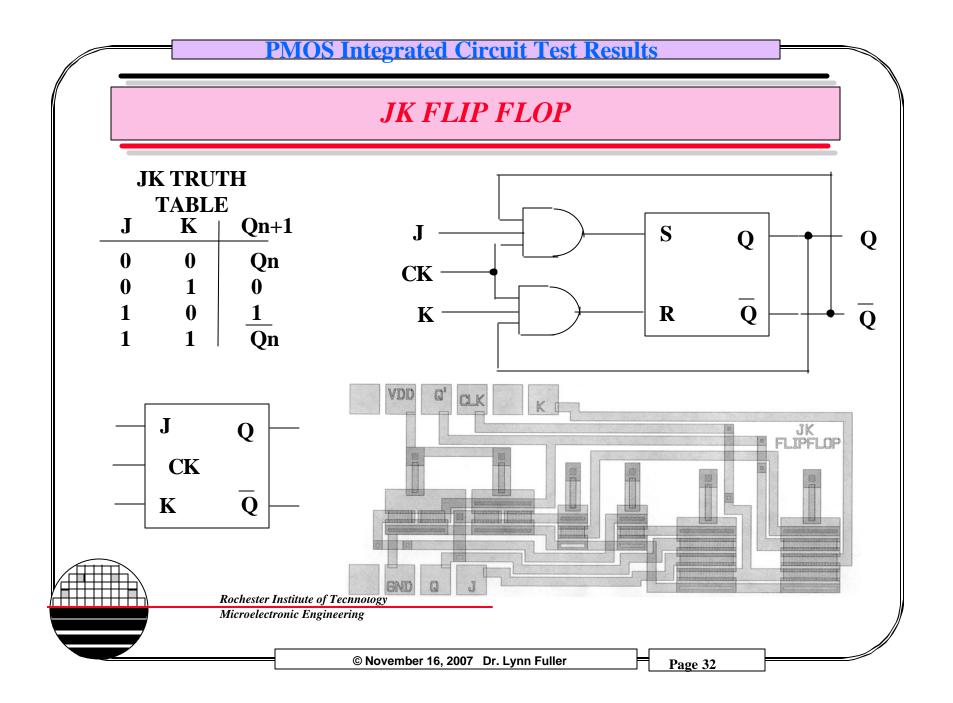

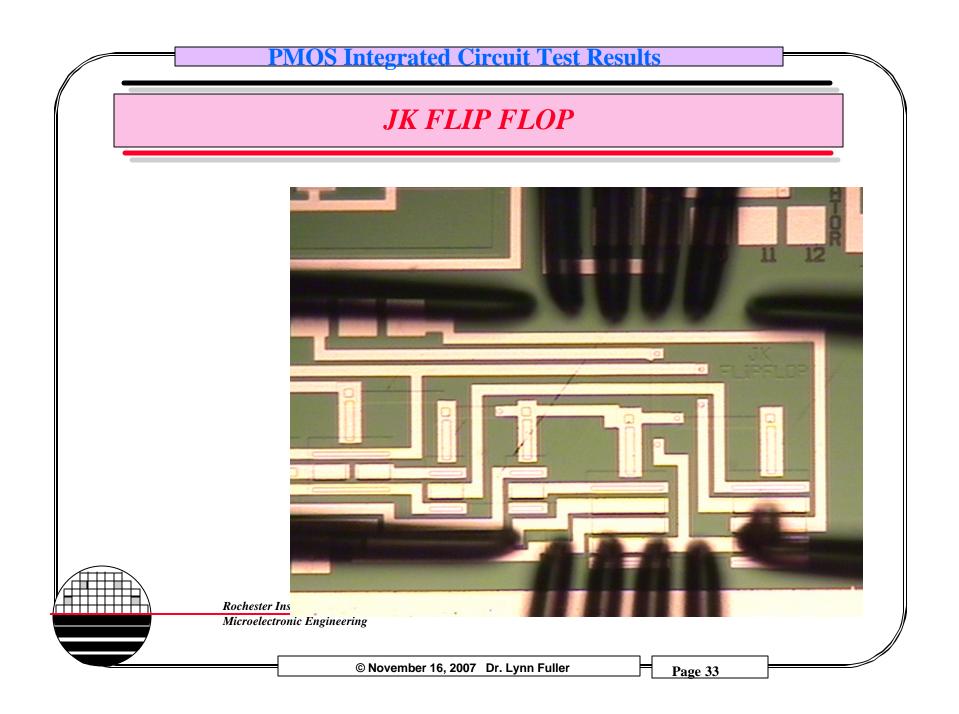

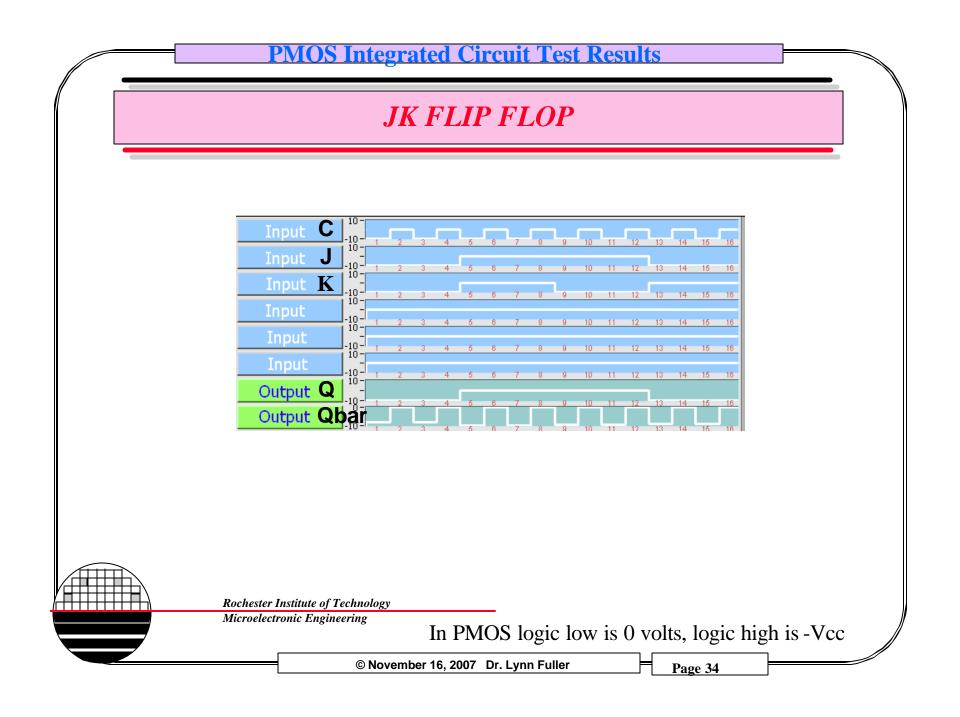

Introduction Inverter NOR (2,3,4 input) XOR 4:2 Encoder 4 input Multiplexer Clocked Data Latch Full Adder 1:4 Demultiplexer/Decoder JK Flip Flop Analog Multiplexer **Binary Counter**

Rochester Institute of Technology

Microelectronic Engineering

© November 16, 2007 Dr. Lynn Fuller

Page 2

# **INTRODUCTION**

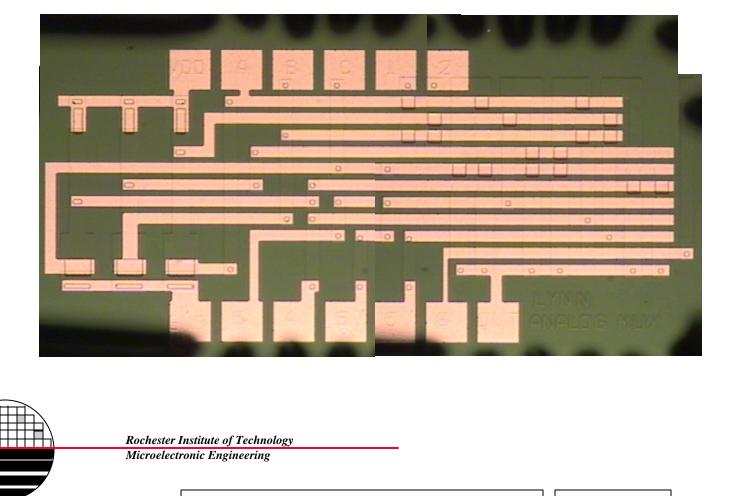

We have been making transistors and integrated circuits at RIT since 1977. We have used Metal Gate PMOS, Bipolar, NMOS, and CMOS technologies.

This document shows some test results for integrated circuits made in Metal Gate PMOS technology.

Rochester Institute of Technology Microelectronic Engineering

© November 16, 2007 Dr. Lynn Fuller

Page 3

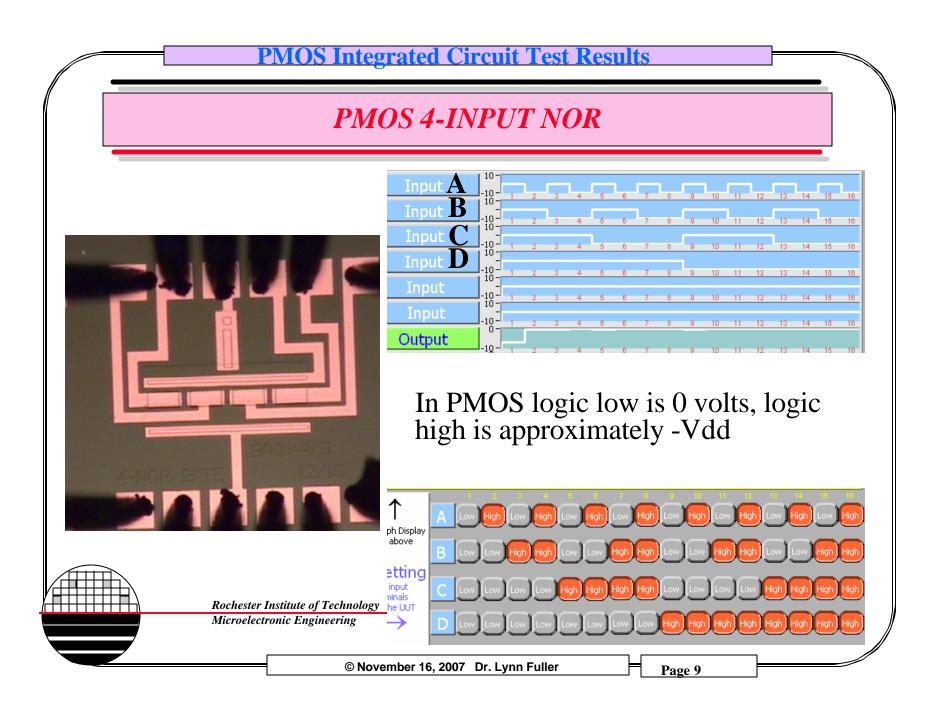

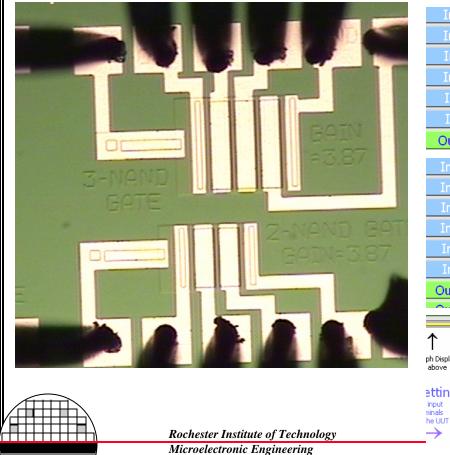

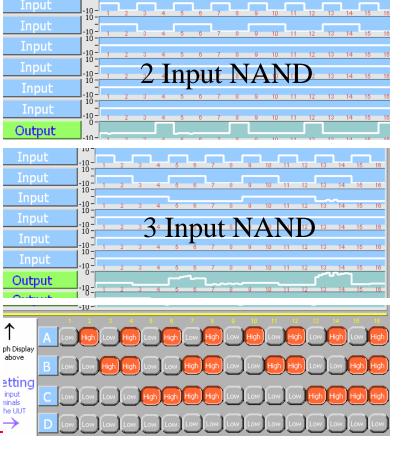

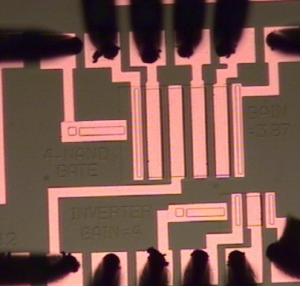

# PMOS 2 AND 3 INPUT NAND

© November 16, 2007 Dr. Lynn Fuller

# PMOS 4-INPUT NAND

# Build IC's with NOR gates (2-input NAND works okay)

Note: NAND gates have problems with so many transistors in series between the supply and ground. Here 5 transistors each with Vt ~2 volts in series and a 10 volt supply

© November 16, 2007 Dr. Lynn Fuller

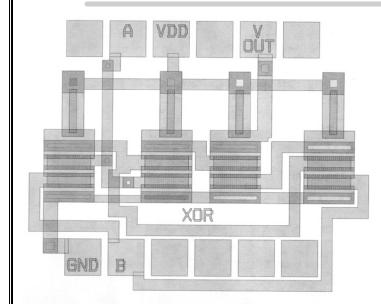

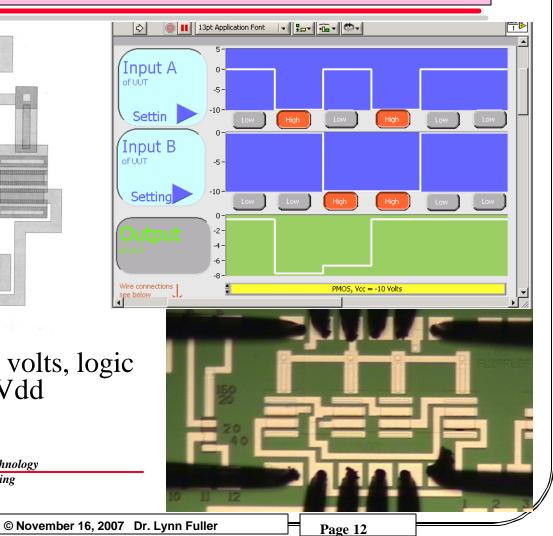

## **PMOS 2-INPUT XOR**

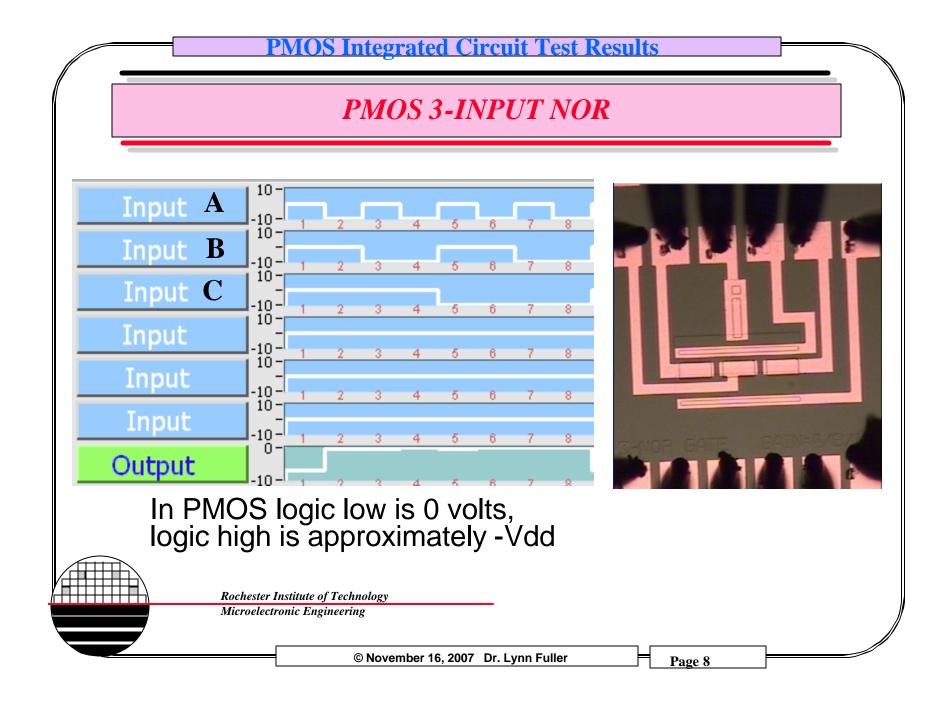

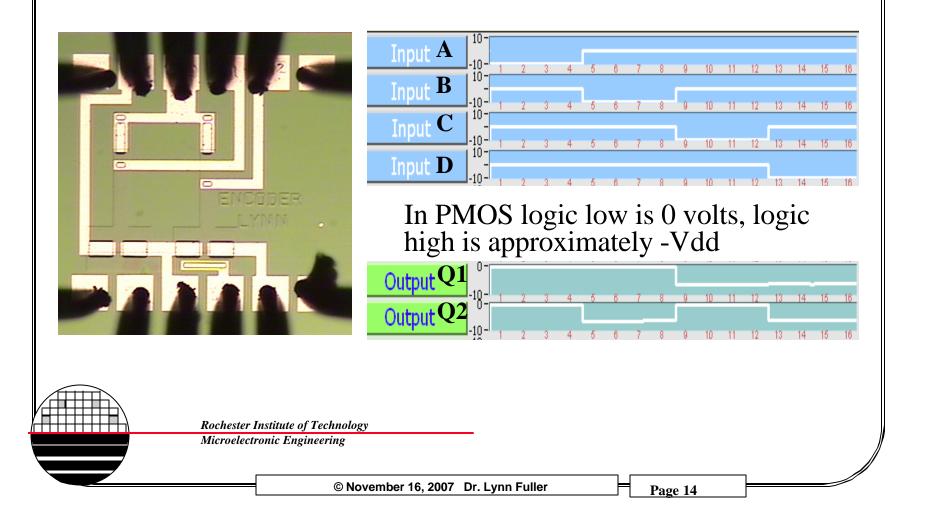

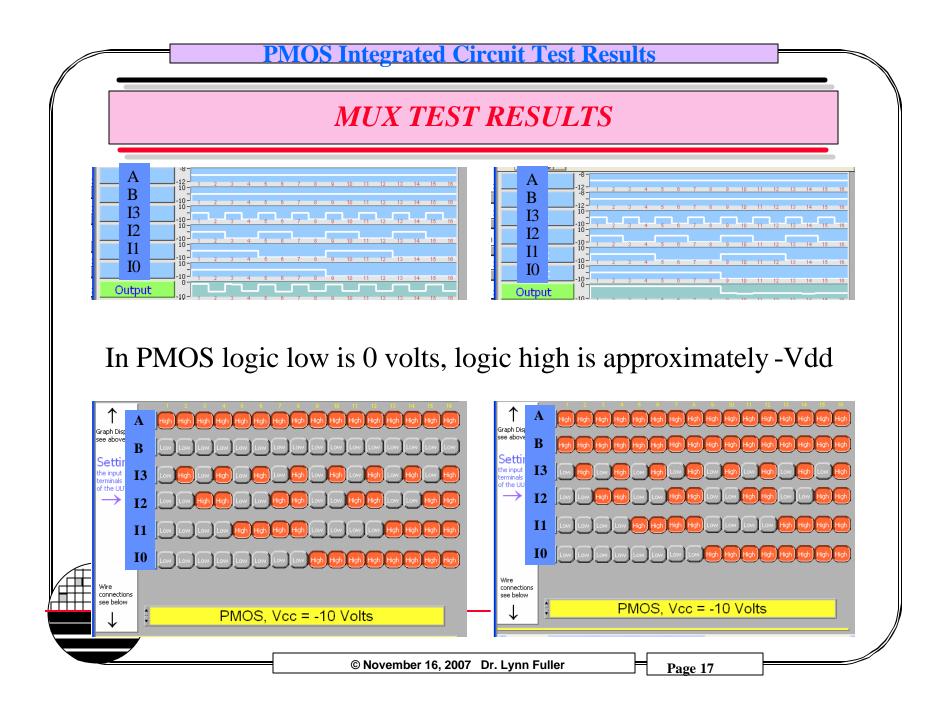

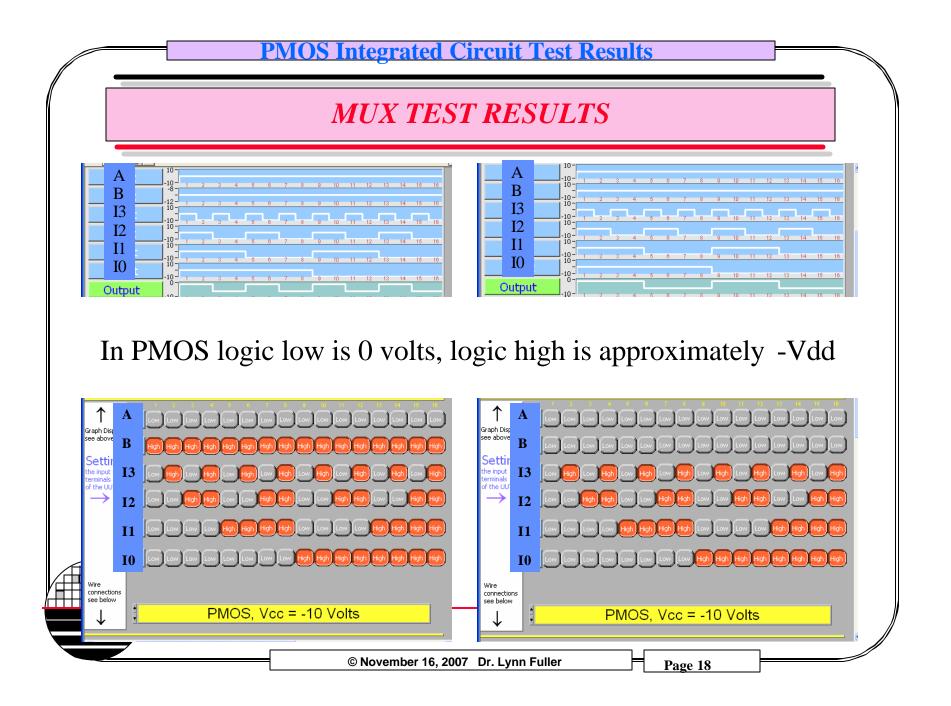

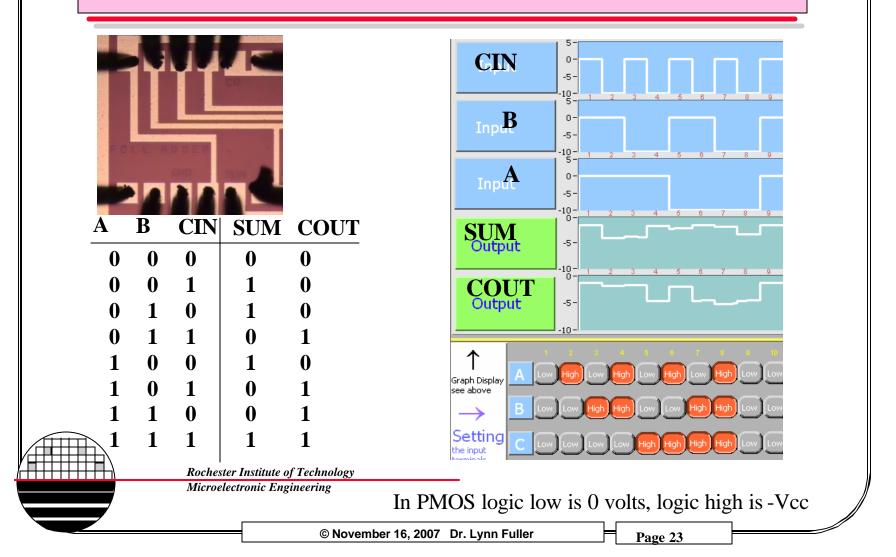

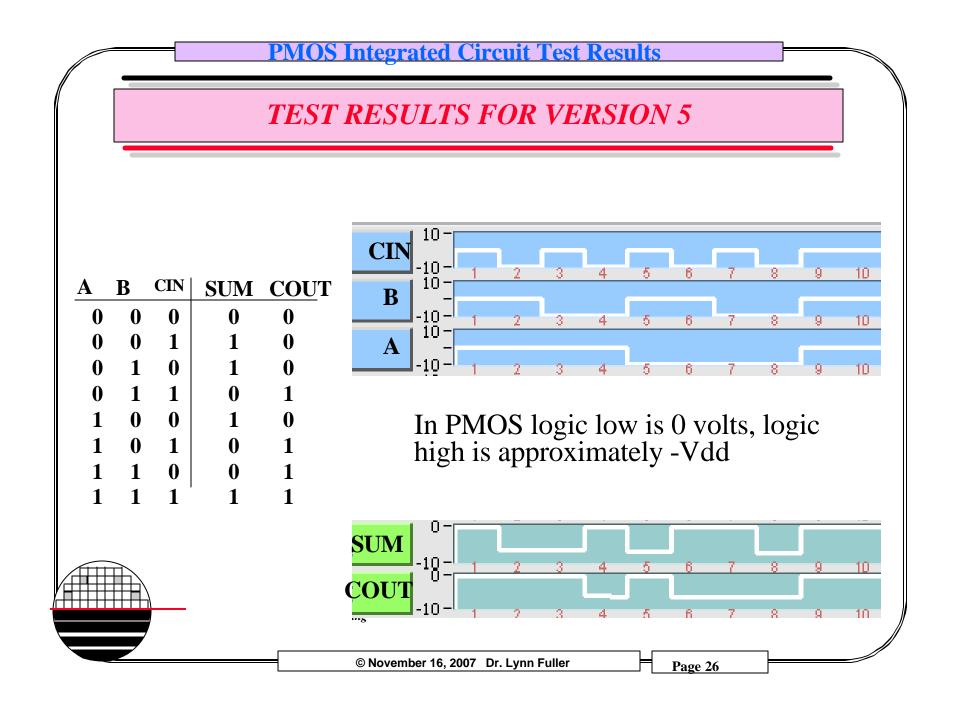

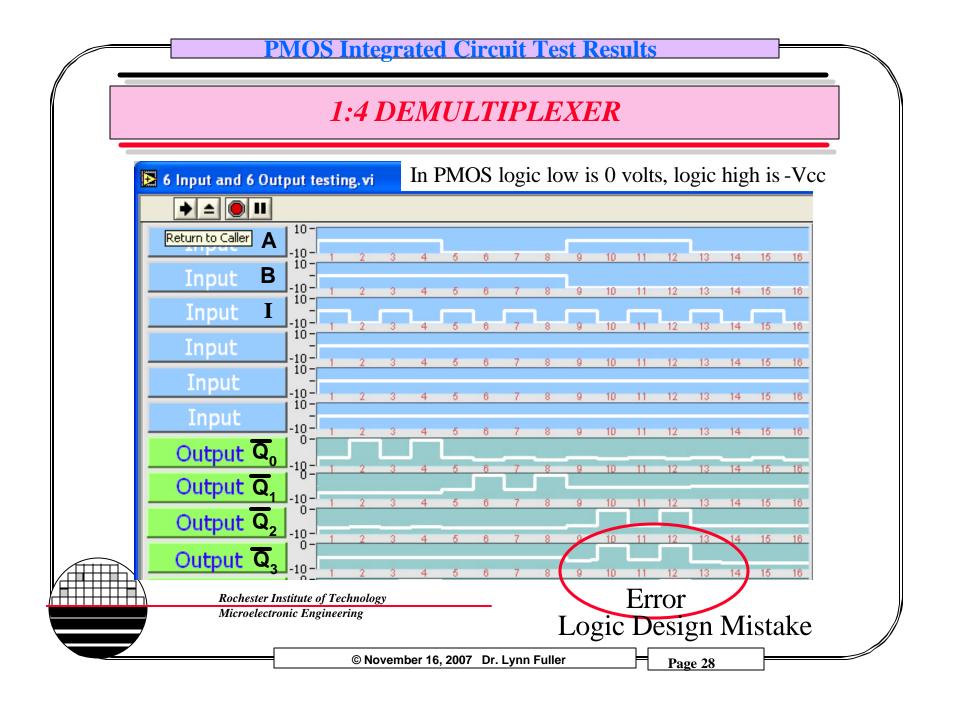

In PMOS logic low is 0 volts, logic high is approximately -Vdd

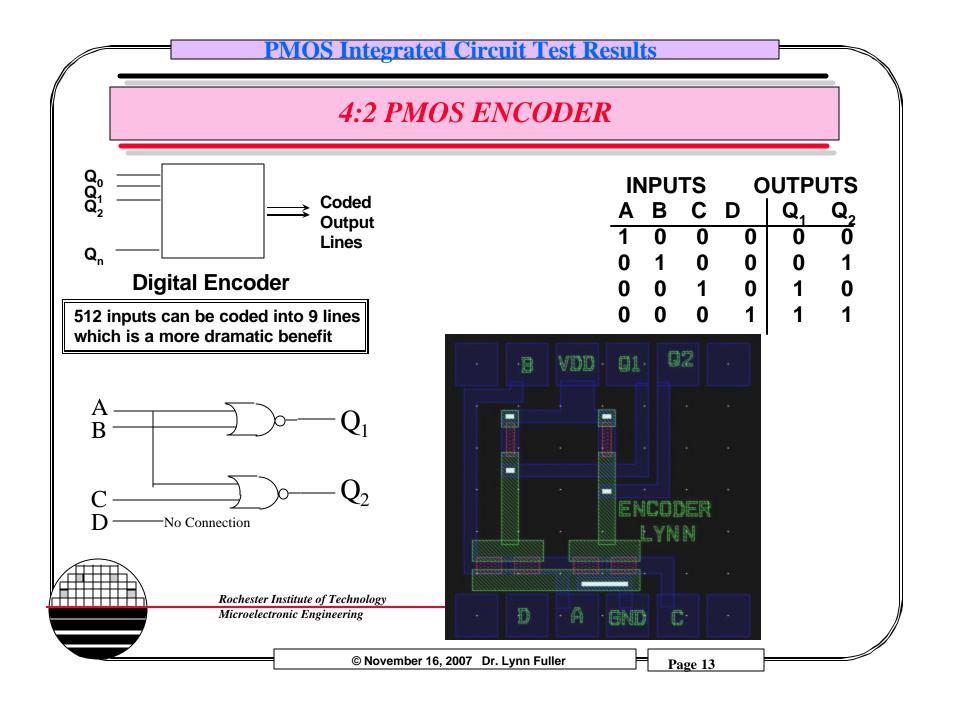

#### 4:2 PMOS ENCODER

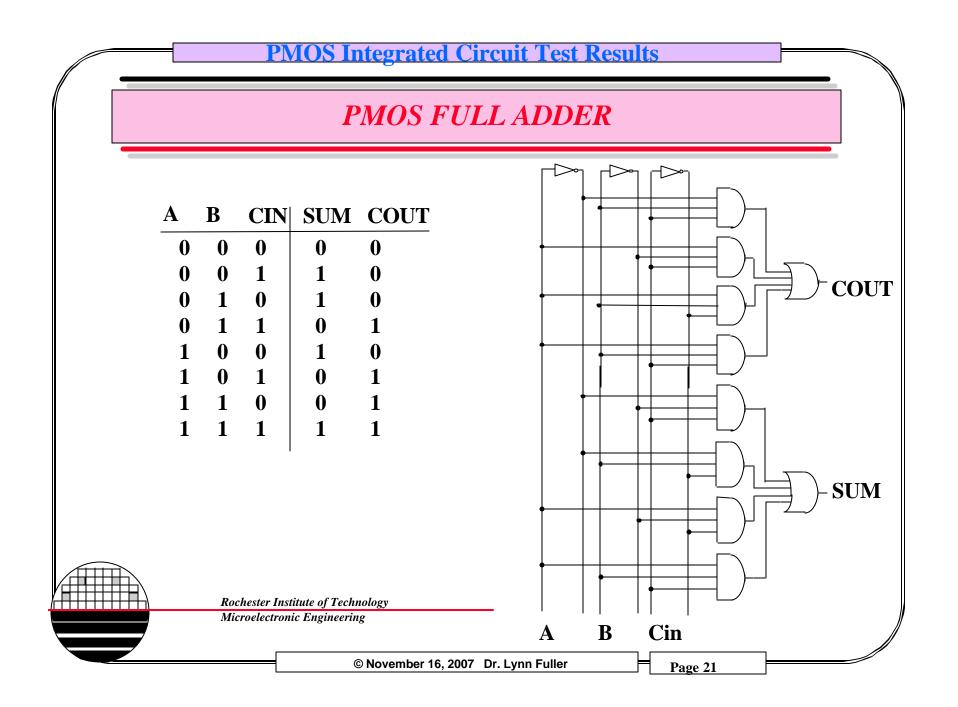

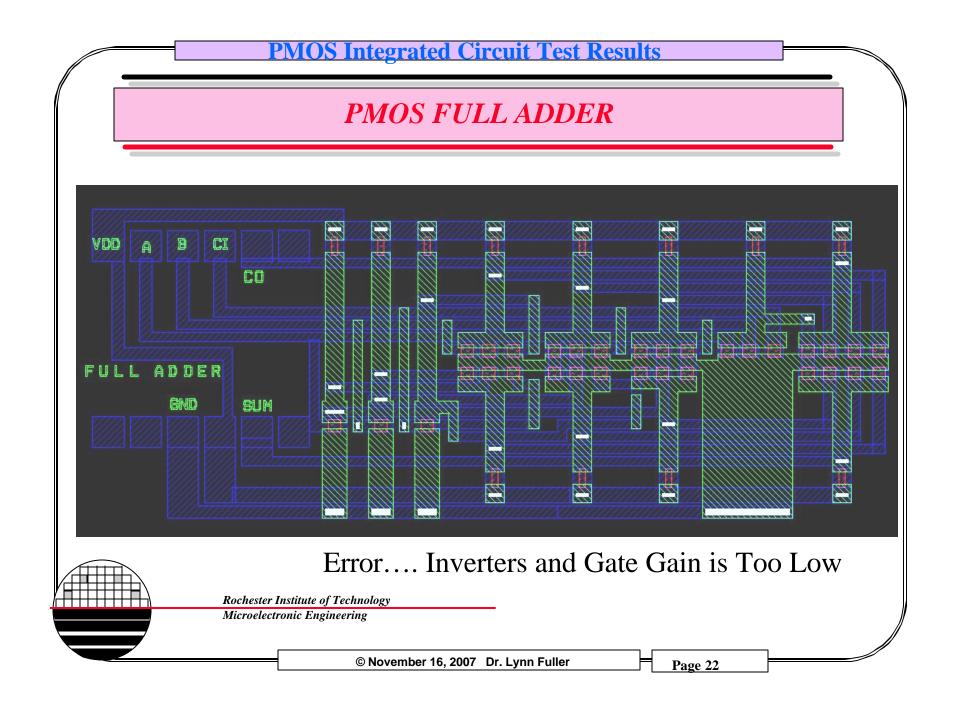

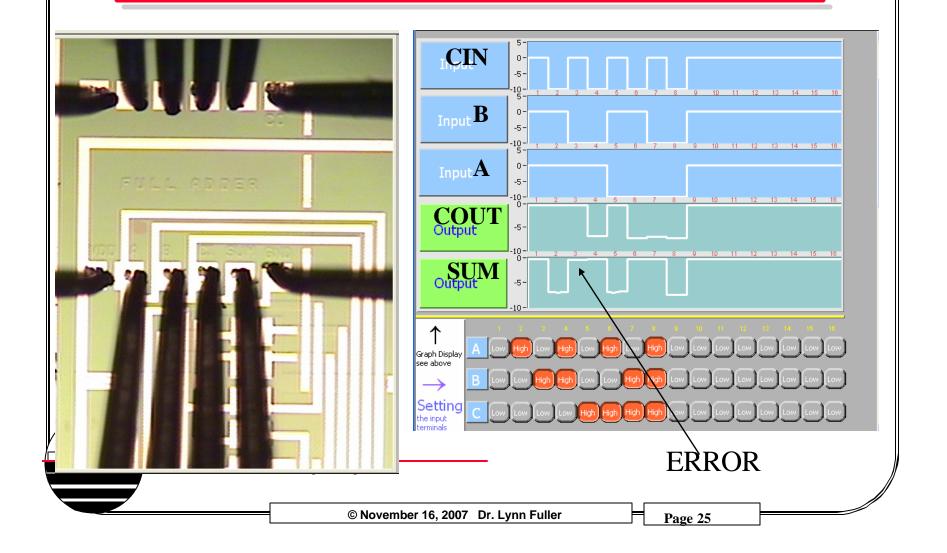

#### **PMOS FULL ADDER**

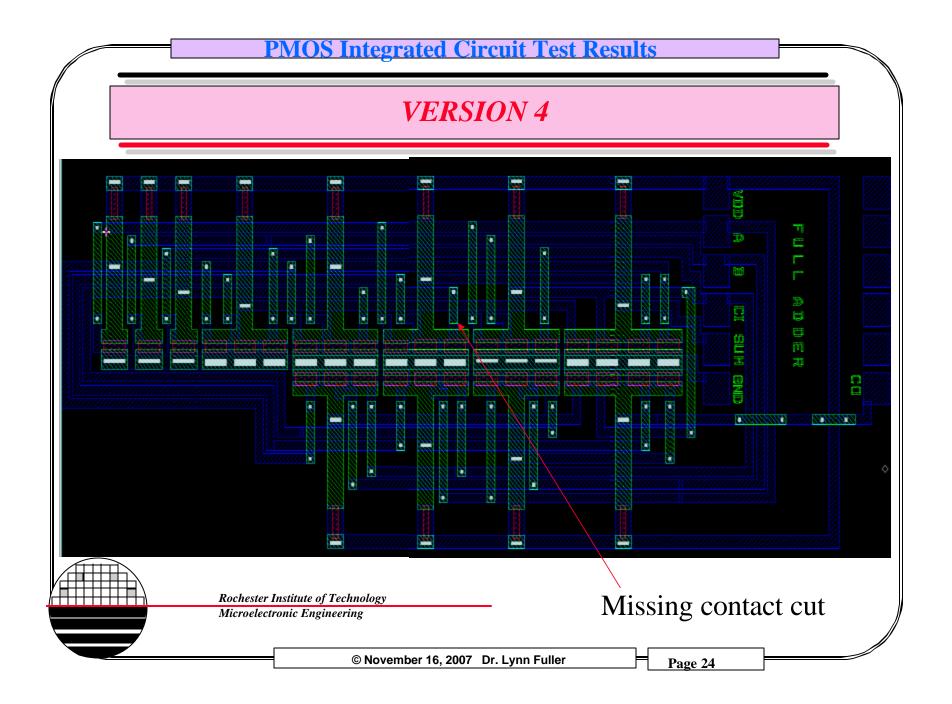

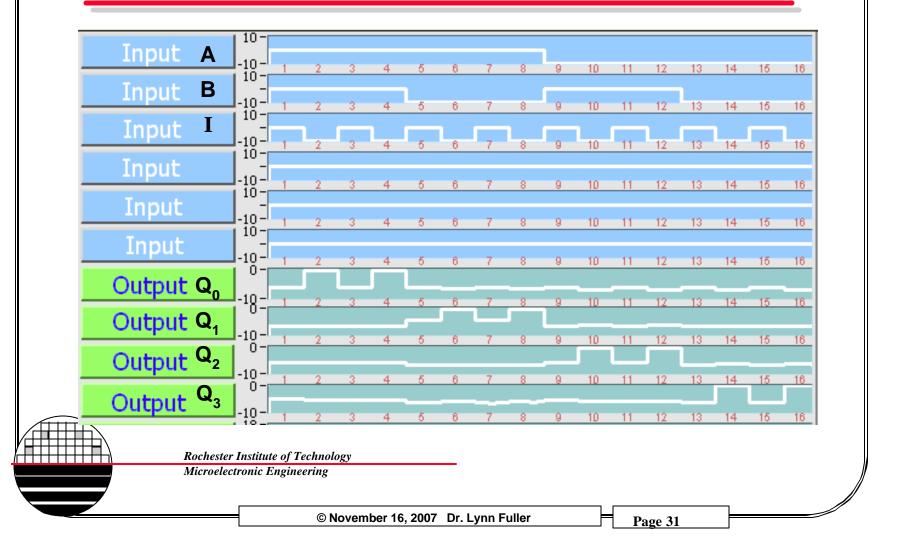

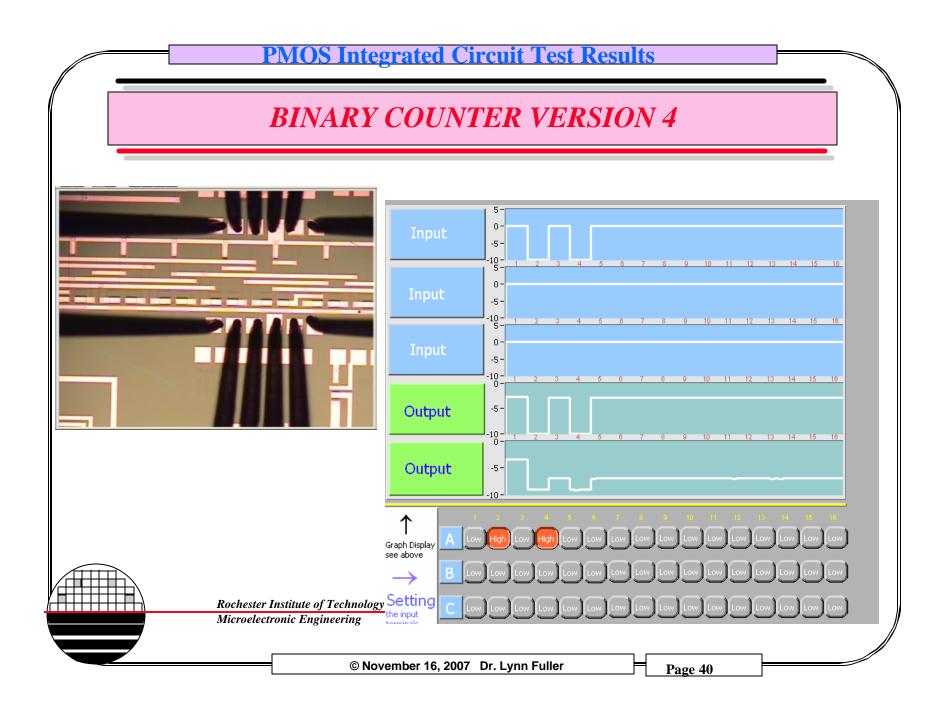

## **TEST RESULTS FOR VERSION 4**

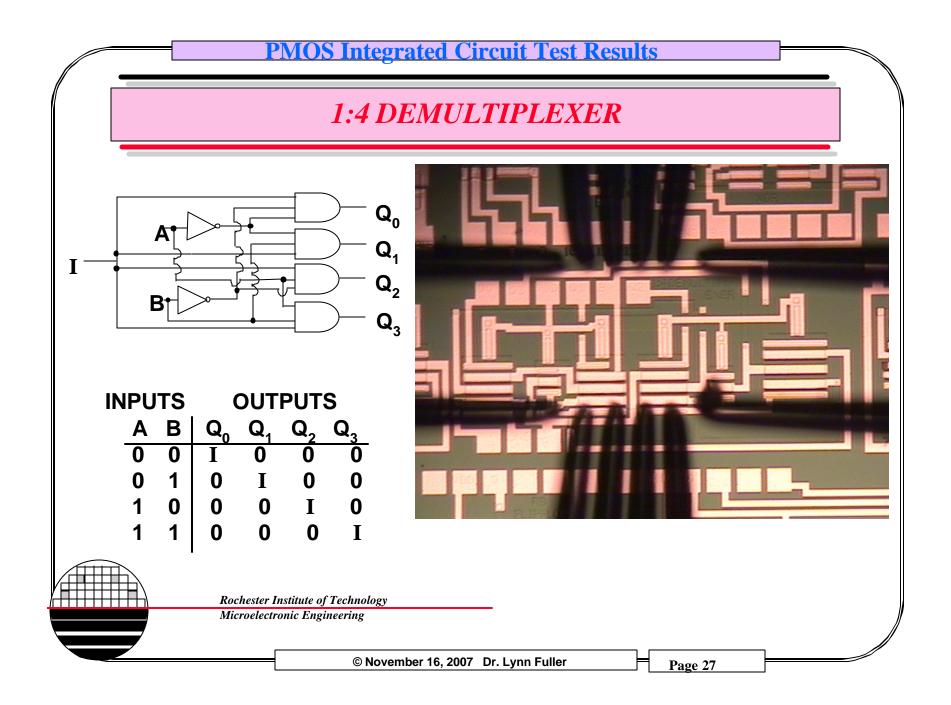

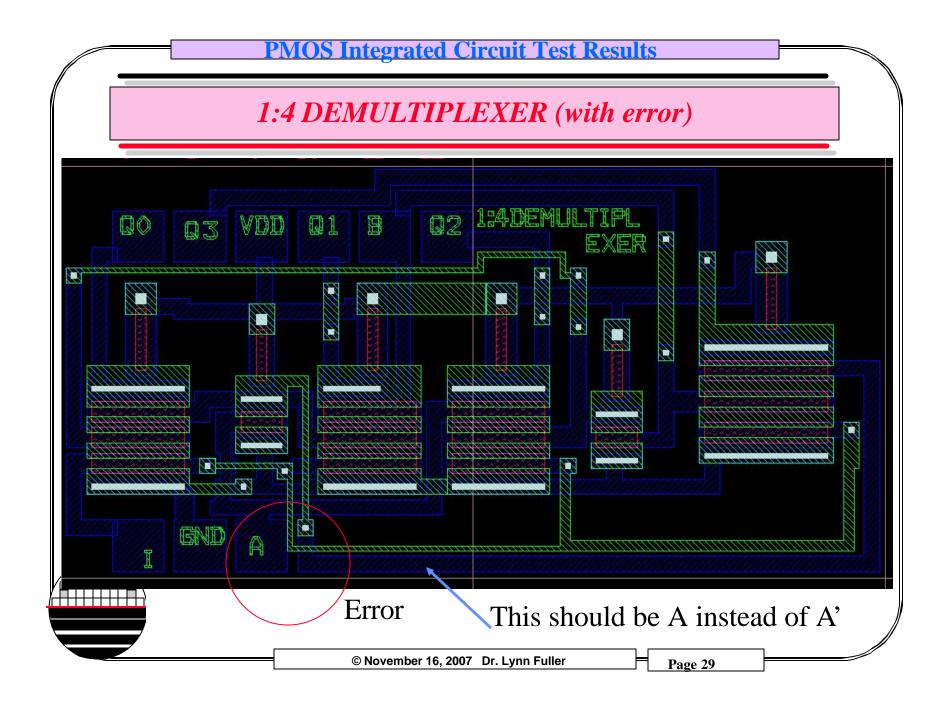

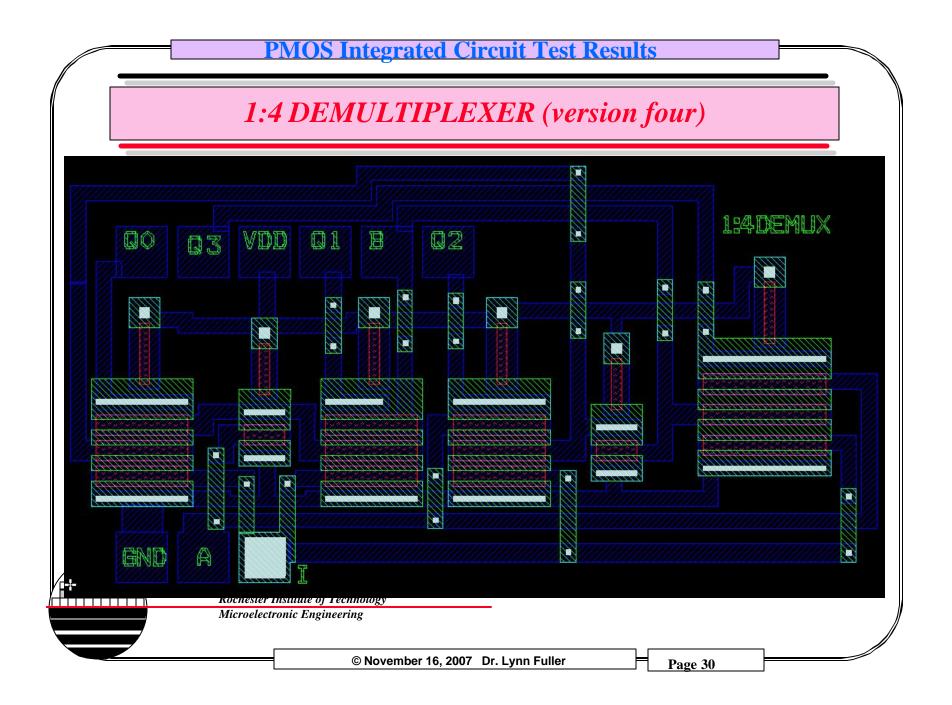

# **TEST RESULT 1:4 DEMULTIPLEXER (version four)**

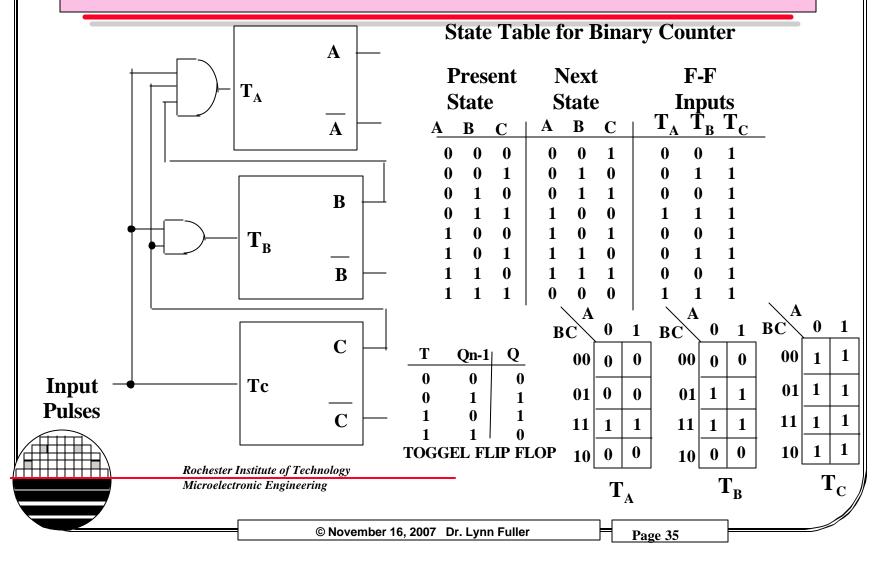

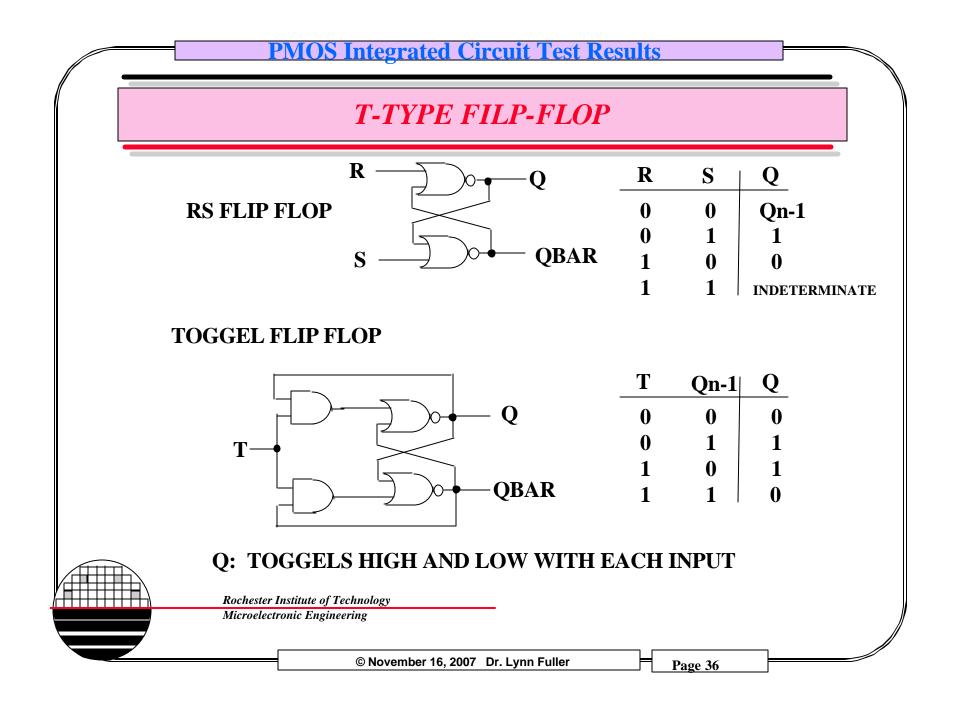

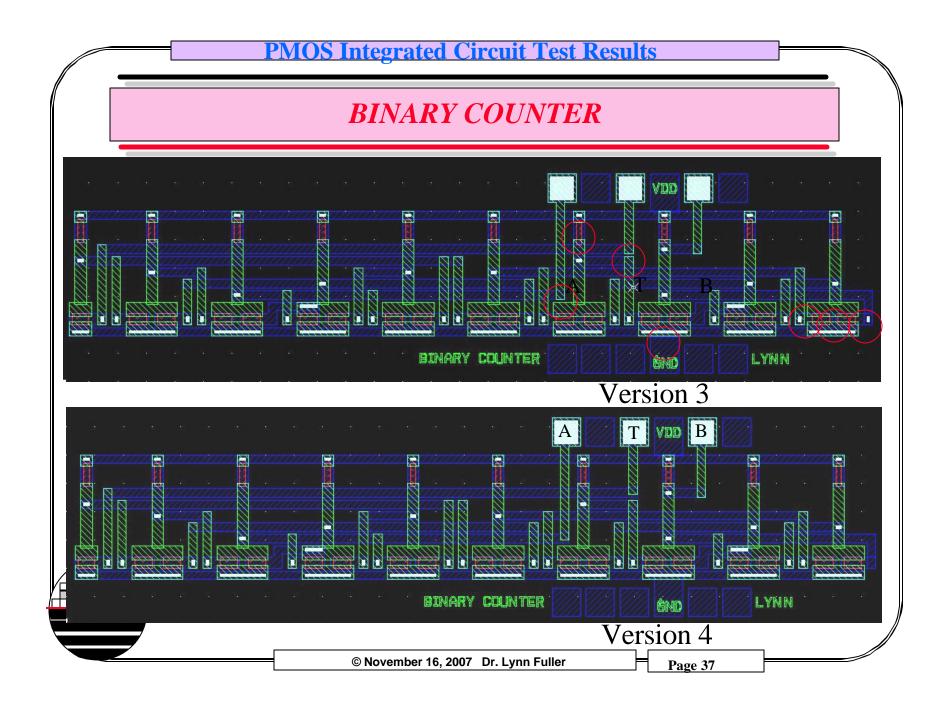

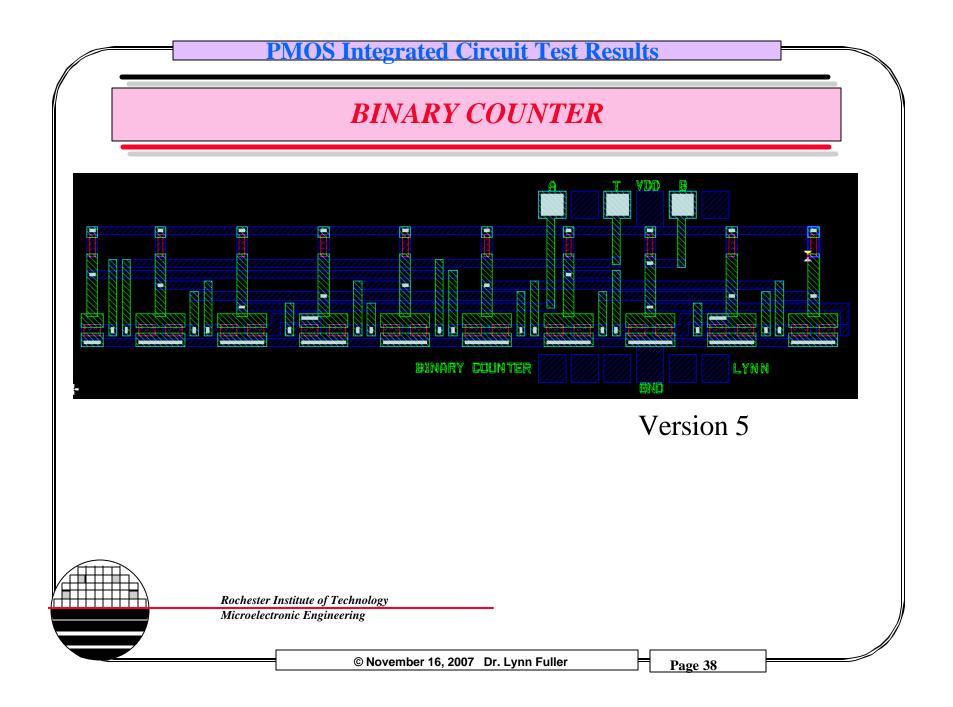

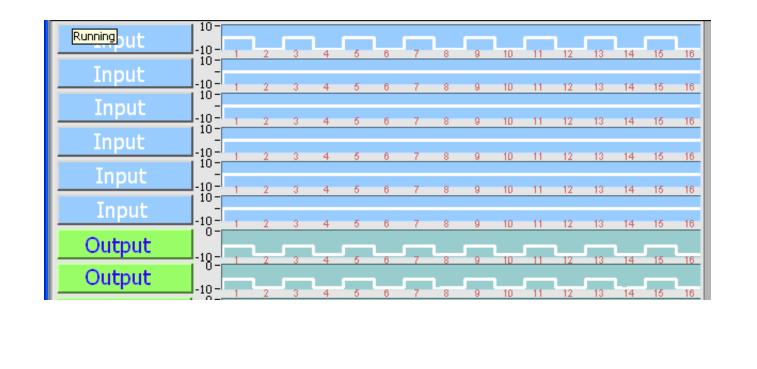

#### **BINARY COUNTER USING T TYPE FLIP FLOPS**

## **PMOS Integrated Circuit Test Results**

## **BINARY COUNTER VERSION 3**

Rochester Institute of Technology

Microelectronic Engineering

© November 16, 2007 Dr. Lynn Fuller

Page 39

PMOS Integrated Circuit Test Results

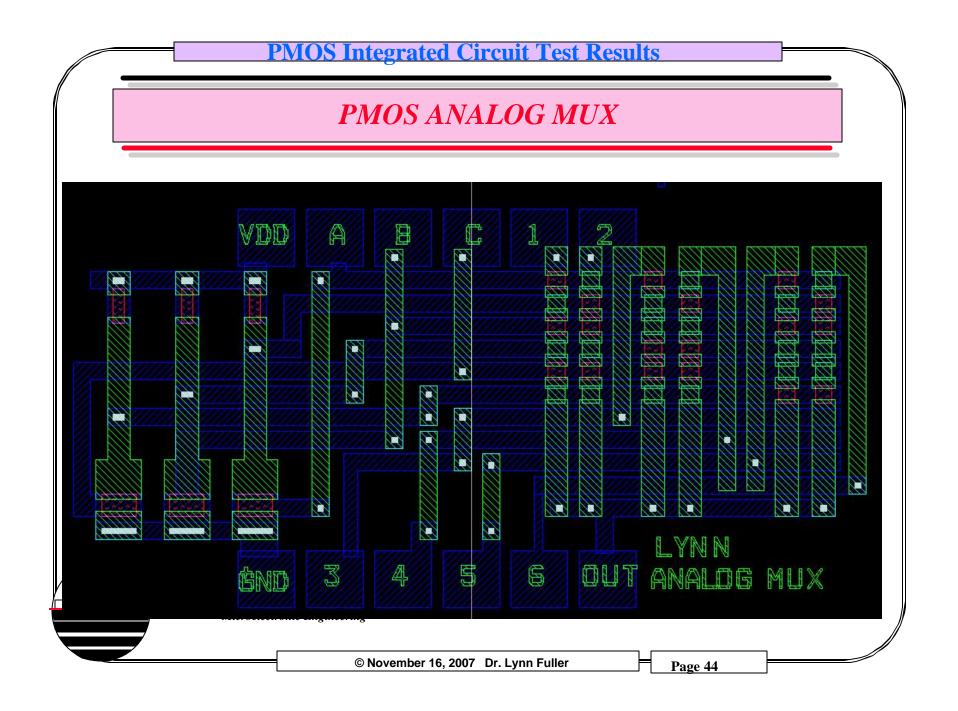

## **PMOS ANALOG MUX**

© November 16, 2007 Dr. Lynn Fuller

Page 45