Development of a Deep-Submicron CMOS Process for Fabrication of High Performance 0.25 mm Transistors

Michael Aquilino M.S. Thesis Defense Microelectronic Engineering Department Rochester Institute of Technology May 19, 2006

**Rochester Institute of Technology**

#### **Motivation**

- Enable the Microelectronic Engineering department to continue the semiconductor industry trend of fabricating high performance transistors that have faster switching speeds and increased density and functionality

- Push the limits of the SMFL in all areas from design to fabrication to test

- Create a baseline process that can be used to integrate strained silicon, metal gates, high-k gate dielectrics, and replacement gate technologies at RIT

# Outline

#### RIT/Industry Scaling Trends

- Gate Control Fundamentals

- Short Channel Effects

- Deep-Submicron Scaling

- Test Chip Layout

- Unit Process Development & Integration

- Electrical Results

- o Summary

- Questions

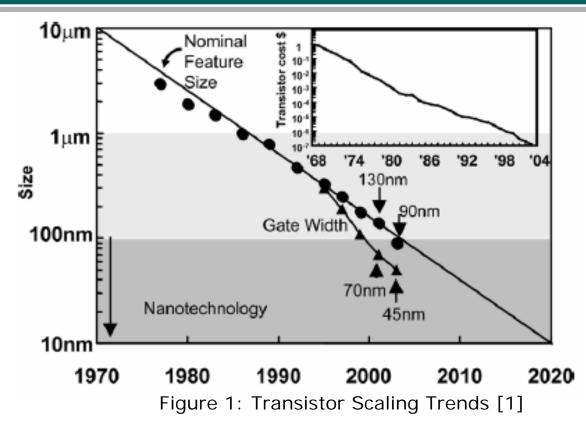

# **RIT/Industry Scaling Trends**

0.25 µm CMOS technology was used in high volume manufacturing of the Intel Pentium III up to 600 MHz through 1999

The gap between industry and RIT is rapidly shrinking

Rochester Institute of Technology Microelectronic Engineering

# **Gate Control Fundamentals**

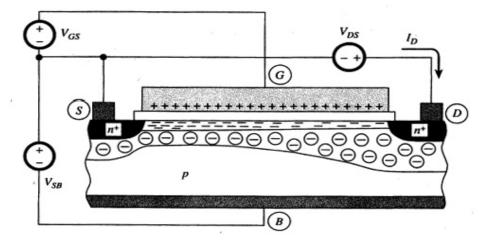

- NMOS Transistor

- o 4 Terminal Device

- Gate

- o Source

- o Drain

- o Body

Figure 2: Schematic of NMOS Transistor [2]

#### To turn transistor on:

- Apply positive charge to Gate, Q<sub>G</sub>

- A depletion region in the p-type body is created as positively charged holes are repelled by gate, exposing negatively charged acceptor ions, Q<sub>B</sub>

- $_{\rm 0}$  As the gate charge is further increased, electrons from the source diffuse into the channel and become inversion charge, Q\_I

$$O_{G} = O_{B} + O_{I}$$

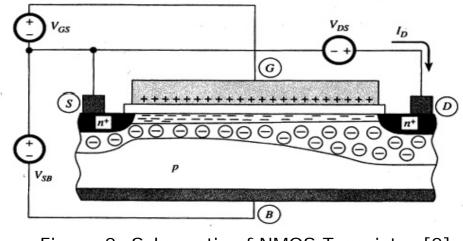

# **Gate Control Fundamentals**

- The source and body terminals are grounded

- A positive voltage is applied to the drain, V<sub>DS</sub>

- Inversion charge moves from source to drain and is the current in the device

Figure 2: Schematic of NMOS Transistor [2]

Equation 1 shows the classical derivation for drain current in a transistor by integrating the inversion charge along the channel

$$I_D = \frac{W}{L} \int_{VS}^{VD} \boldsymbol{m}_{l} Q_n(V) dV \qquad (Eq. 1)$$

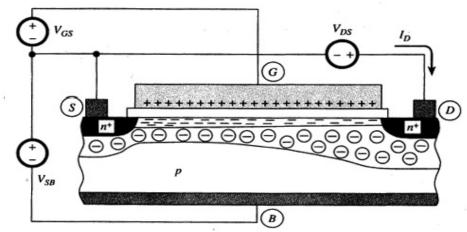

# **Gate Control Fundamentals**

- A depletion region from the drain is created by the reverse biased drain - body N<sup>+</sup>-P diode

- The positively charged donor ions in drain support some of the negative inversion charge

Figure 2: Schematic of NMOS Transistor [2]

- This is known as "Charge Sharing" as the gate does not have full control over the inversion channel

- For large gate lengths, the contribution of the drain in controlling the inversion layer is small compared to the gate contribution

- As transistors are scaled smaller in gate length, the drain has a larger percentage contribution in supporting inversion charge in the channel

Rochester Institute of Technology Microelectronic Engineering

# **Drain Induced Barrier Lowering**

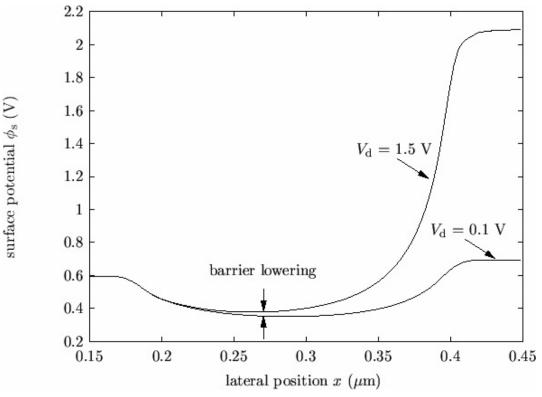

Figure 3: Surface Potential vs. Lateral Position in the Channel [3]

As the drain bias is increased the energy barrier in the channel is lowered

This is known as Drain Induced Barrier Lowering and is the cause of short channel effects <u>Rochester Institute of Technology</u> <u>Microelectronic Engineering</u>

#### Short Channel Effects

Log  $(I_{DS})$   $V_{DS} = 2.5 V$   $V_{DS} = 0.1 V$  $DIBL = \frac{\Delta V_{GS}}{\Delta V_{DS}}$

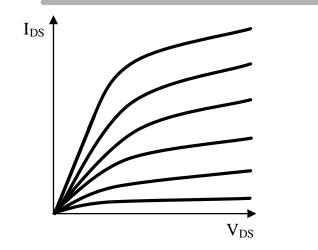

Figure 4: Channel Length Modulation

Figure 6:  $V_T$  Roll-Off

Rochester Institute of Technology Microelectronic Engineering

Figure 5: Increased Sub-threshold Current

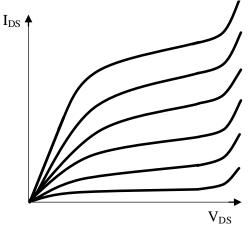

Figure 7: Source/Drain Punch through

• The goal in deep-submicron scaling is to maximize the gate control for switching the device on and off by scaling physical and electrical parameters, therefore reducing short channel effects

Table 2: 0.25 um Scaling Parameters from NTRS Roadman [4]

| Tuble 2. 0.25 µm Searing Faranceers nom Terris Roadinap [4] |              |                               |                                        |  |  |

|-------------------------------------------------------------|--------------|-------------------------------|----------------------------------------|--|--|

| I <sub>ON</sub>                                             | 600 µA/µm    | T <sub>ox</sub>               | 40 - 50 Å                              |  |  |

| I <sub>OFF</sub>                                            | 1 nA/µm      | X <sub>J</sub> (shallow LDD)  | 50 – 100 nm                            |  |  |

| $Log(I_{ON}/I_{OFF})$                                       | 5.75 decades | N <sub>D</sub> (LDD)          | $2 - 5 \times 10^{18} \text{ cm}^{-3}$ |  |  |

| SS                                                          | 85 mV/decade | $R_{S}(LDD)$                  | $400 - 850 \ \Omega/sq$                |  |  |

| DIBL                                                        | < 100  mV/V  | X <sub>J</sub> (contact)      | 135 – 265 nm                           |  |  |

| V <sub>DD</sub>                                             | 1.8 - 2.5 V  | N <sub>D</sub> (contact)      | $1 \times 10^{20} \text{ cm}^{-3}$     |  |  |

| V <sub>T</sub>                                              | 0.5 V        | X <sub>J</sub> (SSRW channel) | 50 – 100 nm                            |  |  |

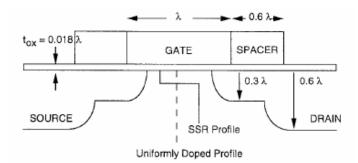

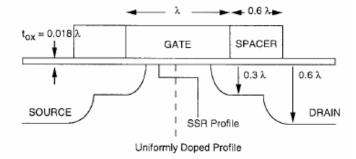

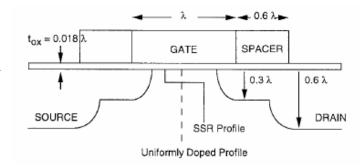

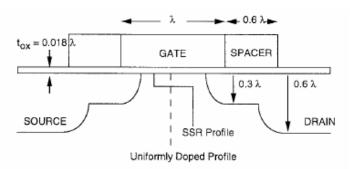

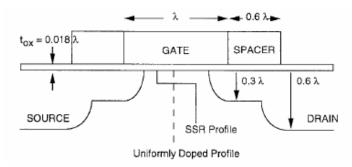

Figure 8: Physical Scaling Guidelines [5]

| Tuble 2. 0.25 µm Seaming Faranceers from TVTKS Roadmap [4] |              |                               |                                        |  |  |

|------------------------------------------------------------|--------------|-------------------------------|----------------------------------------|--|--|

| I <sub>ON</sub>                                            | 600 µA/µm    | T <sub>ox</sub>               | 40 - 50 Å                              |  |  |

| I <sub>OFF</sub>                                           | 1 nA/µm      | X <sub>J</sub> (shallow LDD)  | 50 – 100 nm                            |  |  |

| $Log(I_{ON} / I_{OFF})$                                    | 5.75 decades | $N_{D}$ (LDD)                 | $2 - 5 \times 10^{18} \text{ cm}^{-3}$ |  |  |

| SS                                                         | 85 mV/decade | $R_{S}(LDD)$                  | $400 - 850 \ \Omega/sq$                |  |  |

| DIBL                                                       | < 100  mV/V  | $X_J$ (contact)               | 135 – 265 nm                           |  |  |

| $V_{DD}$                                                   | 1.8 - 2.5 V  | N <sub>D</sub> (contact)      | $1 \times 10^{20} \text{ cm}^{-3}$     |  |  |

| V <sub>T</sub>                                             | 0.5 V        | X <sub>J</sub> (SSRW channel) | 50 – 100 nm                            |  |  |

Table 2: 0.25 µm Scaling Parameters from NTRS Roadmap [4]

- Decrease gate oxide thickness

- o Gate is closer to the channel

- More control in switching device off

$$_{o} C_{ox} \uparrow since C_{ox} = \epsilon A/t_{ox} \text{ or } C_{ox} = \Delta Q/\Delta V$$

$_{\rm O}$  I<sub>D</sub> and g<sub>m</sub>  $\uparrow$  since  $\propto$  C<sub>ox</sub>

Figure 8: Physical Scaling Guidelines [5]

| Table 2. 0.25 µm Scamg Parameters from NTKS Koaumap [4] |              |                               |                                        |  |  |

|---------------------------------------------------------|--------------|-------------------------------|----------------------------------------|--|--|

| I <sub>ON</sub>                                         | 600 µA/µm    | T <sub>ox</sub>               | 40 - 50 Å                              |  |  |

| I <sub>OFF</sub>                                        | 1 nA/µm      | $X_J$ (shallow LDD)           | 50 – 100 nm                            |  |  |

| $Log(I_{ON} / I_{OFF})$                                 | 5.75 decades | N <sub>D</sub> (LDD)          | $2 - 5 \times 10^{18} \text{ cm}^{-3}$ |  |  |

| SS                                                      | 85 mV/decade | R <sub>S</sub> (LDD)          | $400 - 850 \ \Omega/sq$                |  |  |

| DIBL                                                    | < 100  mV/V  | X <sub>J</sub> (contact)      | 135 – 265 nm                           |  |  |

| $V_{DD}$                                                | 1.8 - 2.5 V  | N <sub>D</sub> (contact)      | $1 \times 10^{20} \text{ cm}^{-3}$     |  |  |

| V <sub>T</sub>                                          | 0.5 V        | X <sub>J</sub> (SSRW channel) | 50 – 100 nm                            |  |  |

Table 2: 0.25 um Scaling Parameters from NTRS Roadman [4]

- Decrease junction depth of source/drain

- Depletion region from gate dominates depletion region from the drain

- Trade-off is sheet resistance  $\uparrow$  and  $I_{D} \downarrow$

- $_{\circ}$  N<sub>n</sub> must  $\uparrow$  which will cause R<sub>s</sub>  $\downarrow$

Figure 8: Physical Scaling Guidelines [5]

| Table 2: 0.25 µm Scaling Parameters from NTRS Roadmap [4] |              |                               |                                        |  |  |

|-----------------------------------------------------------|--------------|-------------------------------|----------------------------------------|--|--|

| I <sub>ON</sub>                                           | 600 µA/µm    | T <sub>ox</sub>               | 40 - 50 Å                              |  |  |

| I <sub>OFF</sub>                                          | 1 nA/µm      | X <sub>J</sub> (shallow LDD)  | 50 – 100 nm                            |  |  |

| $Log(I_{ON} / I_{OFF})$                                   | 5.75 decades | $N_{D}$ (LDD)                 | $2 - 5 \times 10^{18} \text{ cm}^{-3}$ |  |  |

| SS                                                        | 85 mV/decade | $R_{\rm S}(\rm LDD)$          | $400 - 850 \ \Omega/sq$                |  |  |

| DIBL                                                      | < 100  mV/V  | $X_{J}$ (contact)             | 135 – 265 nm                           |  |  |

| V <sub>DD</sub>                                           | 1.8 - 2.5 V  | N <sub>D</sub> (contact)      | $1 \times 10^{20} \text{ cm}^{-3}$     |  |  |

| V <sub>T</sub>                                            | 0.5 V        | X <sub>J</sub> (SSRW channel) | 50 – 100 nm                            |  |  |

- Use sidewall spacer to create deeper source/drain junction called the contact

- Typically ~2x as deep as shallow LDD

- Doped heavily to reduce R<sub>s</sub>

Figure 8: Physical Scaling Guidelines [5]

| Table 2: 0.25 µm Scaling Parameters from NTRS Roadmap [4] |              |                               |                                        |  |  |

|-----------------------------------------------------------|--------------|-------------------------------|----------------------------------------|--|--|

| I <sub>ON</sub>                                           | 600 µA/µm    | T <sub>ox</sub>               | 40 - 50 Å                              |  |  |

| I <sub>OFF</sub>                                          | 1 nA/µm      | $X_J$ (shallow LDD)           | 50 – 100 nm                            |  |  |

| $Log(I_{ON} / I_{OFF})$                                   | 5.75 decades | N <sub>D</sub> (LDD)          | $2 - 5 \times 10^{18} \text{ cm}^{-3}$ |  |  |

| SS                                                        | 85 mV/decade | $R_{S}(LDD)$                  | $400 - 850 \ \Omega/sq$                |  |  |

| DIBL                                                      | < 100  mV/V  | X <sub>J</sub> (contact)      | 135 – 265 nm                           |  |  |

| V <sub>DD</sub>                                           | 1.8 – 2.5 V  | N <sub>D</sub> (contact)      | $1 \times 10^{20} \text{ cm}^{-3}$     |  |  |

| V <sub>T</sub>                                            | 0.5 V        | X <sub>J</sub> (SSRW channel) | 50 – 100 nm                            |  |  |

- Decrease V<sub>DD</sub> to reduce depletion region from the drain and prevent lateral and vertical punch-through

- Increase doping of channel to decrease the depletion region from the source/drain

- Use a retrograde profile where doping is low at the surface and higher sub-surface

- Mobility of carriers ↑

Figure 8: Physical Scaling Guidelines [5]

| Table 2. 0.25 µm Scanng Faranielers from NTKS Koaumap [4] |              |                                  |                                           |  |  |

|-----------------------------------------------------------|--------------|----------------------------------|-------------------------------------------|--|--|

| I <sub>ON</sub>                                           | 600 µA/µm    | T <sub>ox</sub>                  | 40 - 50 Å                                 |  |  |

| I <sub>OFF</sub>                                          | 1 nA/µm      | $\overline{X}_{J}$ (shallow LDD) | 50 – 100 nm                               |  |  |

| $Log(I_{ON} / I_{OFF})$                                   | 5.75 decades | N <sub>D</sub> (LDD)             | $2 - 5 \text{ x} 10^{18} \text{ cm}^{-3}$ |  |  |

| SS                                                        | 85 mV/decade | $R_{S}(LDD)$                     | $400 - 850 \Omega/sq$                     |  |  |

| DIBL                                                      | < 100 mV/V   | $X_J$ (contact)                  | 135 – 265 nm                              |  |  |

| V <sub>DD</sub>                                           | 1.8 – 2.5 V  | N <sub>D</sub> (contact)         | $1 \times 10^{20} \text{ cm}^{-3}$        |  |  |

|                                                           | 0.5 V        | X <sub>J</sub> (SSRW channel)    | 50 – 100 nm                               |  |  |

Table 2: 0.25 um Scaling Parameters from NTRS Roadman [4]

- As  $T_{OX} \downarrow$ , gate leakage current  $\uparrow$  as  $V_{GS-MAX} = V_{DD}$

- $\circ$  V<sub>GS</sub> must  $\downarrow$  to reduce this leakage

- $V_T$  must  $\downarrow$  so  $(V_{GS}-V_T)$   $\uparrow$ , this is "Gate Overdrive" and is  $\propto I_D$ • Want  $I_{ON}$   $\uparrow$  since gate delay  $\propto I_{ON}^{-1}$

$$t = \frac{CV}{I_{ON}}$$

(Eq. 2)

| Table 2. 0.25 µm Scanng Faranielers from NTKS Koaumap [4] |              |                               |                                        |  |  |

|-----------------------------------------------------------|--------------|-------------------------------|----------------------------------------|--|--|

| I <sub>ON</sub>                                           | 600 µA/µm    | T <sub>ox</sub>               | 40 - 50 Å                              |  |  |

| I <sub>OFF</sub>                                          | 1 nA/µm      | X <sub>J</sub> (shallow LDD)  | 50 – 100 nm                            |  |  |

| $Log(I_{ON}/I_{OFF})$                                     | 5.75 decades | N <sub>D</sub> (LDD)          | $2 - 5 \times 10^{18} \text{ cm}^{-3}$ |  |  |

| SS                                                        | 85 mV/decade | $R_{S}(LDD)$                  | $400 - 850 \ \Omega/sq$                |  |  |

| DIBL                                                      | < 100  mV/V  | $X_J$ (contact)               | 135 – 265 nm                           |  |  |

| $V_{DD}$                                                  | 1.8 - 2.5 V  | N <sub>D</sub> (contact)      | $1 \times 10^{20} \text{ cm}^{-3}$     |  |  |

| V <sub>T</sub>                                            | 0.5 V        | X <sub>J</sub> (SSRW channel) | 50 – 100 nm                            |  |  |

Table 2: 0.25 um Scaling Parameters from NTRS Roadman [4]

• Want I<sub>OFF</sub> to be low to reduce standby power

- The industry standard metric is 1 nA/µm of off-current

- $_{\rm o}$  This results in 5.75 decades between I<sub>ON</sub> and I<sub>OFF</sub>

- $_{\circ}$  There is 500 mV swing between 0 V and V<sub>T</sub>

SS of 85 mV/decade is needed to turn the device off

$$SS = \frac{KT}{q} \times \ln(10) \times \left[1 + \frac{C_D}{C_{OX}}\right]$$

(Eq. 3) Theoretical limit ~ 60 mV/decade

@ 300K

**Rochester Institute of Technology** Microelectronic Engineering

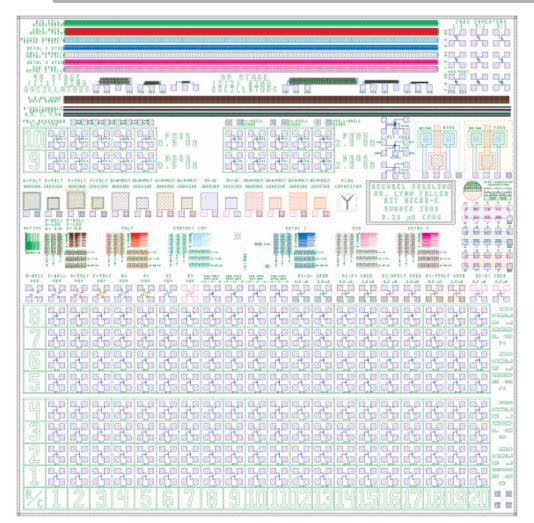

# Layout of Test Chip

- 0 9 Design Layers

- o Active

- o N-Well

- o Poly

- o N<sup>+</sup> Select

- o P<sup>+</sup> Select

- o Contact Cut

- o Metal 1

- o Via

- o Metal 2

- 0 10 Masks

- 0 12 Lithography Levels

Figure 9: Test Chip Layout

**Rochester Institute of Technology**

# Layout of Test Chip

- 0 9 Design Layers

- o Active

- o N-Well

- o Poly

- o N<sup>+</sup> Select

- o P<sup>+</sup> Select

- o Contact Cut

- o Metal 1

- o Via

- o Metal 2

- 0 10 Masks

- o 12 Lithography Levels

Figure 9: Test Chip Layout

**Rochester Institute of Technology**

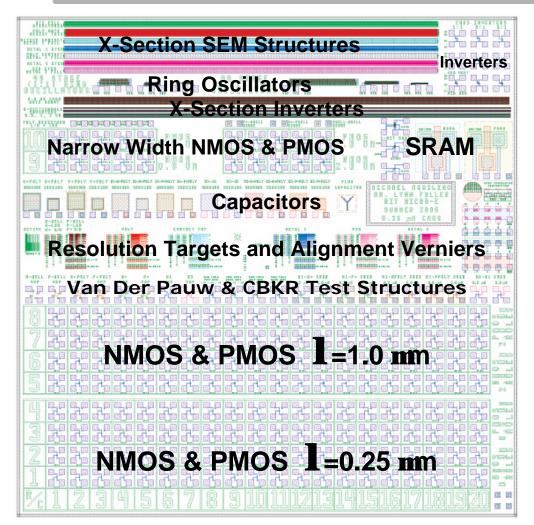

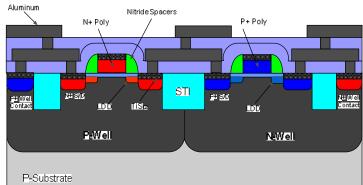

# 0.25 µm Device Technology

Figure 10: CMOS Inverter Cross Section showing NMOS (left) and PMOS (right) Transistors

- o Shallow Trench Isolation

- o 50 Å gate oxide w/  $N_2O$

- o Polysilicon Reactive Ion Etch

- o Arsenic/BF<sub>2</sub> Low Doped SDE

- o Si<sub>3</sub>N<sub>4</sub> Sidewall Spacers

- o Dual Doped Poly Gates

- o Rapid Thermal Dopant Activation

- o Titanium Silicide

- o Contact Cut Plasma Etch

- o 2 Level Aluminum Metallization

# **RIE Trench Etch with Photoresist**

Figure 11: RIE of Silicon Trenches

- o Target silicon trench depth is 4000 Å

- o Photoresist is causing footing at bottom of trench towards the end of etch

- o Need to increase hard bake temp to 140°C from 110°C

- o Trenches as small as 0.5 µm wide can be etched

- o 500 Å liner oxide thermally grown to repair damage to sidewalls of trench and round off the corners at the bottom for better TEOS filling

**Rochester Institute of Technology**

# **Uniformly Doped Twin Well**

|                                                | NMOS                 | PMOS                 | NMOS<br>Field        | PMOS<br>Field        |

|------------------------------------------------|----------------------|----------------------|----------------------|----------------------|

| Well Type                                      | р                    | n                    | р                    | n                    |

| Gate Material                                  | N+ Poly              | P+ Poly              | N+ Poly              | P <sup>+</sup> Poly  |

| Doping<br>Concentration<br>(cm <sup>-3</sup> ) | 6.5x10 <sup>17</sup> | 5.5x10 <sup>17</sup> | 6.5x10 <sup>17</sup> | 5.5x10 <sup>17</sup> |

| Junction Depth<br>(µm)                         | 3                    | 3                    | 3                    | 3                    |

| Gate Oxide<br>(Å)                              | 50                   | 50                   | 4000                 | 4000                 |

| Threshold<br>Voltage<br>(V)                    | + 0.5 V              | - 0.5 V              | + 50 V               | - 50 V               |

Figure 12: Twin Well Doping

o N & P Well implanted after the liner oxide before the STI TEOS fill o Well Drive in for 6 hours @  $1100^{\circ}$ C in N<sub>2</sub>

o The junction depth of the wells must be large enough to prevent vertical punch-through between the reverse-biased drain of the PMOS and the starting wafer Rochester Institute of Technology 21

# 7000 Å Trench Fill with PECVD TEOS

Recipe Parameters: Name = A6-7000A TEOS LS Power = 295 W Pressure = 9000 mTorr TEOS = 400 sccm  $O_2$  = 285 sccm Temp = 390°C

Figure 13: Shallow Trench After TEOS Deposition

o Trenches filled with 7000 Å PECVD TEOS in Applied Materials P-5000

o 4000 Å Si + 500 Å Pad Ox + 1500 Å Nitride + 1000 Å overfill = 7000 Å

o CMP is used to polish TEOS off active areas using nitride as stop layer

**Rochester Institute of Technology**

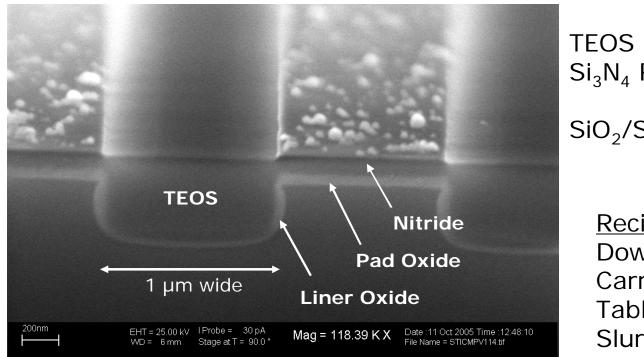

## Shallow Trench Isolation After CMP

TEOS Removal = 1574 Å/min Si<sub>3</sub>N<sub>4</sub> Removal = 407 Å/min

$SiO_2/Si_3N_4$  Selectivity = 3.87

Recipe Parameters: Down Force = 6 PSI Carrier = 70 RPM Table = 50 RPM Slurry = 60 mL/min

Figure 14: 1 µm Shallow Trench After CMP

o Nitride protects the active areas where the transistors will be built

o After cleans, a TEOS densification is done to lower TEOS etch rate in HF

o Nitride and Pad Oxide removed so 50 Å gate oxide can be grown Rochester Institute of Technology

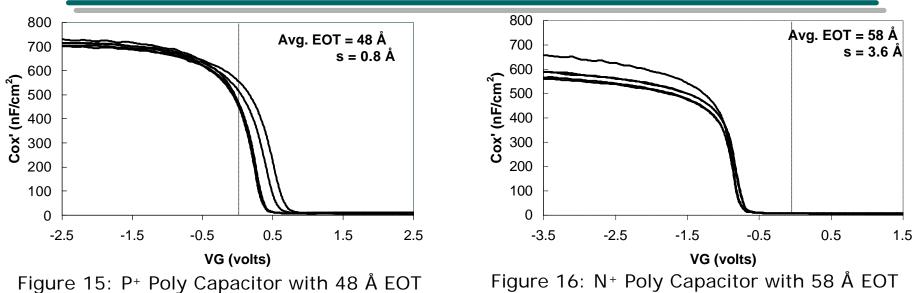

#### C-V Analysis of P<sup>+</sup>/N<sup>+</sup> Poly Capacitors

- Nitrogen is incorporated into the gate oxide from N<sub>2</sub>O gas to prevent boron from diffusing from P<sup>+</sup> poly into the channel during the source/drain anneal

- o 50 Å gate oxide measured with Variable Angle Spectroscopic Ellipsometer

- o P<sup>+</sup> poly capacitors exhibit no poly depletion with average EOT = 48 Å

o N<sup>+</sup> poly capacitors exhibit some poly depletion with average EOT = 58 Å

# Photoresist Trimming for 0.25 µm Gate Length

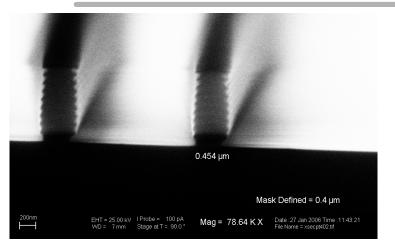

Figure 17: 0.45  $\mu m$  PR Line Before Trim

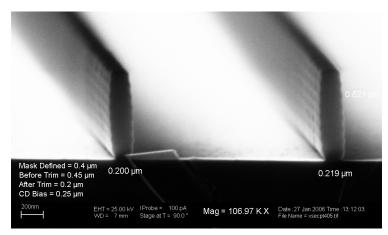

Figure 18: 0.2 µm PR Line After Trim

o Resolution limit of Canon i-line stepper ~ 0.5  $\mu m$

o 1250 Å of PR is etched off each side of 0.5  $\mu$ m PR lines in O<sub>2</sub> plasma to make 0.25  $\mu$ m lines

<u>Recipe Parameters:</u> Power = 100 W Pressure = 400 mTorr  $O_2 = 20$  sccm Gap = 1.65 cm Tool = LAM490

o PR Horizontal Etch Rate = 555 Å/min o PR Vertical Etch Rate = 720 Å/min o Anisotropy =  $(1-ER_H/ER_V) = 0.23$

Rochester Institute of Technology Microelectronic Engineering

# **Polysilicon Reactive Ion Etch**

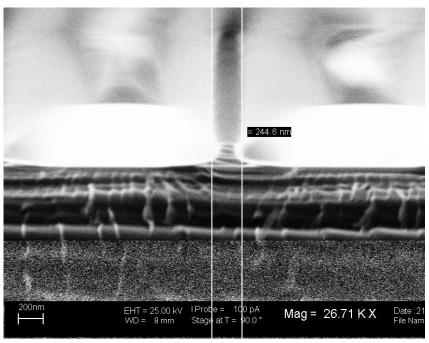

Figure 19: 0.25 µm Poly Gate Length

Poly Etch Rate = 336 Å/min  $SiO_2$  Etch Rate = 70 Å/min

$Poly/SiO_2$  Selectivity = 4.8

Recipe Parameters: Power = 200 W Pressure = 30 mTorr  $SF_6 = 10$  sccm  $CHF_3 = 35$  sccm  $O_2 = 5$  sccm Drytek Quad - Chamber 2

o 0.25 µm PR lines are transferred into 2000 Å LPCVD polysilicon layer

o 75° sidewall angle with RIE recipe

o < 90° angle reduces crossectional area of gate:  $R_{Gate}$  - , switching speed <sup>-</sup>

# **Poly Re-Oxidation**

o After plasma etch of gate there is damage to edges of gate oxide

o A 100 Å oxide is thermally grown to:

o Repair damage to edges of gate oxide from plasma etch of the poly gate

Create a thicker screening oxide for source/drain extension implant

Make a thicker etch stop for sidewall spacer etch process

Figure 20: Poly Re-Oxidaiton

o Form an off-set region for lateral diffusion of shallow s/d extension

o Want to reduce gate overlap of s/d to reduce Miller Capacitance

o This capacitance will reduce the cut-off frequency of the device

Need 15 – 20 nm of gate overlap for proper capacitive coupling of the gate to the channel or drive current will degrade [6]

**Rochester Institute of Technology**

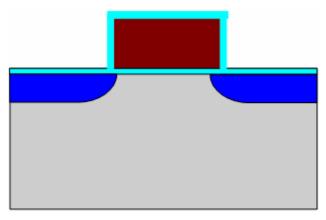

## As/BF<sub>2</sub> Low Doped S/D Extensions

o Low energy BF<sub>2</sub> and Arsenic ions are implanted for shallow junctions self aligned to the poly gate

Figure 21: Effective Channel Length Estimation

o Gate Overlap = 50 nm - 10 nm = 40 nm = 15 - 20 nm requirement

o L<sub>EFFECTIVE</sub> will be extracted to be between L<sub>POLY</sub> and L<sub>Metallurgical</sub>

o Process is designed for  $L_{POLY} = 0.25 \ \mu m$  and  $L_{EFFECTIVE} = 0.20 \ \mu m$ <u>Rochester Institute of Technology</u> <u>Microelectronic Engineering</u>

28

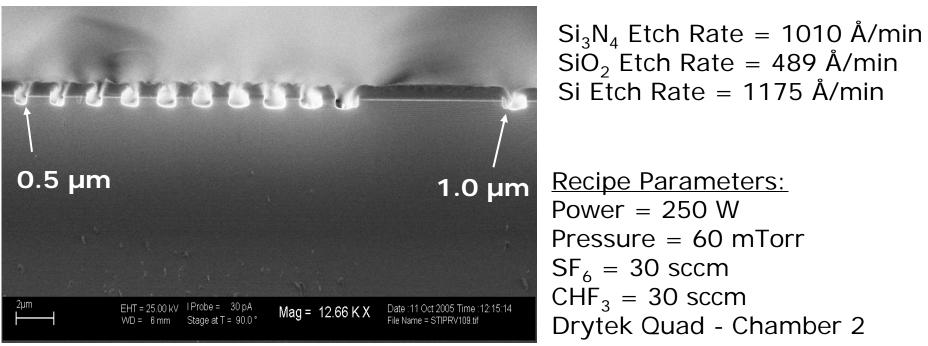

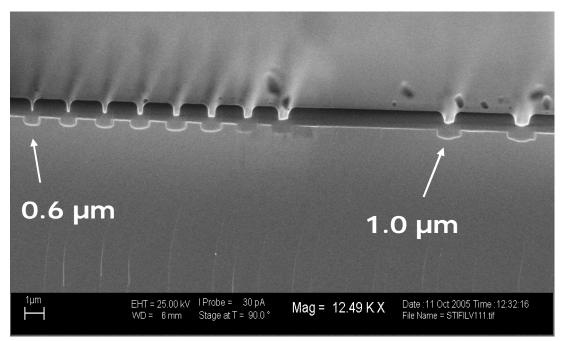

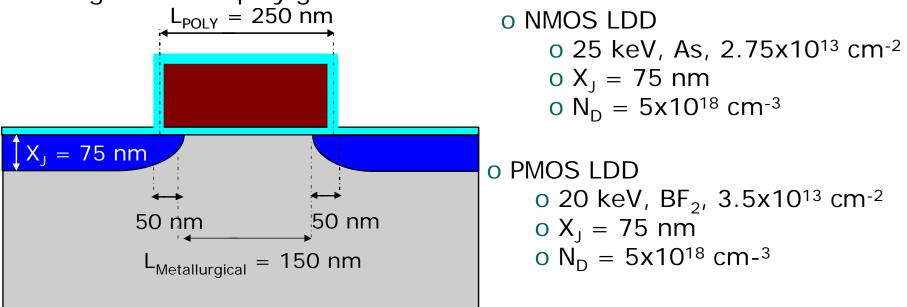

# Silicon Nitride Sidewall Spacers

Rochester Institute of Technology

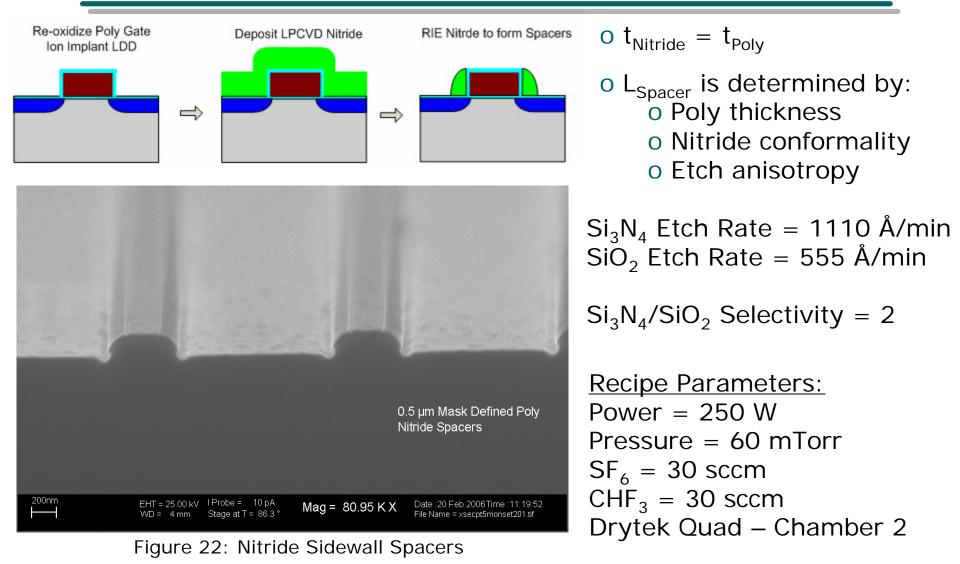

# As/BF<sub>2</sub> Source/Drain & Poly Contact Implant

o High dose  $BF_2$  and Arsenic ions are implanted at higher energies for the deeper source/drain contacts that are self aligned to the spacers

Figure 23: S/D Contact & Poly Doping

o Poly Gates doped at the same time as the source/drain contact implants

o N<sup>+</sup> Poly for NMOS and P<sup>+</sup> Poly for PMOS for surface channel devices

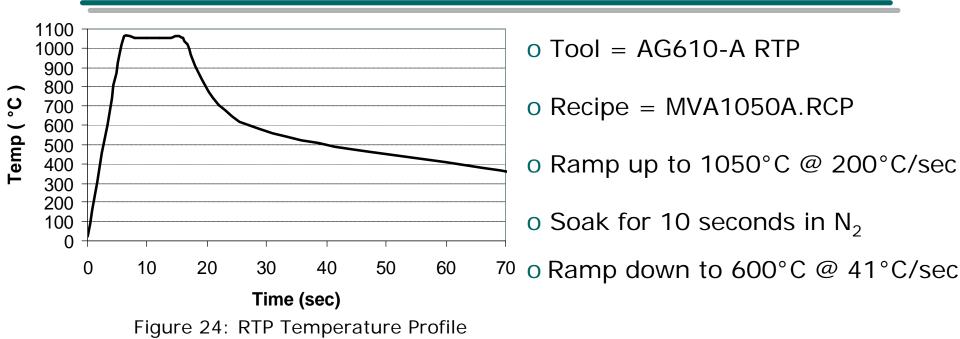

#### **Rapid Thermal Dopant Activation**

- A high temperature thermal step is required for dopant activation and to repair damage to the silicon lattice caused by the high dose S/D implants

- o Rapid Thermal Processor needed to avoid TED temp ranges (670–900°C) [7]

- o Arsenic not as susceptible to Transient Enhanced Diffusion compared to BF<sub>2</sub>

Rochester Institute of Technology

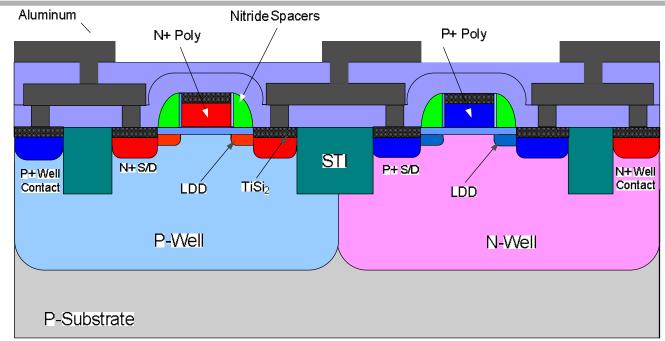

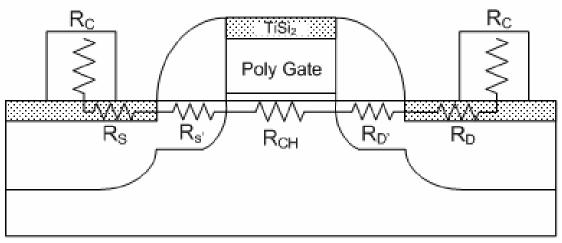

# Self Aligned Titanium Silicide (TiSi<sub>2</sub>)

Figure 25: TiSi<sub>2</sub> for Low Contact Resistance to Source & Drain

- o Two-step silicide process to reduce R<sub>s</sub> and R<sub>D</sub>

- o Higher resistivity C49 Phase 30 seconds @ 715°C in N<sub>2</sub>

- o Etch un-reacted Titanium in 2:1  $H_2O_2$ :  $H_2SO_4$

- o Lower resistivity C54 Phase 20 seconds @ 850°C in N<sub>2</sub>

|                                    | After S/D Anneal | After RTP-1 & Ti etch | After RTP-2 |

|------------------------------------|------------------|-----------------------|-------------|

| Average Sheet<br>Resistance (Ω/sq) | 45               | 12.86                 | 1.66        |

**Rochester Institute of Technology**

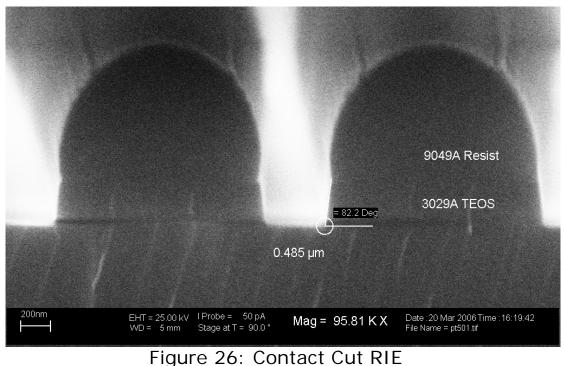

#### **Contact Cut Reactive Ion Etch**

$SiO_2$  Etch Rate = 1850 Å/min Si Etch Rate = 320 Å/min

$SiO_2/Si$  Selectivity = 5.78

<u>Recipe Parameters:</u> Applied Materials P-5000 Recipe = C6 – Oxide Etch Power = 650 W Pressure = 250 mTorr  $CHF_3 = 100$  sccm  $CF_4 = 50$  sccm B = 40 Gauss

o 0.5 µm contact cuts etched in 3000 Å of TEOS

o 82° Sidewall Angle with RIE recipe

**Rochester Institute of Technology**

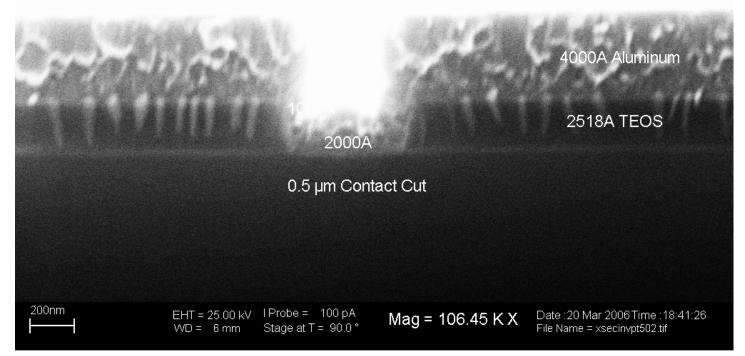

# **Aluminum Metallization**

Figure 27: 0.5 µm Contact Cuts After Metal 1

o 0.5  $\mu m$  contact cuts are filled with 5000 Å of Aluminum

o Smaller areas are more difficult to fill

o Back End CMP, Via and Metal 2 processes still need characterization

Rochester Institute of Technology Microelectronic Engineering

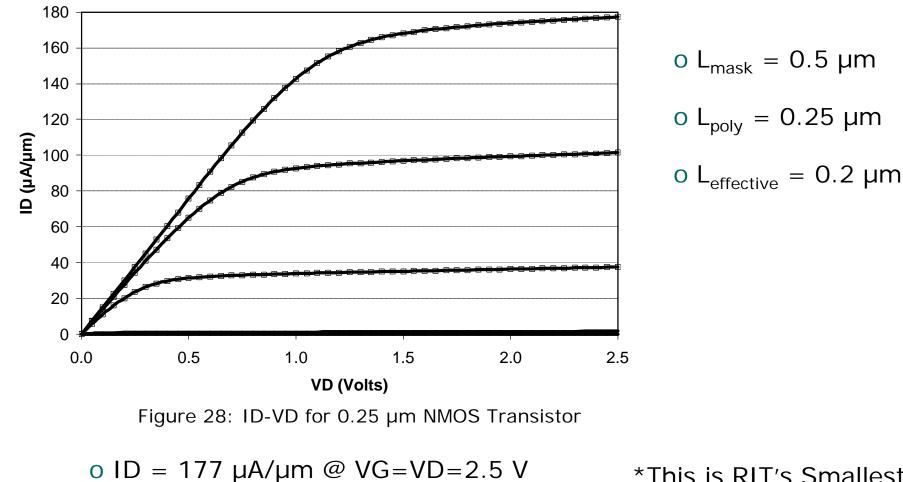

#### ID-VD for 0.25 µm NMOS Transistor

\*This is RIT's Smallest NMOS Transistor

Microelectronic Engineering

$O V_{T} = 1.0 V$

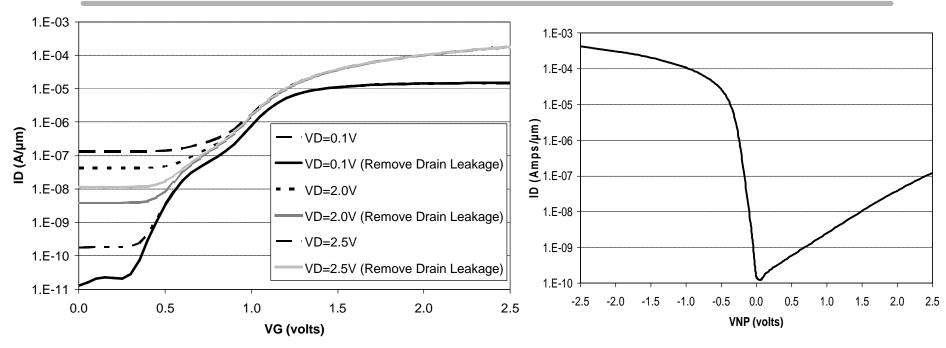

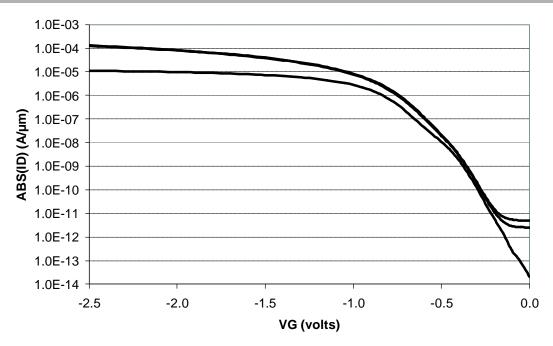

#### ID-VG Sub-threshold 0.25 µm NMOS

Figure 29: ID-VG for 0.25 µm NMOS Transistor

o  $I_{off} = 13 \text{ pA/}\mu\text{m} @ \text{VD}=0.1 \text{ V}$  (with drain diode leakage removed) o  $I_{off} = 11 \text{ nA/}\mu\text{m} @ \text{VD}=2.5 \text{ V}$  (with drain diode leakage removed) o  $\text{Log}(I_{on}/I_{off}) = 4.2 \text{ decades}$ o SS = 119 mV/decade @ VD=0.1 V

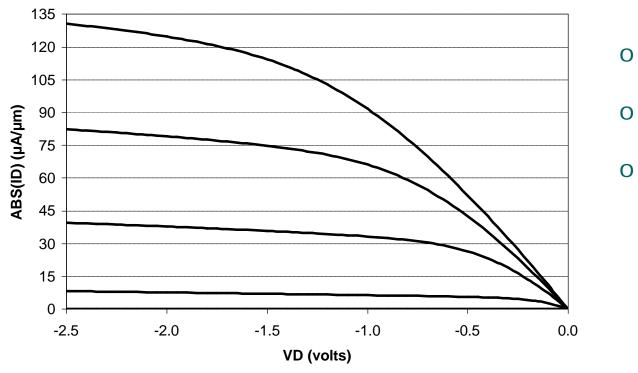

#### ID-VD for 0.25 µm PMOS Transistor

$$D L_{mask} = 0.6 \ \mu m$$

$$o L_{poly} = 0.25 \ \mu m$$

o  $L_{effective} = 0.2 \ \mu m$

\*This is RIT's Smallest PMOS Transistor

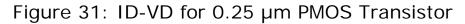

#### ID-VG Sub-threshold 0.25 µm PMOS

Figure 32: ID-VG for 0.25 µm PMOS Transistor

o  $I_{off} = -20 \text{ fA}/\mu\text{m} @ \text{VD}=-0.1 \text{ V}$ o  $I_{off} = -4.9 \text{ pA}/\mu\text{m} @ \text{VD}=-2.5 \text{ V}$ o  $\text{Log}(I_{on}/I_{off}) = 7.4 \text{ decades}$  o SS = 75 mV/decade @ VD=-0.1 V

o SS = 85 mV/decade @ VD=-2.5 V

o DIBL = 8.3 mV/V @ ID=-1 nA/μm

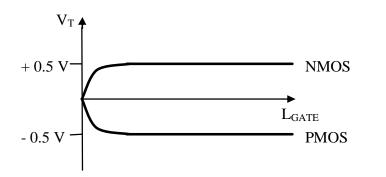

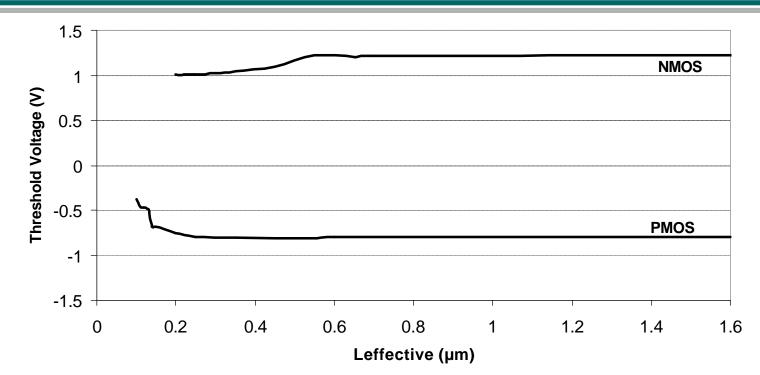

# $V_T$ Roll-Off

Figure 33: Threshold Voltage Roll-off Short Channel Effect

o As the gate length decreases,  $V_T$  decreases in magnitude

o For small enough  $L_{effective}$ , the  $V_T$ 's can decrease to 0 V

o Energy barrier lowering from drain so severe, the devices are on at V<sub>G</sub>=0 V <u>Rochester Institute of Technology</u> <u>Microelectronic Engineering</u>

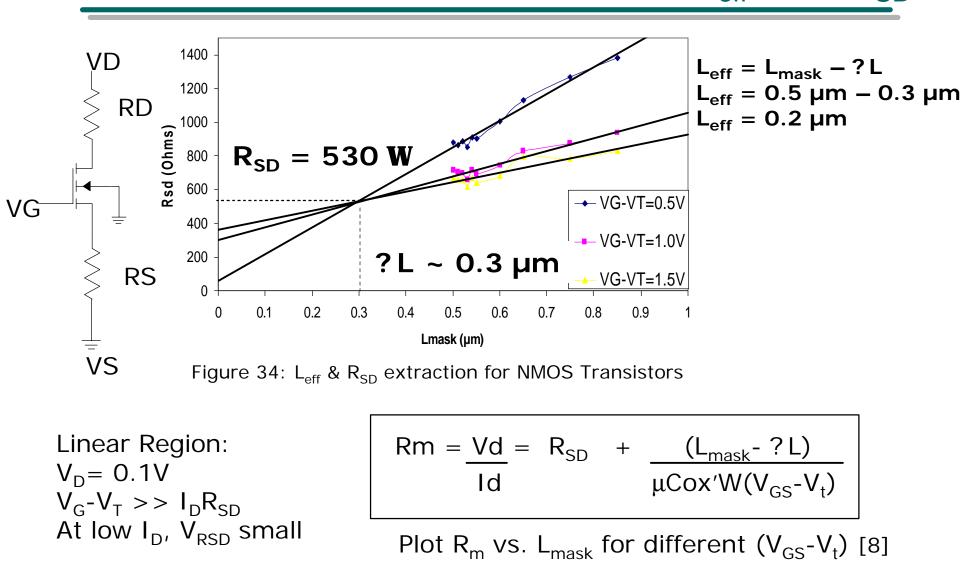

#### NMOS Terada-Muta Method for L<sub>eff</sub> and R<sub>SD</sub>

**Rochester Institute of Technology**

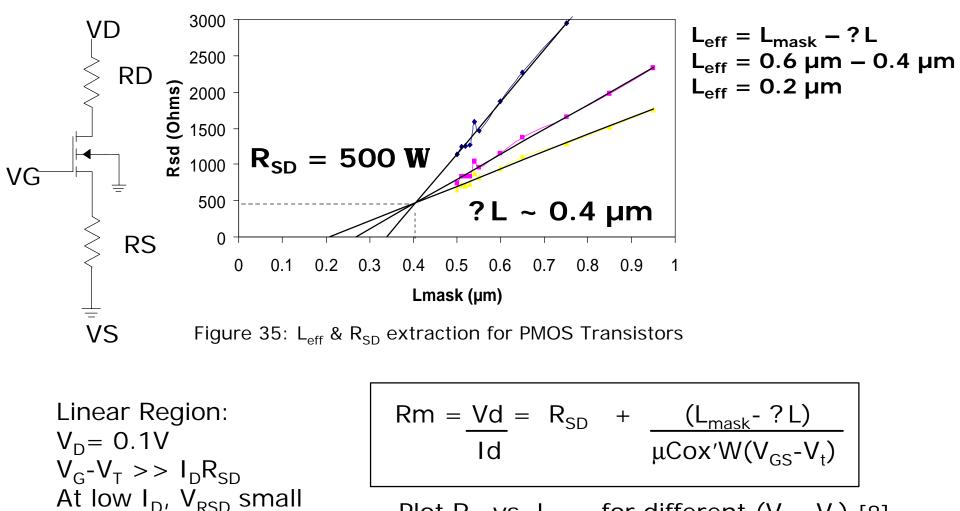

#### PMOS Terada-Muta Method for L<sub>eff</sub> and R<sub>SD</sub>

Plot  $R_m$  vs.  $L_{mask}$  for different ( $V_{GS}$ - $V_t$ ) [8]

Rochester Institute of Technology Microelectronic Engineering

#### Summary

o Unit Processes have been developed to achieve 0.25 µm CMOS Transistors

- o The unit processes have been integrated into a 75-step CMOS process flow

- o Fabrication has been completed and transistors characterized

- o This process can be improved upon for increased transistor performance as well as integrating high-k and strained silicon technologies in the future

#### Acknowledgements

I would like to thank the following people for their advisement and support in this work and throughout my 6 years at RIT:

- o Dr. Lynn Fuller o Dr. Santosh Kurinec

- o Dr. Karl Hirschman

(M.S. Thesis Advisor) (Committee Member) (Committee Member)

o MicroE Faculty & Staff

- o Dr. Sean Rommel

- o Dr. Michael Jackson

- o Dr. Bruce Smith

- o Dr. Robert Pearson

- o Prof. Dale Ewbank

- o Sara Widlund

- o SMFL Staff

- o Bruce Tolleson

- o Dave Yackoff

- o Sean O'Brien

- o Scott Blondell

- o Tom Grimsley

- o Rich Battaglia

- o John Nash

- o Graduate Students

- o Dan Jaeger

- o Reinaldo Vega

- o Eric Woodard

- o Mike Latham

- o Rob Manley

- o Germain Fenger

#### References

[1] S. E. Thompson, et al., "A 90-nm logic technology featuring strained-silicon," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1790-1797, 2004.

[2] Y. Tsividis. *Operation and Modeling of The MOS Transistor, 2nd Edition.* Oxford University Press, 1999.

[3] Michael Stockinger, <u>http://www.iue.tuwien.ac.at/phd/stockinger/node15.html</u>

[4] L. Wilson, ed., "The National Technology Roadmap for Semiconductors: 1997 Edition", Semiconductor Industry Association, San Jose, California

[5] De, I.; Osburn, C.M., "Impact of super-steep-retrograde channel doping profiles on the performance of scaled devices," *IEEE Trans. Electron Devices*, vol. 46, Issue: 8, pp.1711 - 1717, Aug. 1999

[6] S. Thompson, P. Packan, M. Bohr, "MOS Scaling: Transistor Challenges for the 21st Century", *Intel Technology Journal*, 1998

[7] S. Wolf. Silicon Processing for the VLSI Era. Volume 4-Deep Submicron Process Technology. Lattice Press, 2002

[8] K. Terada and H. Muta, "A new method to determine effective MOSFET channel length," Jpm. J. Appl. Phys., vol. 18, p. 935, 1979.

**Rochester Institute of Technology**