ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

# Introduction to ASML PAS 5500 Wafer Alignment and Exposure

# Dr. Lynn Fuller Stephanie Bolster

Webpage: <a href="http://people.rit.edu/lffeee">http://people.rit.edu/lffeee</a>

Electrical and Microelectronic Engineering

Rochester Institute of Technology

82 Lomb Memorial Drive

Rochester, NY 14623-5604

Tel (585) 475-2035

Email: Lynn.Fuller@rit.edu

Department Webpage: http://www.microe.rit.edu

Revision Date: 4-28-2014 Lithography-ASML.PPT

© April 28, 2014 Dr. Lynn Fuller

Page 1

Lithography Using ASML Stepper

# **DEFINITIONS**

**ASML** (today) – ASM Lithography (1988) – ASM International and Royal Phillips (1984)

**PAS** – Phillips Automatic Stepper as in ASML PAS 5500/200 **Reticle** – quartz plate with single layer of chip layout (or array) at

5X actual size (also called photomask)

PM – primary marks (same design for mask and wafer alignment)

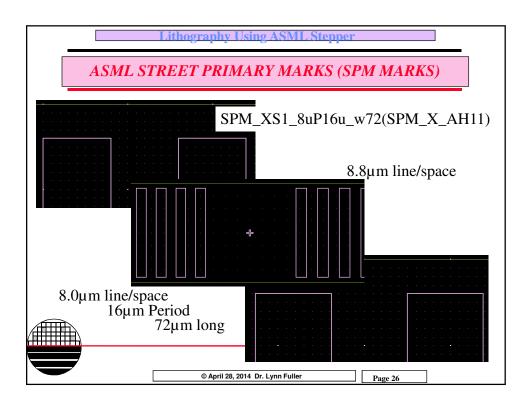

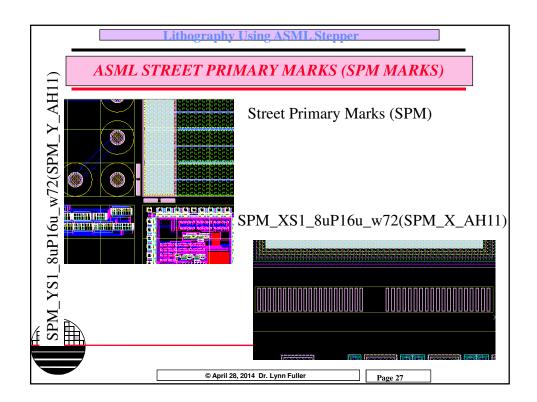

**SPM** – scribe line primary marks

**NA-** numerical aperture

$\sigma$  - sigma or coherency

**DOF** – depth of focus

**REMA** –Reticle Masking System

© April 28, 2014 Dr. Lynn Fuller

#### **OUTLINE**

Introduction

PAS 5500 Specifications

Stage Accuracy

Reticle Specifications and Alignment

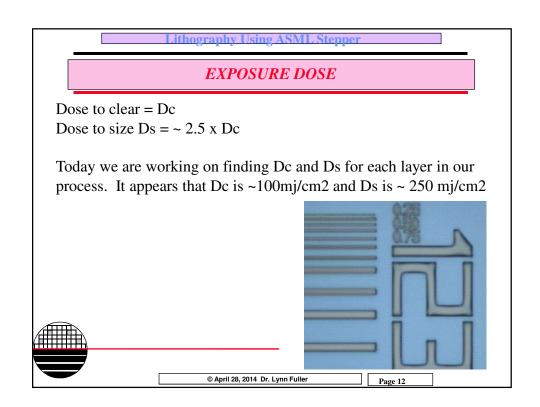

Exposure Dose

Wafer Alignment

Overlay Measurement

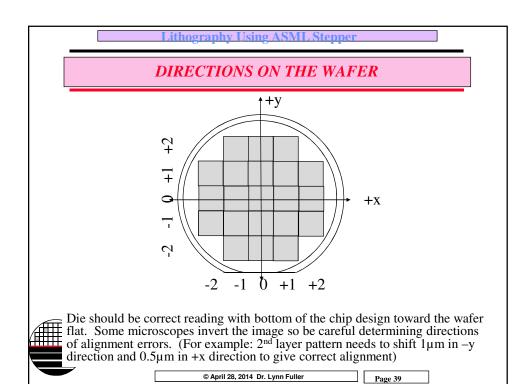

Reticle and Wafer Orientation

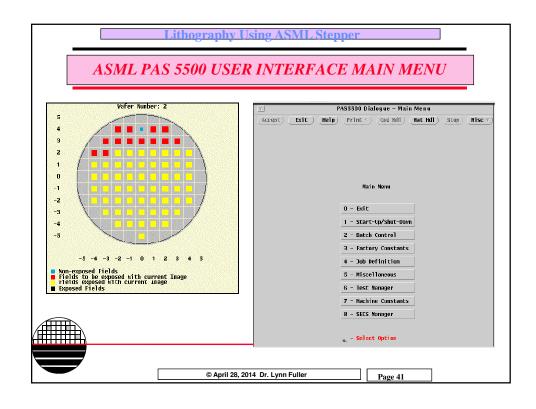

User Interface

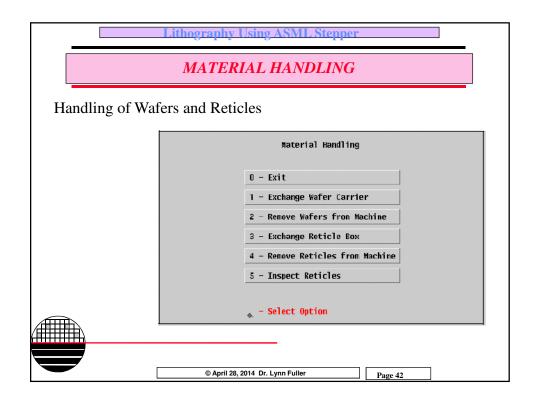

Material Handling

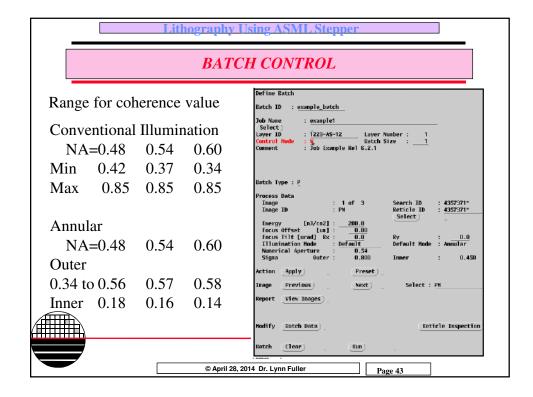

Batch Control

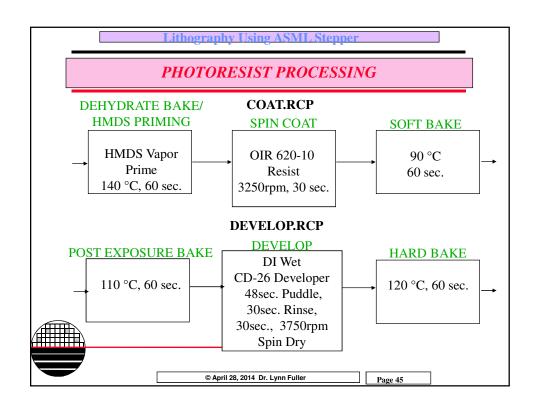

Coat and Develop Track

Stepper Jobs

References

© April 28, 2014 Dr. Lynn Fuller

Page 3

#### Lithography Using ASML Stepper

#### **INTRODUCTION**

Overlay (alignment) is as important as resolution in lithography. Modern CMOS integrated circuits have ~ 30 layers to be aligned. The RIT SUB-CMOS processes use up to 15 layers. Alignment marks are placed on the wafer at the beginning of the process during the first level lithography or in a special zero level lithography. The wafers then undergo many processing steps such as CMP, oxide growth, metal deposition and LOCOS like processes. These processes change the appearance of the alignment marks. Marks that start out as trenches can change to mesas, marks with topology can become flat after CMP, marks can change color and can become buried or even invisible. Thus a strategy for alignment must be devised as part of the process design and chip layout. The strategy may include zero level wafer alignment marks, zero and first level combined wafer alignment marks, clear out exposures over wafer alignment marks for some levels, and/or use of street alignment marks.

© April 28, 2014 Dr. Lynn Fuller

# INTRODUCTION (cont.)

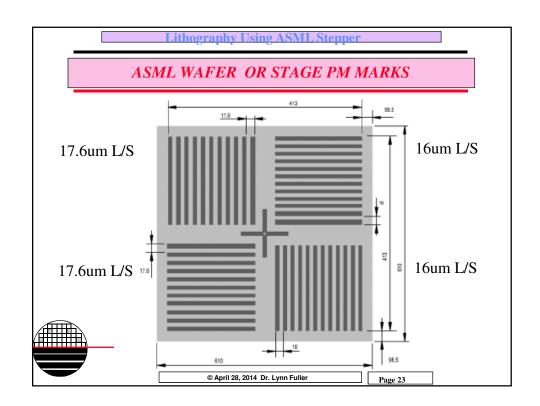

The ASML PAS 5500 uses wafer alignment marks that are diffraction gratings. There are marks for both the x and y directions. These marks are illuminated with a HeNe laser at a single wavelength near 632.8nm. The reflected wave exhibits a diffraction pattern of bright and dark lines that are focused on a sensor. The stage is moved slightly to learn the best position to match the sensor and that stage position is used to calculate the stage position to place the die under the center of the optical column. The wafer is moved to the lens center (or shifted by a fixed amount from center) and the die is exposed. The stage position for the remaining die are calculated and those die are also exposed. The wafer marks are lines and spaces etched into the starting wafer. To give maximum contrast in the diffracted pattern the etch depth  $\lambda/4n$  results in a optical path difference of  $\pi$ ,  $\lambda$  is the wavelength of the laser light and n is the index of refraction of the material above the marks (usually photoresist or oxide). The etch depth calculation gives a value of approximately 632.8/4/1.45 = 110 nm (1100 Å)

© April 28, 2014 Dr. Lynn Fuller

Page 5

#### Lithography Using ASML Stepper

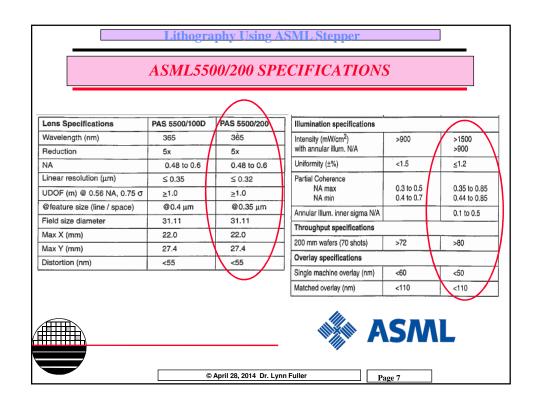

# RIT's - ASML PAS 5500/200

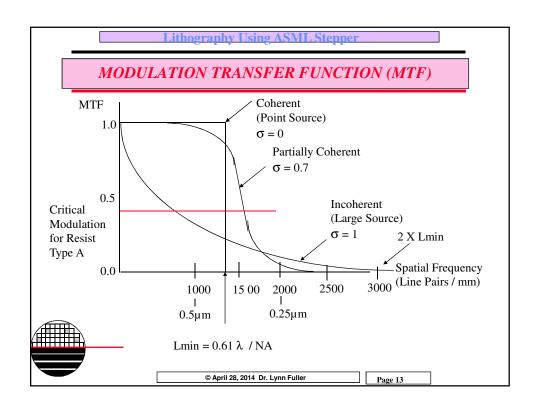

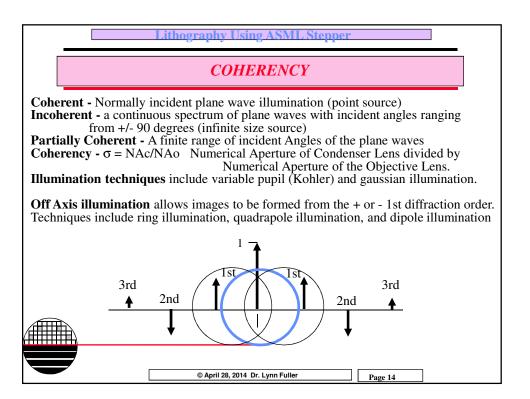

NA = 0.48 to 0.60 variable  $\sigma$ = 0.35 to 0.85 variable

With Variable Kohler, or Variable Annular illumination Resolution =  $K1 \lambda / NA$

$= \sim 0.35 \mu m$

for NA=0.6,  $\sigma$  =0.85

Depth of Focus =  $k_2 \lambda/(NA)^2$ = > 1.0  $\mu$ m for NA = 0.6

i-Line Stepper  $\lambda = 365 \text{ nm}$ 22 x 27 mm Field Size

© April 28, 2014 Dr. Lynn Fuller

# **SUMMARY**

This table lists the tradeoffs for numerical aperture, NA, coherency,  $\sigma$ , and type of illumination as it relates to resolution, Lmin, Depth of Focus, DOF, modulation of aerial image, M, and time to expose, throughput.

|                     | Lmin     | DOF      | Modulation | Throughput |

|---------------------|----------|----------|------------|------------|

| Increasing NA       | 1        | <b>↓</b> | 1          | 1          |

| Increasing <b>o</b> | 1        |          | <b>↓</b>   | 1          |

| Off Axis vs. Kohler | <b>↓</b> |          | <b>↓</b>   | <b>↓</b>   |

Increasing NA,  $\sigma$  and using off axis illumination can give higher resolution but will be offset by poorer DOF, Modulation and throughput.

© April 28, 2014 Dr. Lynn Fuller

Page 15

<u>Lithography Using ASML Stepper</u>

# STAGE ACCURACY

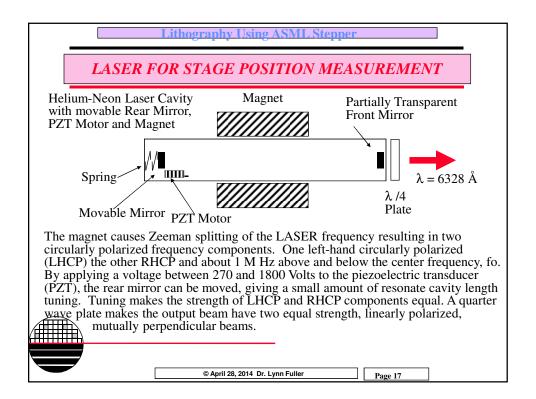

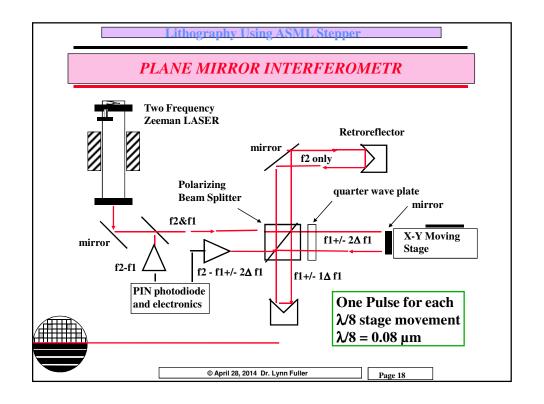

The stage position is very accurate. Its position is measured using a laser interferometer that has a fundamental accuracy of  $\lambda/8$  ~0.08µm. The interferometer measures the position of the mirrors on the x and y stages while the wafer is some distance from the mirrors on the stage. If the temperature inside the environmental chamber is kept constant then the errors caused by the thermal coefficient of expansion for the stage can be minimized. The stage accuracy is monitored periodically to ensure that the interferometer is working correctly. However, in most modes of operation, including alignment, the stepper stage measured position is assumed to be perfect.

© April 28, 2014 Dr. Lynn Fuller

#### <u>Lithography Using ASML Stepper</u>

#### **ALIGNMENT**

Alignment involves placing the wafer /stage in a position such that the wafer/stage marks can be illuminated by the HeNe laser. The reflected diffraction pattern goes back through the lens and the wafer image is reconstructed from the +/-1<sup>st</sup> order components of the diffraction pattern (the zero order is returned to the laser, higher orders are blocked). The electric and magnetic fields are transferred through the lens as in a linear system resulting in a sinusoidal field image. The intensity is the square of the field doubling the frequency of the diffraction grating on the wafer when viewed at the mask level. This image is superimposed on the fiducial marks on the reticle and a light detector measures the brightness as the stage is moved to find best alignment of the wafer to the mask.

© April 28, 2014 Dr. Lynn Fuller

Page 19

Page 20

# OPTICAL PATH FOR WAFER ALIGNMENT The red laser is split into two beams one directed toward the left side of the wafer and the other directed toward the right side of the wafer, for alignment marks on the left or right side respectively. Only one alignment mark is illuminated at a time.

© April 28, 2014 Dr. Lynn Fuller

# TYPES OF ALIGNMENT

**Fiducial** – Reticle alignment when there are no alignment marks on the wafer (zero or 1<sup>st</sup> level) F1 aligned to M1 and F1 to M2

**Global** – After both reticle and wafer exchange F1 aligned to M1, W1 to M2, and W2 to M1

Wafer – After wafer exchange W1 aligned to M1 and W2 to M1

**Reticle** – After reticle exchange W1aligned to M1 and W1 to M2

Reticle

© April 28, 2014 Dr. Lynn Fuller

#### <u>Lithography Using ASML Stepper</u>

# WAFER ALIGNMENT CONTINUED

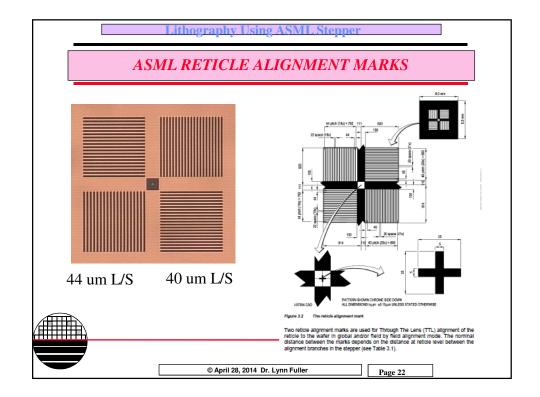

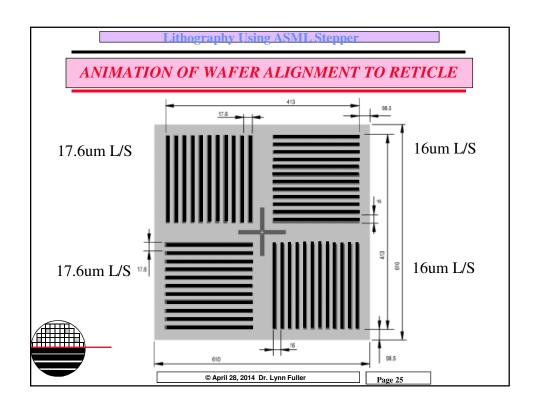

The 16um L/S wafer marks are transferred to the mask at 5X for the lens magnification divided by two for the frequency doubling. This is 40um L/S equal to the period on the reticle alignment marks. (the 17.6um L/S becomes 44um L/S at the reticle) The light from the wafer goes through the lens and through the reticle alignment marks to the detector. The stage moves to determine the best alignment. Thus the wafer is aligned to the reticle.

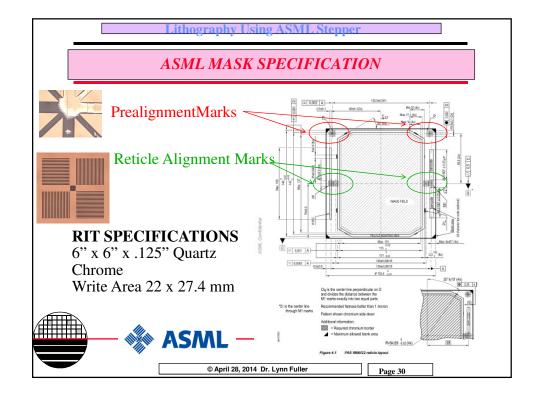

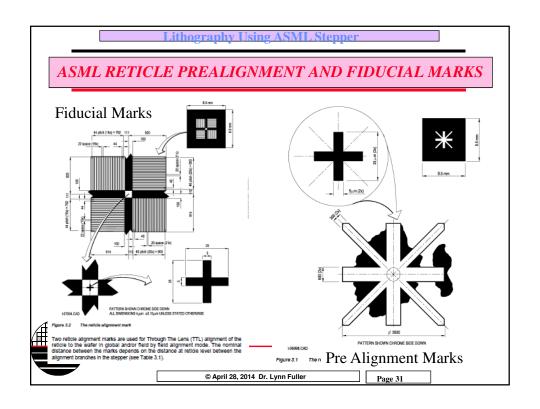

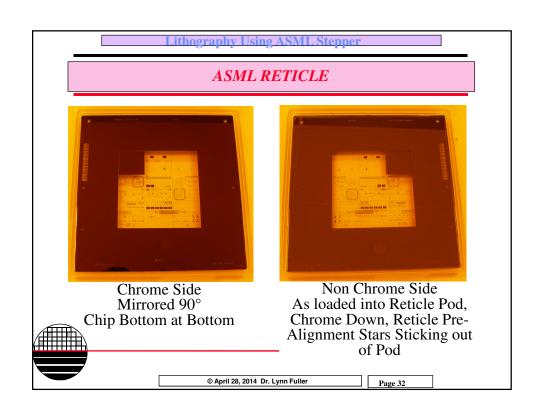

#### RETICLE ALIGNMENT

In order to align a reticle to the stepper, the reticle must have fiducial marks at given locations near the edge of the mask. The ASML fiducial marks are shown on the following pages. They are automatically included in any stepper job written in the RIT maskshop. If your mask is made outside of RIT you will need to request fiducial marks and specify type and possibly the exact location on the mask.

You can use reticles with no fiducial marks but only in a non production mode such as exposure matrix. To do this press alignment and change alignment mode to N (none).

#### <u>Lithography Using ASML Stepper</u>

# RETICLE ALIGNMENT (continued)

Once the mask is placed on the platen. The reticle prealignment marks are used to position the reticle in the approximate correct location. The stage is moved to position special alignment marks attached to the stage in the correct position to do the reticle fine alignment. Just like wafer alignment the marks are illuminated with a HeNe laser and the reticle is moved to give the best alignment position and then held in that position until removed from the stepper.

© April 28, 2014 Dr. Lynn Fuller

# ASML 4 LEVELS PER PLATE RETICLE

Stepper Job Name = PMOS

Masks with 4 levels per plate

Saves money, time, inventory

Max Chip size 10mm by 10mm

© April 28, 2014 Dr. Lynn Fuller

Page 33

Lithography Using ASML Stepper

# COMBINED ZERO AND FIRST LEVEL WAFER MARKS

The wafer marks can be etched to the calculated depth or created by differential oxide growth.

For example a wafer with 500nm of oxide on it can be patterned and etched with the wafer marks followed by another 500nm oxide growth resulting in a 120nm step in the silicon. One could also use LOCOS or shallow trench processes to create steps in the silicon.

Drytek Quad, Recipe ZEROETCH Chamber3, Step 1, 100 mTorr, 200w CF4=25, CHF3=50, O2=10sccm, Max Etch Time = 2 min for 1300Å

© April 28, 2014 Dr. Lynn Fuller