# ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

# **Introduction to Digital Electronics**

# Dr. Lynn Fuller

Webpage: <a href="http://people.rit.edu/lffeee">http://people.rit.edu/lffeee</a>

Microelectronic Engineering

Rochester Institute of Technology

82 Lomb Memorial Drive

Rochester, NY 14623-5604

Tel (585) 475-2035

Email: Lynn.Fuller@rit.edu

Department webpage: <a href="http://www.microe.rit.edu">http://www.microe.rit.edu</a>

10-12-2014 IntroDigitalElectronics.ppt

#### ADOBE PRESENTER

This PowerPoint module has been published using Adobe Presenter. Please click on the Notes tab in the left panel to read the instructors comments for each slide. Manually advance the slide by clicking on the play arrow or pressing the page down key.

#### **OUTLINE**

Brief History of IC Industry **Basic Logic Functions** Logic (Really Continuous Signals) VTC and Noise Margin **Transient Characteristics Power Dissipation** Digital Circuit Design PMOS, NMOS, CMOS CAD, VLSI Standard Cell Design System on a Chip (SOC) Challenges Ahead References Homework

Rochester Institute of Technology

# **INTRODUCTION**

# Industry rankings not including foundries

| Rank<br>2012 | Rank<br>2011 | Rank<br>2010 |    | Company                 | Country of origin       | Revenue<br>(million<br>\$ USD) | 2012/2011 changes | Market share |

|--------------|--------------|--------------|----|-------------------------|-------------------------|--------------------------------|-------------------|--------------|

| 1            | 1            | 1            | 1  | Intel Corporation       | United States           | \$47,543                       | -2.4%             | 15.7%        |

| 2            | 2            | 2            | 2  | Samsung Electronics     | South Korea             | \$30,474                       | +6.7%             | 10.1%        |

| 3            | 6            | 9            | 6  | Qualcomm                | United States           | \$12,976                       | +27.2%            | 4.3%         |

| 4            | 3            | 4            | 4  | Texas Instruments       | United States           | \$12,008                       | -14.0%            | 4.0%         |

| 5            | 4            | 3            | 3  | Toshiba Semiconductors  | <ul><li>Japan</li></ul> | \$10,996                       | -13.6%            | 3.6%         |

| 6            | 5            | 5            | 9  | Renesas Electronics (1) | <ul><li>Japan</li></ul> | \$9,430                        | -11.4%            | 3.1%         |

| 7            | 8            | 6            | 7  | Hynix                   | South Korea             | \$8,462                        | -8.9%             | 2.8%         |

| 8            | 7            | 7            | 5  | STMicroelectronics      | France / I I Italy      | \$8,453                        | -13.2%            | 2.8%         |

| 9            | 10           | 10           | 14 | Broadcom                | United States           | \$7,840                        | +9.5%             | 2.6%         |

| 10           | 9            | 8            | 13 | Micron Technology (2)   | United States           | \$6,955                        | -5.6%             | 2.3%         |

Total \$304B in 2010

## TSMC AND GLOBAL FOUNDRIES

TSMC, Tiwan

http://www.tsmc.com/english/default.htm

Global Foundries, Malta, New York

http://www.globalfoundries.com/

http://www.globalfoundries.com/manufacturing/fab-8-overview

Go to these web locations and explore, watch some videos, etc.

Rochester Institute of Technology

# JACK KILBY AND ROBERT NOYCE

# The First (2D) Integrated Circuit Jack Kilby, Texas Instruments, 1958

- Transistor, Resistors and Capacitors on the same piece of semiconductor

- · Interconnects between components not integrated

- → Low connectivity between components

# Nobel Prize in Physics 2001

# The First Monolithic (2D) Integrated Circuit Robert Noyce, Fairchild Semiconductor, 1961

- Transistor, Resistors and Capacitors on the same piece of semiconductor

- Interconnects between components integrated

- → High connectivity between components

# JACK KILBY AT RIT 1986

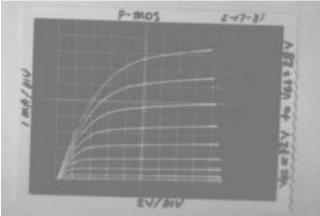

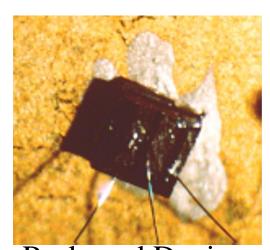

# FIRST TRANSISTORS MADE AT RIT 1981

Vt = 12 volts

2" n-type silicon wafer

2-17-81 Rob Pearson Jim Radak

**PMOS** Transistors

Packaged Device Aluminum wire bonds

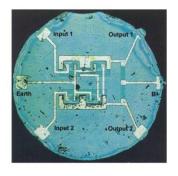

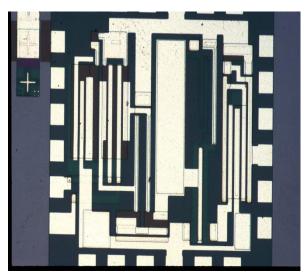

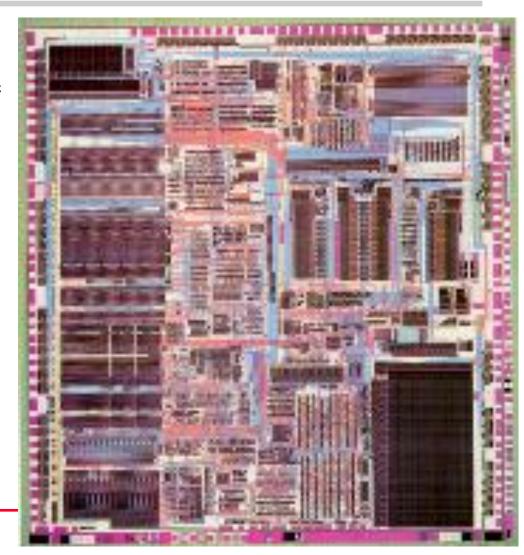

# FIRST INTEGRATED CIRCUITS MADE AT RIT

Jonathan Littlehale All PMOS Op Amp 1985

Jim Pollard Metal Gate CMOS 1987

Dr. Lane's

Thin Films Class

NMOS Inverter

1990's

Rochester Institute of Technology

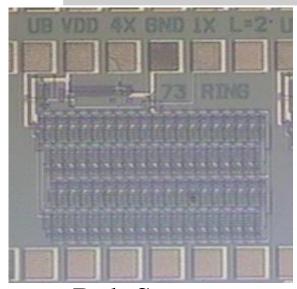

# FIRST INTEGRATED CIRCUITS MADE AT RIT

Rob Saxer 2μm 73 Stage CMOS Ring Oscillator 2000

George Lungu 10,000 Pixel Imager 1999

1.0

VD (Volts)

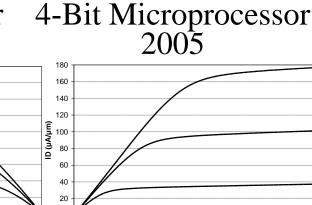

Mike Aquilino 250 nm CMOS MOSFETS, 2006

© October 12, 2014 Dr. Lynn Fuller

-1.0

VD (volts)

-2.0

Page 10

0.0

# **PROCESS TECHNOLOGY**

# Process Technology

Rochester Institute of Technology

## **PROCESS SELECTION**

It is not necessary to know all process details to do CMOS integrated circuit design. However the process determines important circuit parameters such as supply voltage and maximum frequency of operation. It also determines if devices other than PMOS and NMOS transistors can be realized such as poly-to-poly capacitors and EEPROM transistors. The number of metal interconnect layers is also part of the process definition. Starting wafer type determines if isolated n-wells or p-wells are available.

# RIT PROCESSES

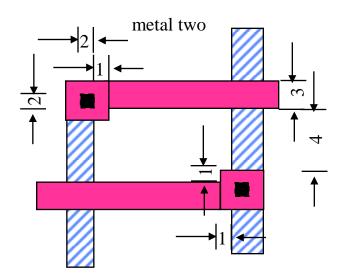

At RIT we use the Sub-CMOS and ADV-CMOS processes for most designs. In these processes the minimum poly length is 1 $\mu$ m and 0.5 $\mu$ m respectively. We use scalable MOSIS design rules with lambda equal to 0.5 $\mu$ m and 0.25 $\mu$ m. These processes use one layer of poly and two layers of metal.

The examples on the following pages are designs that could be made with either of the above processes. As a result the designs are generous, meaning that larger than minimum dimensions are used. For example  $\lambda=0.5\mu m$  and minimum poly is  $2\lambda$  which would result in transistor gate length of  $1\mu m$  but are designed at  $2\mu m$  for higher yield.

The design approach for digital circuits is to design primitive cells and then use the primitive cells to design basic cells which are then used in the project designs. A layout approach is also used that allows for easy assembly of these cells into more complex cells.

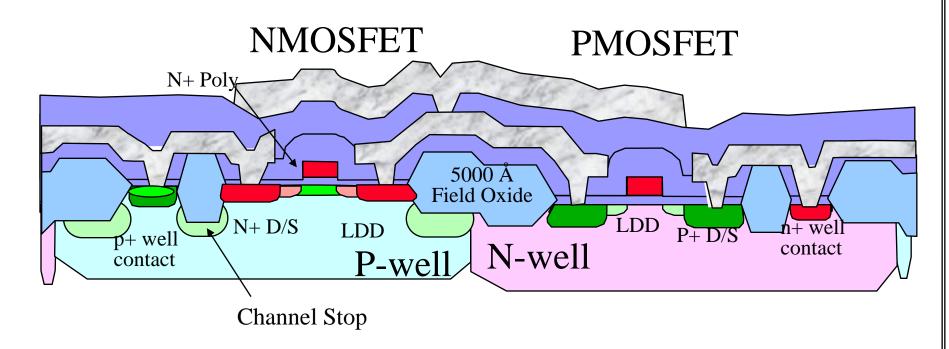

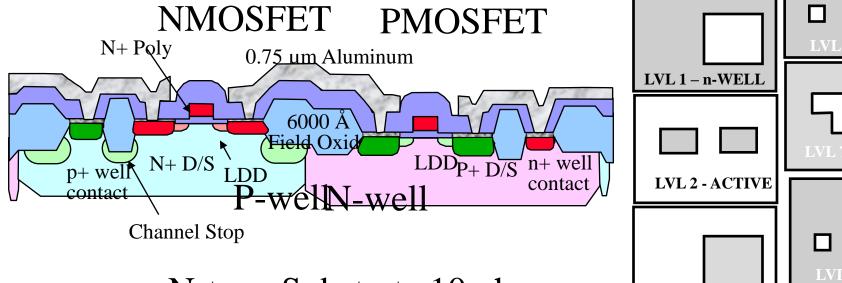

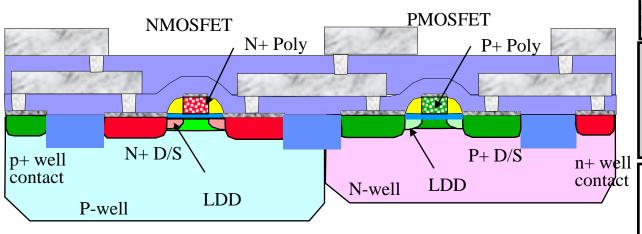

# RIT SUBµ CMOS

# RIT Subµ CMOS

150 mm wafers

Nsub = 1E15 cm-3

Nn-well = 3E16 cm-3

$Xj = 2.5 \mu m$

Np-well = 1E16 cm-3

$X\hat{j} = 3.0 \, \mu m$

LOCOS

Field Ox = 6000 Å

Xox = 150 Å

Lmin=  $1.0 \mu m$

LDD/Side Wall Spacers

2 Layers Aluminum

Long Channel Behavior

3.3 Volt Technology VT's = +/- 0.75 Volt Robust Process (always works) Fully Characterized (SPICE)

# RIT SUBµ CMOS

# Substrate 10 ohm-cm

Rochester Institute of Technology

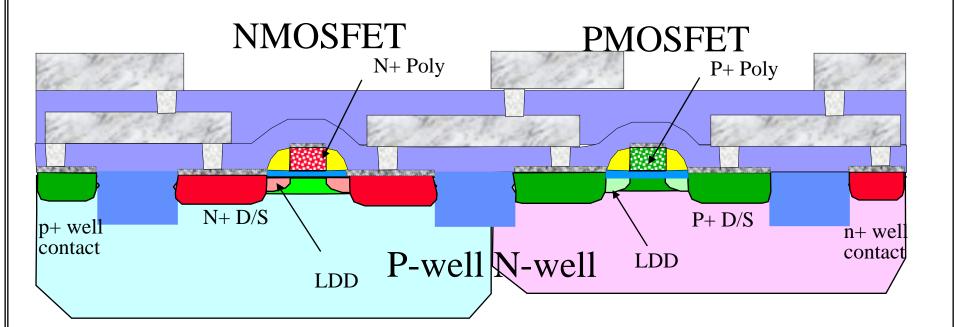

# RIT ADVANCED CMOS VER 150

## **RIT Advanced CMOS**

150 mm Wafers

Nsub = 1E15 cm-3 or 10 ohm-cm, p

Nn-well = 1E17 cm-3

$Xj = 2.5 \mu m$

Np-well = 1E17 cm-3

$X\hat{j} = 2.5 \mu m$

Shallow Trench Isolation

Field Ox (Trench Fill) = 4000 Å

Dual Doped Gate n+ and p+

Xox = 100 Å

Lmin =  $0.5 \mu m$ , Lpoly =  $0.35 \mu m$ , Leff =  $0.11 \mu m$

LDD/Nitride Side Wall Spacers

TiSi2 Salicide

Tungsten Plugs, CMP, 2 Layers Aluminum

Long Channel Behavior

Vdd = 3.3 volts

Vto=+-0.75 volts

Rochester Institute of Technology

# RIT ADVANCED CMOS

Rochester Institute of Technology

# **DIGITAL ELECTRONICS**

# Digital Electronics

Rochester Institute of Technology

## DIGITAL INTEGRATED CIRCUITS

BOOLEAN ALGEBRA IS BASED ON TWO DISCRETE LEVELS CALLED LOW OR HIGH (0 OR 1). (from George Boole, 1815-1864)

BOOLEAN ALGEBRA USES FUNCTIONS SUCH AS "INVERT", "AND", "OR" TO EVALUATE INPUTS AND GENERATE "OUTPUTS".

THE TERM "BINARY LOGIC" IS USED TO DESCRIBE DEVICES THAT FOLLOW THE RULES OF BOOLEAN ALGEBRA.

EACH SUB CIRCUIT OR "GATE" SHOULD HAVE ITS INPUTS AND OUTPUTS AT 0 OR 1 (Except Briefly During Switching)

Rochester Institute of Technology

# **BASIC LOGIC FUNCTIONS**

INV, NAND NOR

Truth Tables

Sum of Products, Product of Sums

XOR, XNOR, MUX

Sequential Logic

RS, D, JK, T Flip Flops

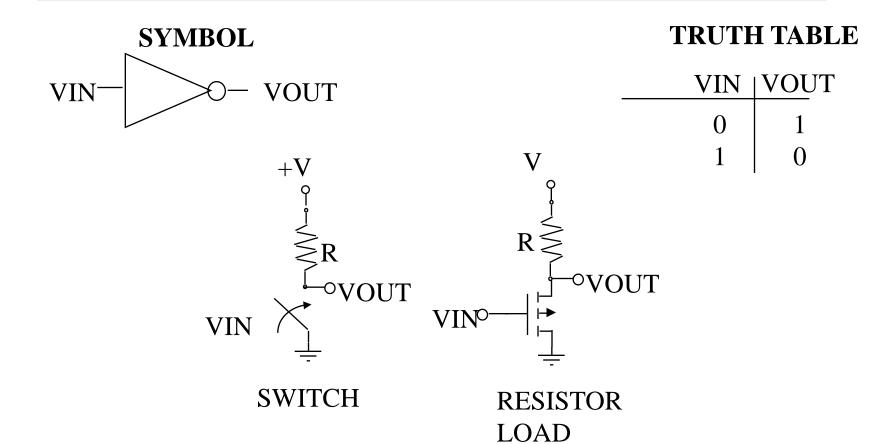

# **INVERTER**

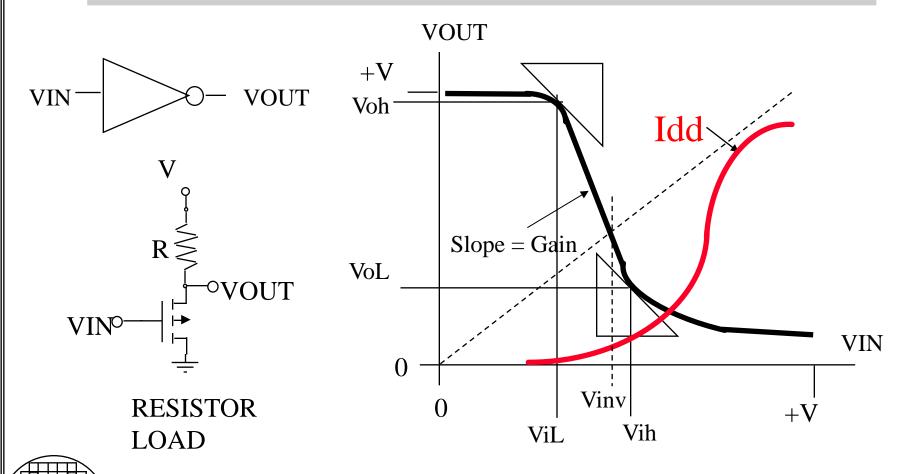

# **VOLTAGE TRANSFER CURVE**

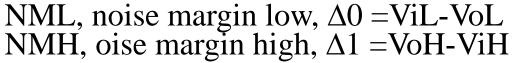

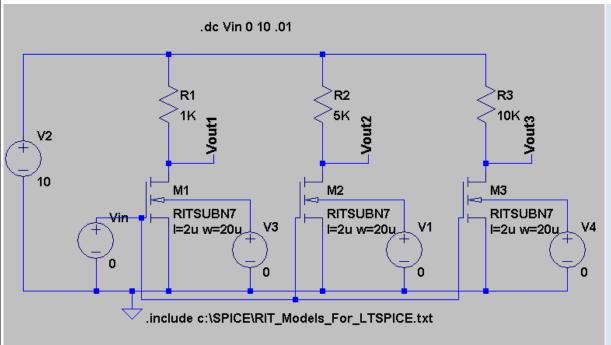

# LTSPICE - INVERTER VTC - FOR DIFFERENT RL

Rochester Institute of Technology

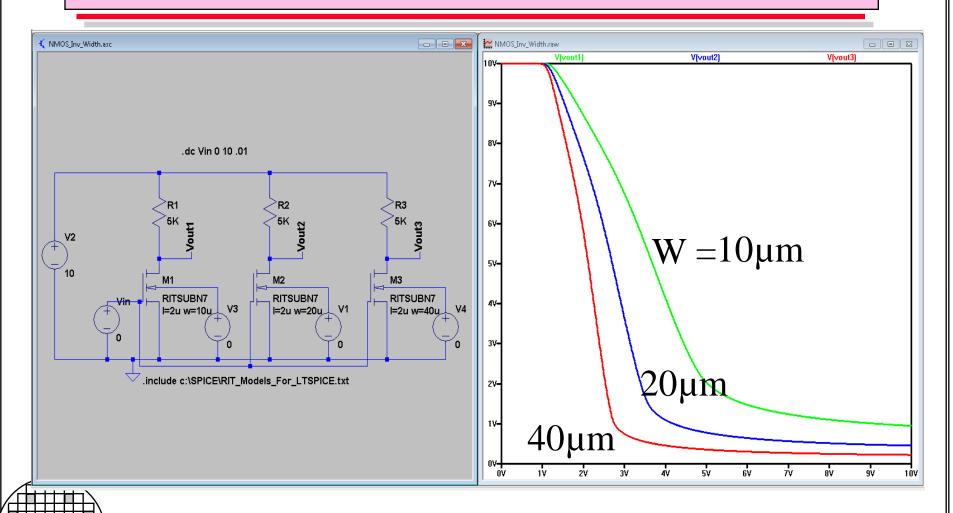

# LTSPICE - INVERTER FOR DIFFERENT NMOS W

Rochester Institute of Technology

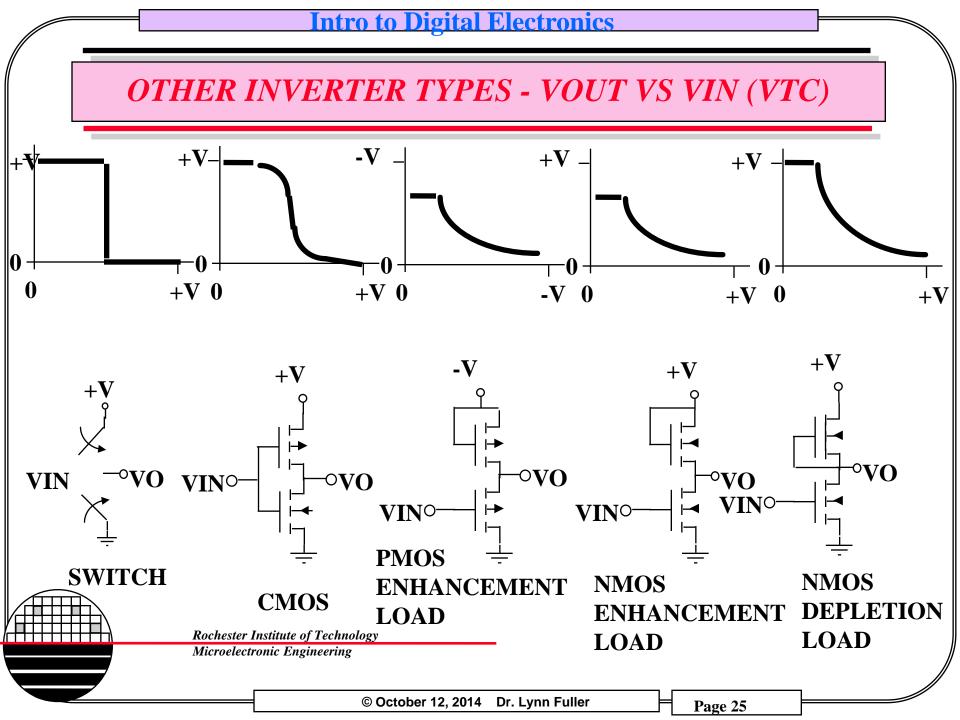

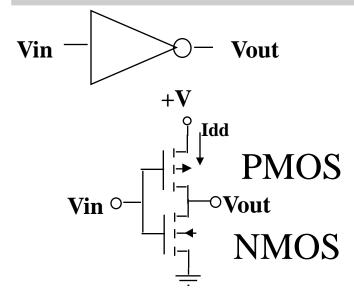

# **CMOS INVERTER**

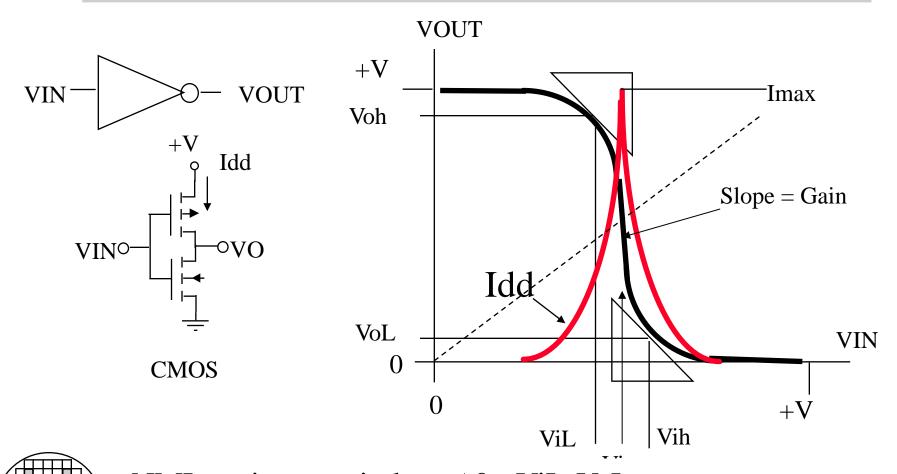

NML, noise margin low,  $\Delta 0 = ViL-VoL$  NMH, noise margin high,  $\Delta 1 = VoH-ViH$

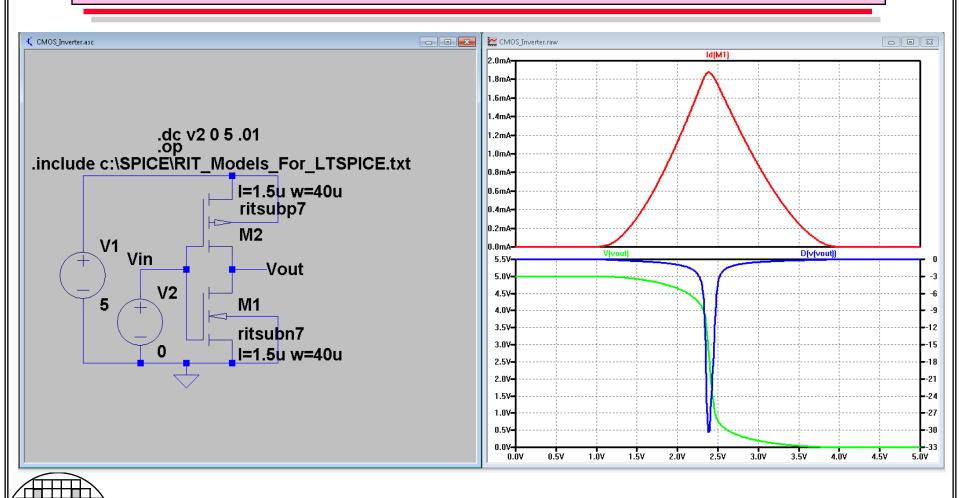

# LTSPICE - CMOS INVERTER

# **INVERTER PROPERTIES**

DC Properties

Noise Margins

Current, I

Size

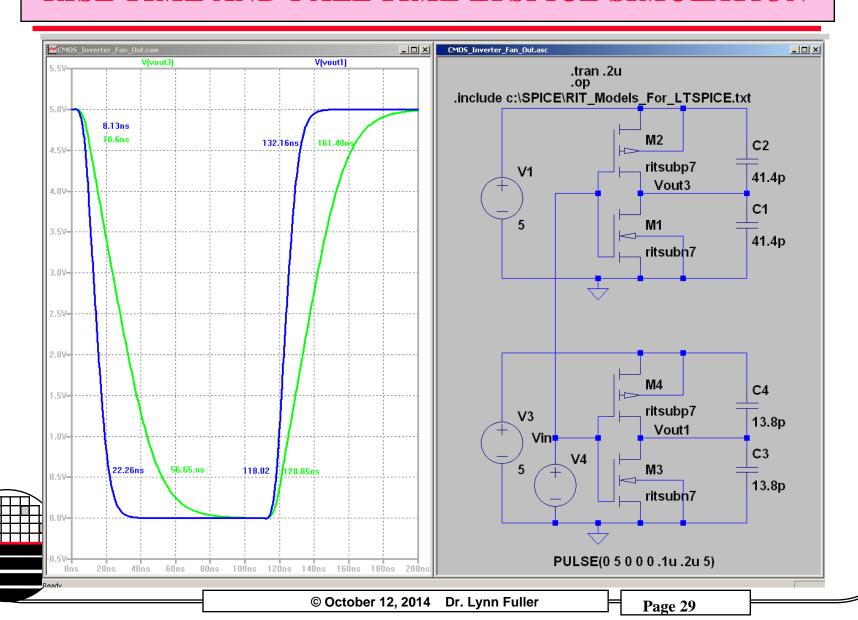

Transient Properties

Rise/Fall Time

Fan Out

Rochester Institute of Technology

## RISE TIME AND FALL TIME LTSPICE SIMULATION

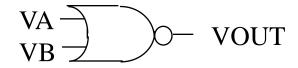

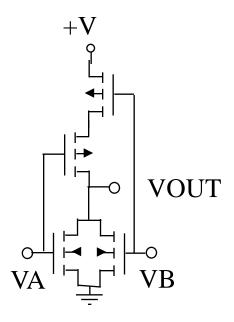

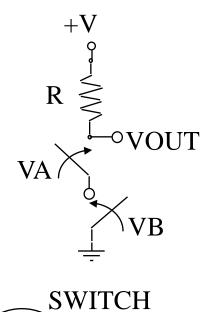

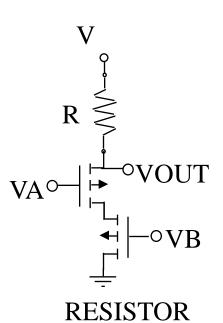

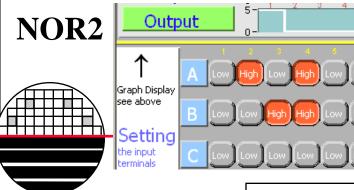

# **NOR GATE**

# **SYMBOL**

| TRUTH TABLE | VA | VB | <u> </u> |

|-------------|----|----|----------|

|             |    |    |          |

| , | • = | _ · · · · |

|---|-----|-----------|

| 0 | 0   | 1         |

| 0 | 1   | 0         |

| 1 | 0   | 0         |

| 1 | 1   | 0         |

R VOUT

RESISTOR LOAD

Rochester Institute of Technology

Microelectronic Engineering

**CMOS**

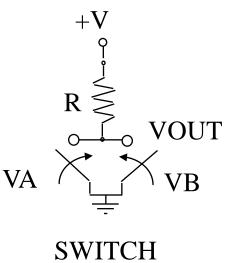

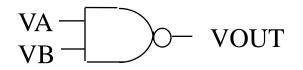

# NAND GATE

#### **SYMBOL**

LOAD

**VOUT** TRUTH TABLE\_VA VB +V**VOUT** VAO o VB

**CMOS**

# **OTHER LOGIC GATES**

|          | AN    | ID                   |       | OR    |                | 3       | INF | PUT | AND   |           | 3 IN                 | IPUT | OR    |

|----------|-------|----------------------|-------|-------|----------------|---------|-----|-----|-------|-----------|----------------------|------|-------|

| VA<br>VB |       | - VOUT               | VA VB |       | VOUT           | VA<br>V |     |     | ⊢VOUT | V         | YA A<br>YB A<br>VC Z |      | -VOUT |

| VA       | VB    | VOUT                 | VA    | VB    | VOUT           | VA      | VB  | VC  | VOUT  | <u>VA</u> | VB                   | VC   | VOUT  |

| 0        | 0     | 0                    | 0     | 0     | 0              | 0       | 0   | 0   | 0     | 0         | 0                    | 0    | 0     |

| 0        | 1     | 0                    | 0     | 1     | 1              | 0       | 0   | 1   | 0     | 0         | 0                    | 1    | 1     |

| 1        | 0     | 0                    | 1     | 0     | 1              | 0       | 1   | 0   | 0     | 0         | 1                    | 0    | 1     |

| 1        | 1     | 1                    | 1     | 1     | 1              | 0       | 1   | 1   | 0     | 0         | 1                    | 1    | 1     |

|          |       |                      |       |       |                | 1       | 0   | 0   | 0     | 1         | 0                    | 0    | 1     |

|          |       |                      | _     |       |                | 1       | 0   | 1   | 0     | 1         | 0                    | 1    | 1     |

|          | _)o-[ | <del>&gt;&gt;-</del> |       | _)o-[ | <b>&gt;</b> >- | 1       | 1   | 0   | 0     | 1         | 1                    | 0    | 1     |

|          |       |                      |       |       |                | 1       | 1   | 1   | 1     | 1         | 1                    | 1    | 1     |

# **ADDITION IN BINARY**

| IN I  | BASE 10 | 0  | 0000 |

|-------|---------|----|------|

|       |         | 1  | 0001 |

|       | 7       | 2  | 0010 |

|       | +2      | 3  | 0011 |

|       |         | 4  | 0100 |

|       | 9       | 5  | 0101 |

|       |         | 6  | 0110 |

| IN BI | NARY    | 7  | 0111 |

|       |         | 8  | 1000 |

| 11    | CARRY   | 9  | 1001 |

| 0111  |         | 10 | 1010 |

| 0010  |         | 11 | 1011 |

|       |         | 12 | 1100 |

| 1001  | SUM     | 13 | 1101 |

|       |         | 14 | 1110 |

|       |         | 15 | 1111 |

TRUTH TABLE FOR ADDITION RULES

| <u>A</u> | В | CIN | <u>SUM</u> | COUT |

|----------|---|-----|------------|------|

| 0        | 0 | 0   | 0          | 0    |

| 0        | 0 | 1   | 1          | 0    |

| 0        | 1 | 0   | 1          | 0    |

| 0        | 1 | 1   | 0          | 1    |

| 1        | 0 | 0   | 1          | 0    |

| 1        | 0 | 1   | 0          | 1    |

| 1        | 1 | 0   | 0          | 1    |

| 1        | 1 | 1   | 1          | 1    |

|          |   |     |            |      |

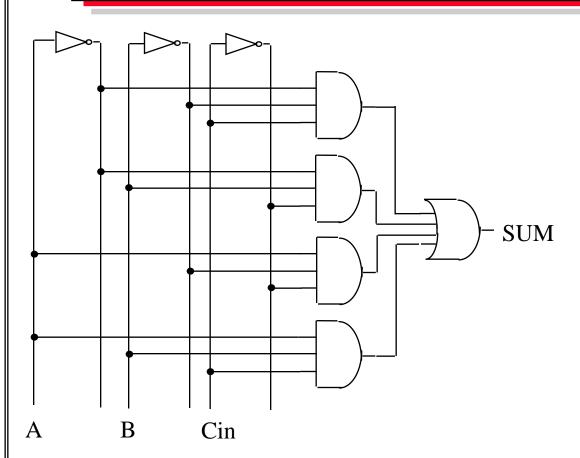

# AND-OR CIRCUIT REALIZATION OF SUM

TRUTH TABLE FOR ADDITION RULES

| <u>A</u> | В | CIN | <u>SUM</u> | COUT |

|----------|---|-----|------------|------|

| 0        | 0 | 0   | 0          | 0    |

| 0        | 0 | 1   | 1          | 0    |

| 0        | 1 | 0   | 1          | 0    |

| 0        | 1 | 1   | 0          | 1    |

| 1        | 0 | 0   | 1          | 0    |

| 1        | 0 | 1   | 0          | 1    |

| 1        | 1 | 0   | 0          | 1    |

| 1        | 1 | 1   | 1          | 1    |

|          |   |     |            |      |

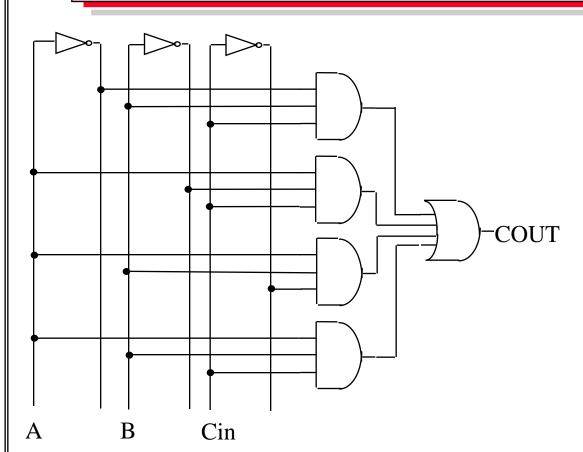

# CIRCUIT REALIZATION OF CARRY OUT (COUT)

TRUTH TABLE FOR ADDITION RULES

| <u>A</u> | В | CIN | <u>SUM</u> | COUT |

|----------|---|-----|------------|------|

| 0        | 0 | 0   | 0          | 0    |

| 0        | 0 | 1   | 1          | 0    |

| 0        | 1 | 0   | 1          | 0    |

| 0        | 1 | 1   | 0          | 1    |

| 1        | 0 | 0   | 1          | 0    |

| 1        | 0 | 1   | 0          | 1    |

| 1        | 1 | 0   | 0          | 1    |

| 1        | 1 | 1   | 1          | 1    |

|          |   |     |            |      |

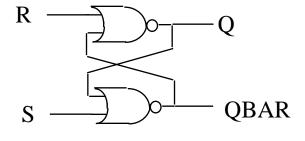

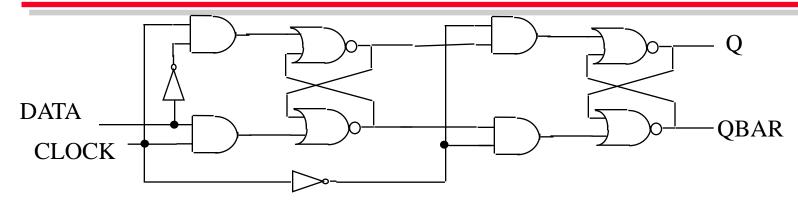

# FILP-FLOPS

RS FLIP FLOP

| R | S | _ Q_          |

|---|---|---------------|

| 0 | 0 | Qn-1          |

| 0 | 1 | 1             |

| 1 | 0 | 0             |

| 1 | 1 | INDETERMINATE |

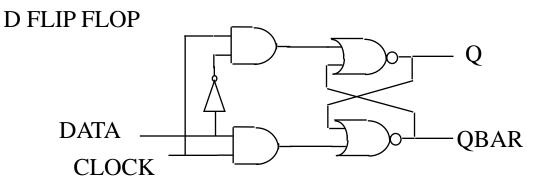

Q=DATA IF CLOCK IS HIGH IF CLOCK IS LOW Q=PREVIOUS DATA VALUE

Rochester Institute of Technology

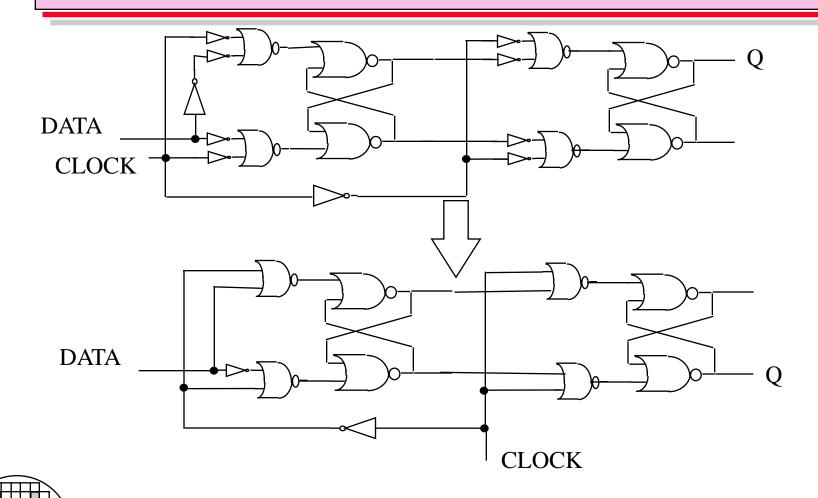

#### MASTER-SLAVE D FLIP FLOP

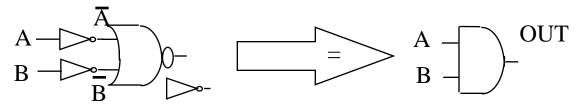

#### NEGATED INPUT NOR IS EQUAL TO AND

| A | В | Ā | B | OUT | OUT |

|---|---|---|---|-----|-----|

| 0 | 0 | 1 | 1 | 1   | 0   |

| 0 | 1 | 1 | 0 | 1   | 0   |

| 1 | 0 | 0 | 1 | 1   | 0   |

| 1 | 1 | 0 | 0 | 0   | 1   |

Rochester Institute of Technology

#### ALL NOR MASTER SLAVE D FLIP FLOP

Rochester Institute of Technology

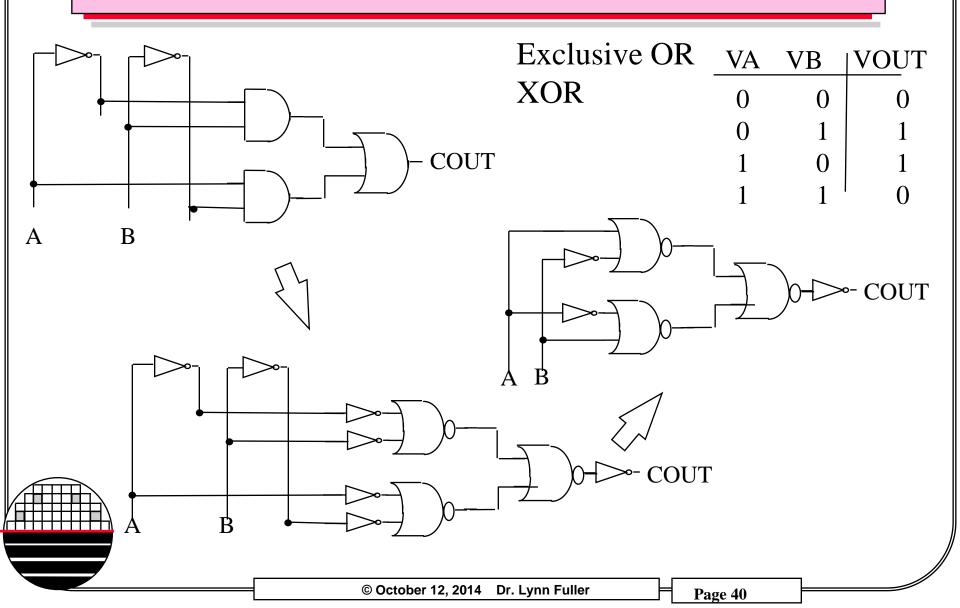

#### **EQUAVILANT REALIZATIONS**

AND-OR realizations are easily derived from truth table description of a circuits performance. Replacing the AND and OR gates with all NOR gates is equivalent. Replacing the AND and OR gates with all NAND gates is equivalent.

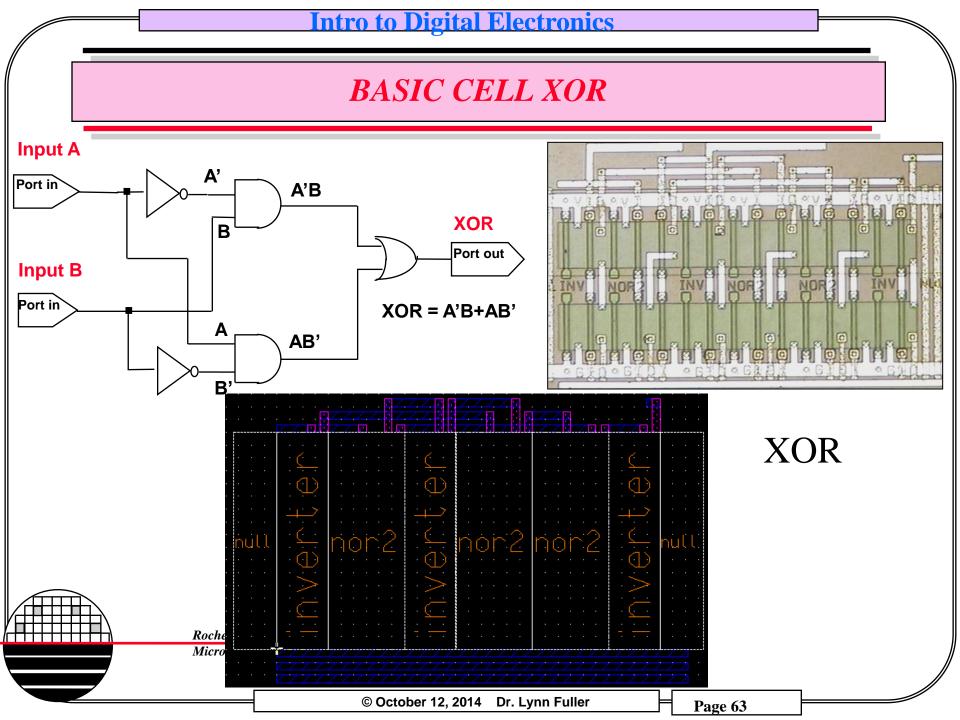

#### **CIRCUIT REALIZATION FOR XOR**

#### **VLSI**

# VLSI Very Large Scale Integration

Rochester Institute of Technology

#### **INTRODUCTION**

VLSI is an acronym for Very Large Scale Integration. This includes Integrated circuits with greater than tens of thousands of transistors including multi-million or even billions of transistors.

VLSI Design refers to methodologies and computer software tools for designing digital circuits with huge numbers of transistors. Some of theses methodologies and tools can also be applied to analog circuit design.

Software tools include schematic capture, SPICE analog simulation, switch level digital simulation, layout editors, layout versus schematic checking, design rule checking (DRC), auto place and routing and many more.

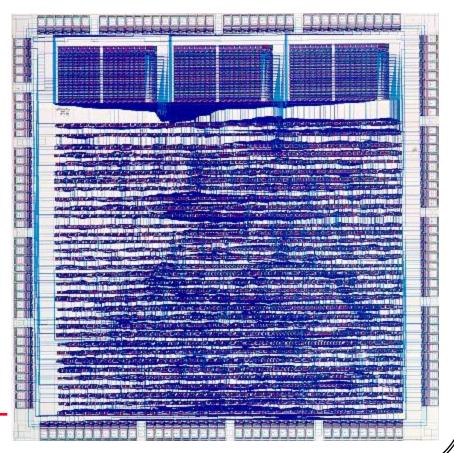

#### **VLSI DESIGN**

Computer software is used to check the layout, compare the layout to the schematic and make it possible to design circuits with millions of transistors with no errors.

Rochester Institute of Technology Microelectronic Engineering

#### **VLSI DESIGN METHODOLOGIES**

### **Full Custom Design**

Direct control of layout and device parameters

Longer design time High performance fast, low power, dense

## Standard Cell Design

Easy to implement Medium performance Limited cell library selections

# Gate Array or Programmable Logic Array Design

Fastest design turn around

Rochester Institute of Technology

Microelectronic Engineering

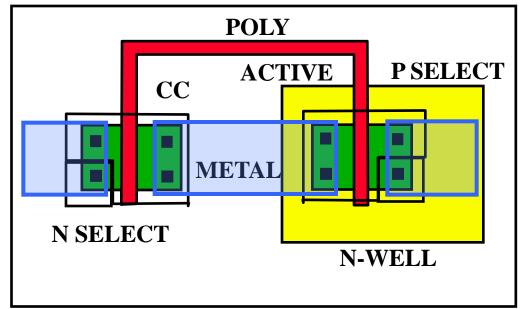

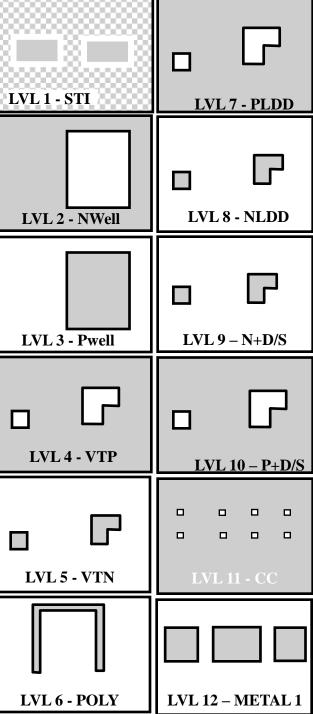

#### **LAYOUT**

# Layout Design Rules

Rochester Institute of Technology

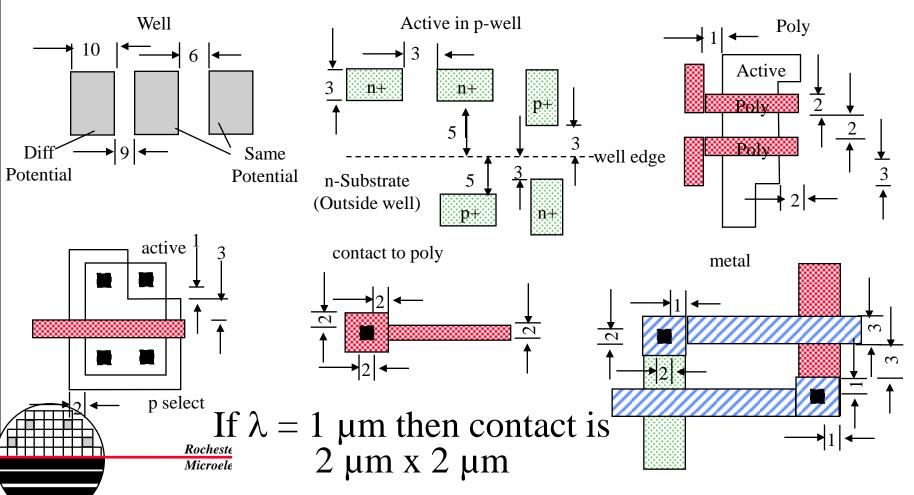

#### LAMBDA BASED DESIGN RULES

The design rules may change from foundry to foundry or for different technologies. So to make the design rules generic the sizes, separations and overlap are given in terms of numbers of lambda ( $\lambda$ ). The actual size is found by multiplying the number by the value for lambda for that specific foundry.

For example:

RIT PMOS process  $\lambda = 10~\mu m$  and minimum metal width is 3  $\lambda$  so that gives a minimum metal width of 30  $\mu m$ . The RIT SUB-CMOS process has  $\lambda = 0.5~\mu m$  and the minimum metal width is also 3  $\lambda$  so minimum metal is 1.5  $\mu m$  but if we send our CMOS designs out to industry  $\lambda$  might be 0.25  $\mu m$  so the minimum metal of 3  $\lambda$  corresponds to 0.75  $\mu m$ . In all cases the design rule is the minimum metal width = 3  $\lambda$

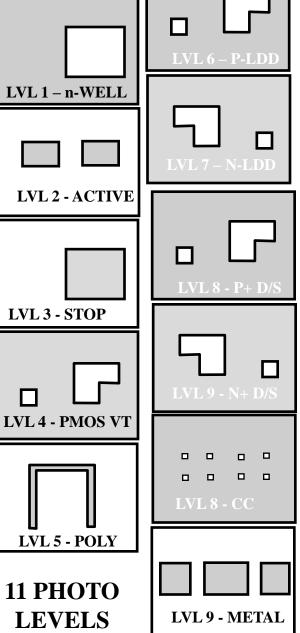

#### **DESIGN RULES**

We will use a modified version of the MOSIS TSMC 0.35 2P 4M design rules. Eventually we hope to be compatible with MOSIS but new process technology needs to be developed at RIT to do that (PECVD Tungsten, 4 layer metal). We use one layer of poly and two layers of metal. We will use the same design layer numbers with additional layers as defined on the following pages for manufacturing/maskmaking enhancements. Many of the designs will use minimum drawn poly gate lengths of 2µm where circuit architecture is the main purpose of the design. Minimum size devices (Drawn Poly =  $0.5\mu m$ , etc.) are included to develop manufacturing process technology. These transistors (0.5µm drawn) yield 0.35µm Leff and are equivalent to the TSMC 0.35 µm transistors.

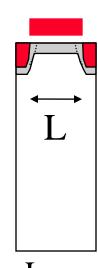

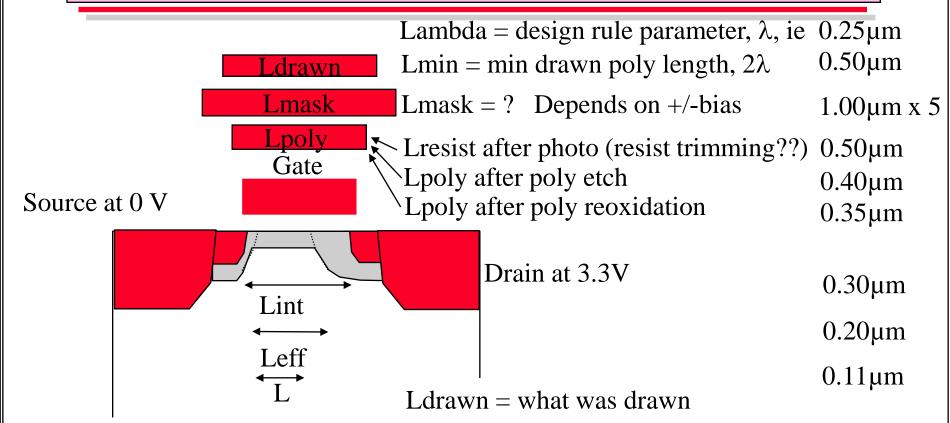

## LAMBDA, Lmin, Ldrawn, Lmask, Lpoly, Lint, Leff, L

Internal Channel Length, Lint = distance between junctions, including under diffusion Effective Channel Length, Leff = distance between space charge layers, Vd = Vs = 0 Channel Length, L, = distance between space charge layers, when Vd = What it is Extracted Channel Length Parameters = anything that makes the fit good (not real)

#### MOSIS TSMC 0.35 2POLY 4 METAL PROCESS

#### **General Information**

About MOSIS

Products

Processes

Prices

Support

User Group

Events

Job Openings

News

#### Work with MOSIS

Overview Getting Started Design and Test

#### Requests

Run Status Project Status Test Data

#### **Docs and Forms**

<u>Documents</u> <u>Forms/Agreements</u> <u>Web Forms</u>

#### Quick Reference

New Users

Experienced Users

Purchasing Agents

Design and Test

Academic Institutions

Export Program

Submit A Project

#### Search MOSIS

Search

#### http://www.mosis.com/Technical/Designrules/scmos/scmos-main.html#tech-codes

MOSIS SCMOS Technology Codes and Layer Maps

#### SCN4M and SCN4M SUBM

This is the layer map for the technology codes SCN4M and SCN4M\_SUBM using the MOSIS Scalable CMOS layout rules (<u>SCMOS</u>), and only for SCN4M and SCN4M\_SUBM. For designs that are laid out using other design rules (or <u>technology codes</u>), use the standard layer mapping conventions of that design rule set. For submissions in GDS format, the datatype is "O" (zero) unless specified in the map below.

SCN4M: Scalable CMOS N-well, 4 metal, 1 poly, silicided. Silicide block and thick oxide option available only on the TSMC process.

SCN4M\_SUBM: Uses revised layout rules for better fit to sub-micron processes (see MOSIS Scalable CMOS (SCMOS) Design Rules, section 2.4).

Fabricated on <u>TSMC</u>, <u>AMIS</u>, and <u>Agilent/HP</u> 0.35 micron process runs. See "Notes" section of layer map for foundry-specific options.

| Layer         | GDS | CIF | CIF Synonym | Rule<br>Section |           |                 | Notes                      |         |

|---------------|-----|-----|-------------|-----------------|-----------|-----------------|----------------------------|---------|

| N WELL        | 42  | CWN |             | <u>1</u>        |           |                 |                            |         |

| ACTIVE        | 43  | CAA |             | <u>2</u>        |           |                 |                            |         |

| THICK ACTIVE  | 60  | CTA |             | <u>24</u>       | Optional  | for TSMC; not a | available for Agilent/HP r | or AMIS |

| <u>DLY</u>    | 46  | CPG |             | <u>3</u>        |           |                 |                            |         |

| LICIDE BLOCK  | 29  | CSB |             | <u>20</u>       | Optional  | for Agilent/HP  | ; not available for AMI    |         |

| PLUS SELECT   | 45  | CSN |             | 4               |           |                 |                            |         |

| PLUS SELECT   | 44  | CSP |             | <u>4</u>        |           |                 |                            |         |

| <u>ONTACT</u> | 25  | ccc | CCG         | <u>5, 6, 13</u> |           |                 |                            |         |

| LY CONTACT    | 47  | CCP |             | <u>5</u>        | Can be re | eplaced by CON  | TACT                       |         |

| TIVE CONTACT  | 48  | CCA |             | <u>6</u>        | Can be re | eplaced by CON  | TACT                       |         |

| ETAL1         | 49  | CM1 | CMF         | 7               |           |                 |                            |         |

| <u> </u>      | 50  | CV1 | CVA         | <u>8</u>        |           |                 |                            |         |

| TAL2          | 51  | CM2 | CMS         | <u>9</u>        | l         |                 |                            |         |

| <u>42</u>     | 61  | CV2 | CVS         | <u>14</u>       |           | TSMC            | 0.35 micron                | 0.:     |

| AL3           | 62  | СМЗ | CMT         | <u>15</u>       |           |                 | 2P4M (4 Metal              |         |

| <u> 43</u>    | 30  | CA3 | CVT         | <u>21</u>       |           |                 | Polycided, 3.3             |         |

| <u>ΓΑL4</u>   | 31  | CM4 | CMQ         | <u>22</u>       |           |                 | V/5 V)                     |         |

| <u>ASS</u>    | 52  | COG |             | <u>10</u>       | l         |                 |                            |         |

| os            | 26  | ΧP  |             |                 | Non-fab I | ayer used to h  | ighlight pads              |         |

Comments

CX

Comments

#### MOSIS TSMC 0.35 2-POLY 4-METAL LAYERS

| MASK LAYER<br>NAME | MENTOR<br>NAME  | GDS<br># | COMMENT                               |

|--------------------|-----------------|----------|---------------------------------------|

| N WELL             | N_well.i        | 42       |                                       |

| ACTIVE             | Active.i        | 43       |                                       |

| POLY               | Poly.i          | 46       |                                       |

| N PLUS             | N_plus_select.i | 45       |                                       |

| P PLUS             | P_plus_select.i | 44       |                                       |

| CONTACT            | Contact.i       | 25       | Active_contact.i 48 poly_contact.i 47 |

| METAL1             | Metal1.i        | 49       |                                       |

| VIA                | Via.i           | 50       |                                       |

| METAL2             | Metal2.i        | 51       |                                       |

| VIA2               | Via2.i          | 61       | <b>Under Bump Metal</b>               |

| METAL3             | Metal3.i        | 62       | Solder Bump                           |

These are the main design layers up through metal two

#### MOSIS LAMBDA BASED DESIGN RULES

## http://www.mosis.com/design/rules/

© October 12, 2014 Dr. Lynn Fuller

#### MOSIS LAMBDA BASED DESIGN RULES

http://www.mosis.com/design/rules/

## **MOSIS** Educational Program

Instructional Processes Include: AMI  $\lambda = 0.8 \ \mu m$  SCMOS Rules AMI  $\lambda = 0.35 \ \mu m$  SCMOS Rules

Research Processes: go down to poly length of 65nm

Rochester Institute of Technology

## **MOSIS REQUIREMENTS**

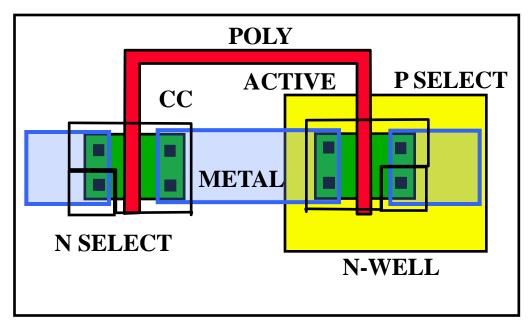

MOSIS requires that projects have successfully passed LVS (Layout Versus Schematic) and DRC (Design Rule Checking). The MENTOR tools for LVS and DRC (as they are set up at RIT) require separate N-select and P-select levels in order to know an NMOS transistor from a PMOS transistor. Although either an N-well, P-well or both will work for a twin well process, we have set up our DRC to look for N-well. (Also since we use a p-type starting wafer we can not have isolated p-wells but we can have isolated n-wells, thus drawing separate n-wells can be useful for some circuit designs.)

http://www.mosis.com

Rochester Institute of Technology

#### **LAYOUT**

# Digital Circuit Layout

Rochester Institute of Technology

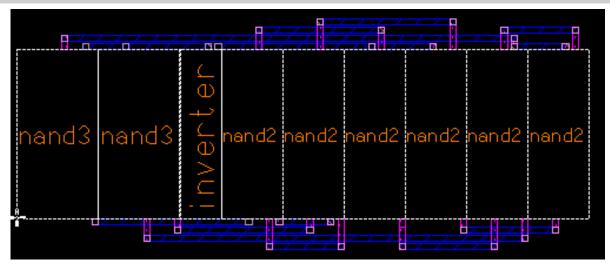

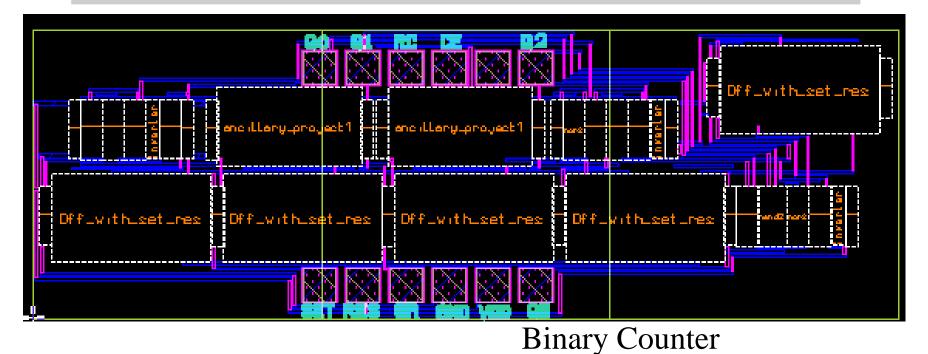

#### **DIGITAL CIRCUITS**

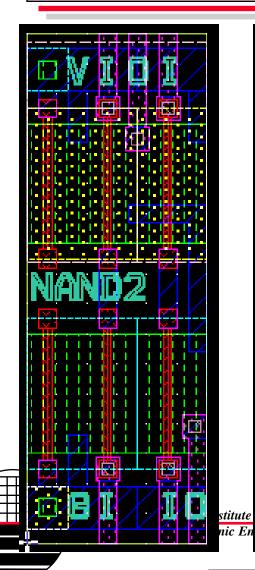

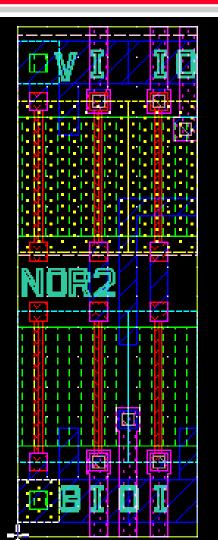

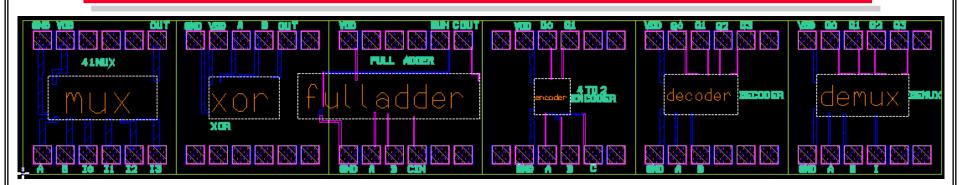

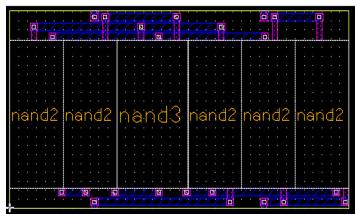

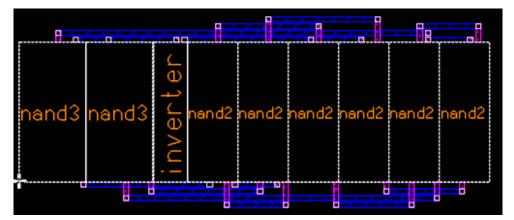

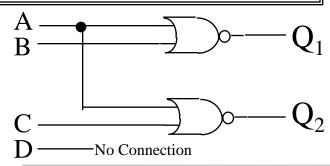

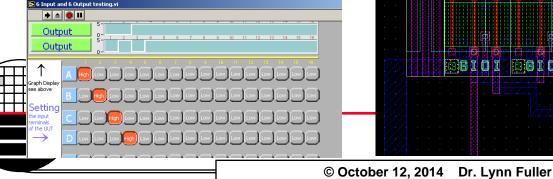

The design approach for digital circuits is to design primitive cells and then use the primitive cells to design basic cells which are then used in the project designs. A layout approach is also used that allows for easy assembly of these cells into more complex cells.

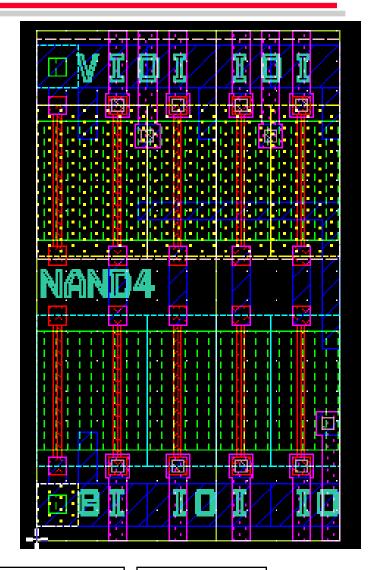

Primitive Cells INVERTER, NAND2,3,4, NOR2,3,4, NULL

**Basic Cells**

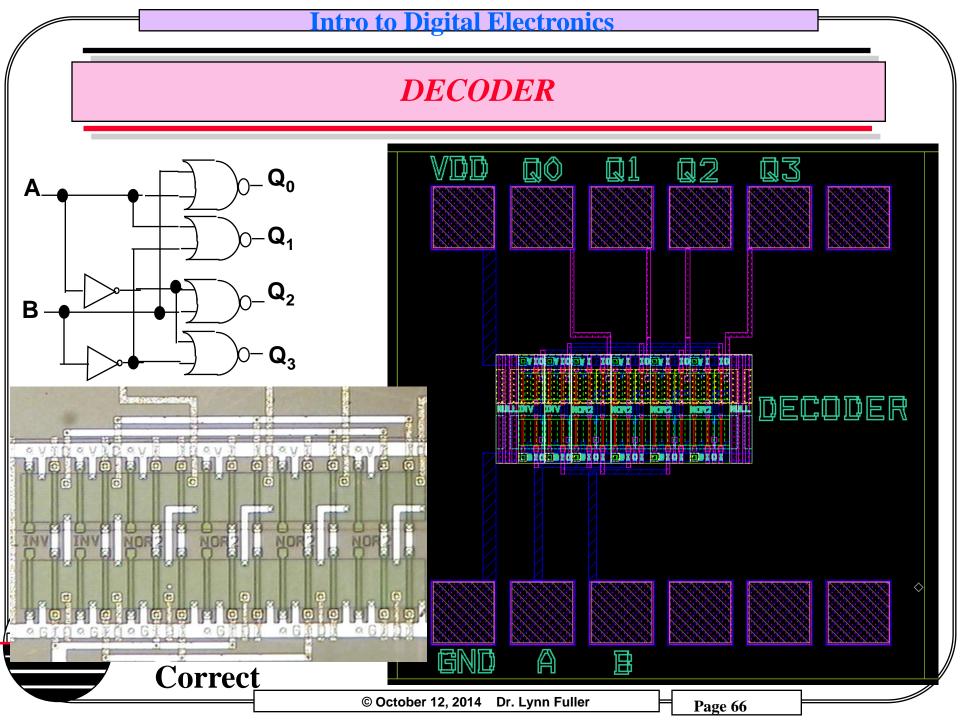

XOR, MUX, DEMUX, ENCODER, DECODER FULL ADDER, FLIP FLOPS

Macro Cells

BINARY COUNTER

SRAM

Rochester Institute of Technology

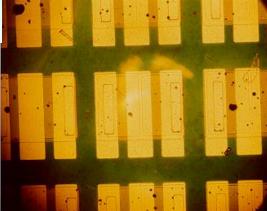

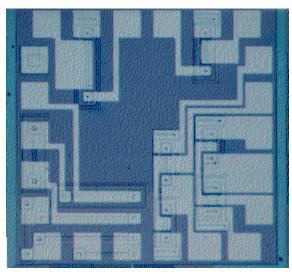

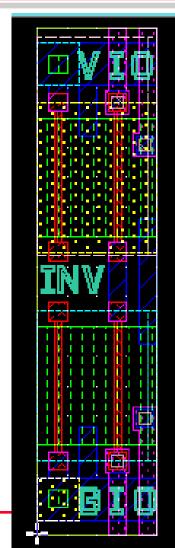

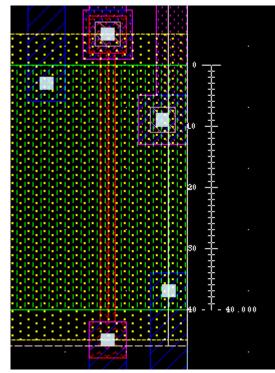

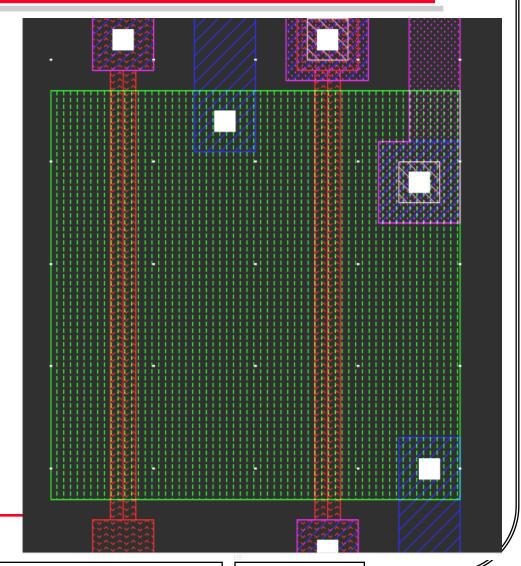

## Intro to Digital Electronics LAYOUT – GATE ARRAY **VDD** Green is Active **PMOS** Dashed Yellow is N-Well Red is Poly Blue is Metal-One Pink is Metal-Two White is Contact Cut Yellow is Via **NMOS** P and N select not shown **GND** Rochester Institute of Technology Microelectronic Engineering © October 12, 2014 Dr. Lynn Fuller Page 56

#### LAYOUT DETAILS FOR GATE ARRAY

- 1. Cells are separated from adjacent cells by off transistors

- 2. Well contacts are made at each of the off transistors

- 3. Metal-two connects thru Via to Metal-one

- 4. Metal-one connects thru Contact Cuts to active and Poly

- 5. Inputs and Outputs connections are made vertically with Metaltwo

- 6. Routing channels exist above and below the gate array and contain horizontal metal-one interconnects between cells, with Via to Metal-two.

- 7. The NULL cell at the end of the gate array row satisfy design rules for extension of well beyond active, etc. It also provides a vertical routing channel which may be useful in constructing macro cells.

#### **INVERTER**

#### **CMOS**

#### TRUTH TABLE

| VIN | VOUT |

|-----|------|

| 0   | 1    |

| 1   | 0    |

Rochester Institute of Technology

Microelectronic Engineering

$W = 40 \mu m$

$Ldrawn = 2.5 \mu m$

Lpoly =  $1.0\mu m$

$Leff = 0.35 \mu m$

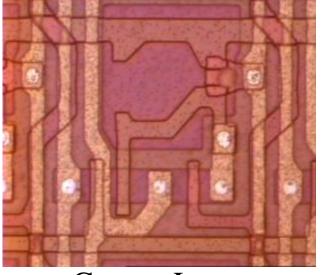

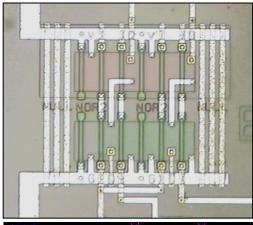

#### LAYOUT OF SOME PRIMITIVE CELLS

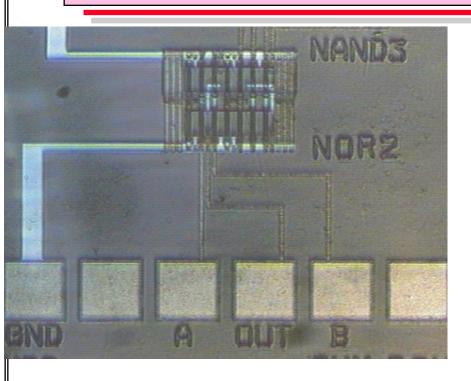

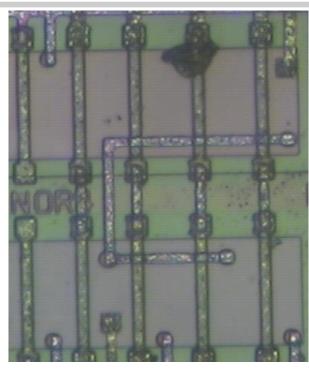

## **VERIFICATION NOR2 NAND3 FABRICATION & TEST**

NAND3

#### BASIC DIGITAL CELLS WITH PADS

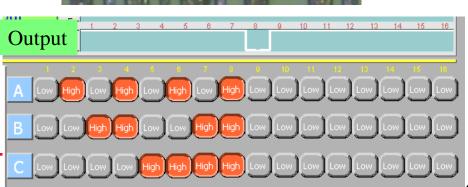

Multiplexer XOR Full Adder Encoder Decoder Demux

Edge Triggered D FF

JK FF

Rochester Institute of Technology

Microelectronic Engineering

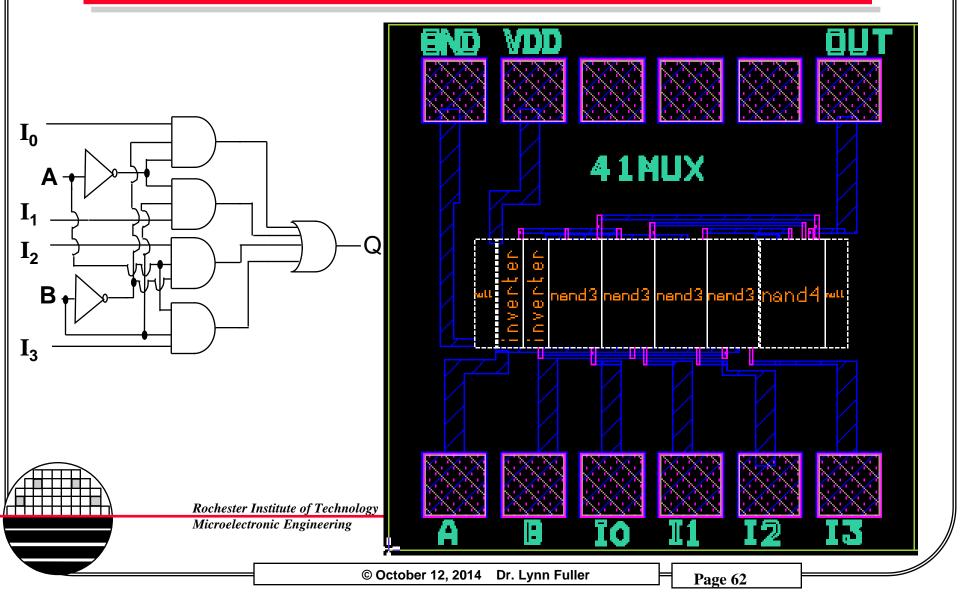

#### 4 TO 1 MULTIPLEXER

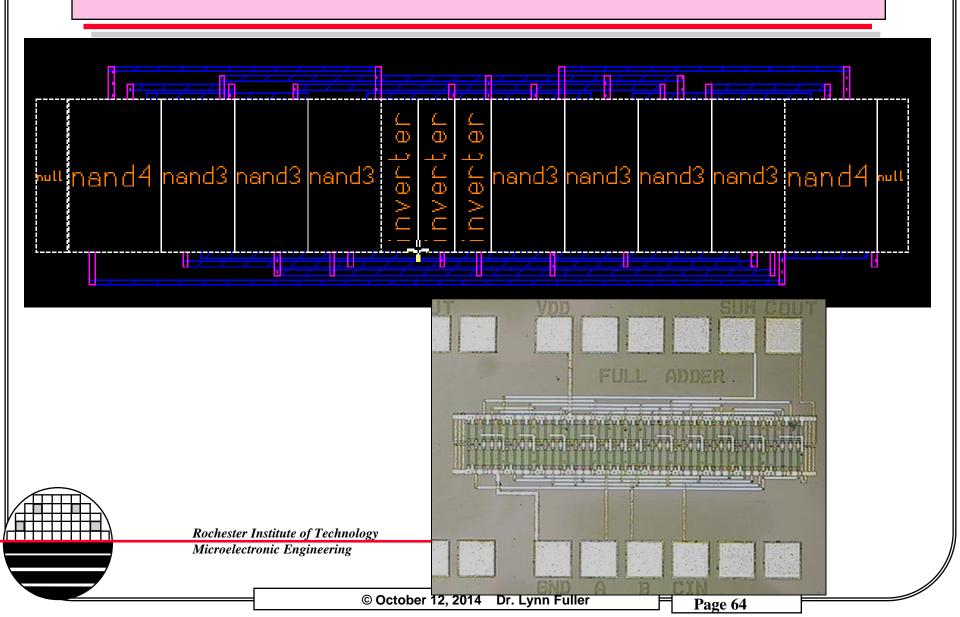

#### **FULL ADDER**

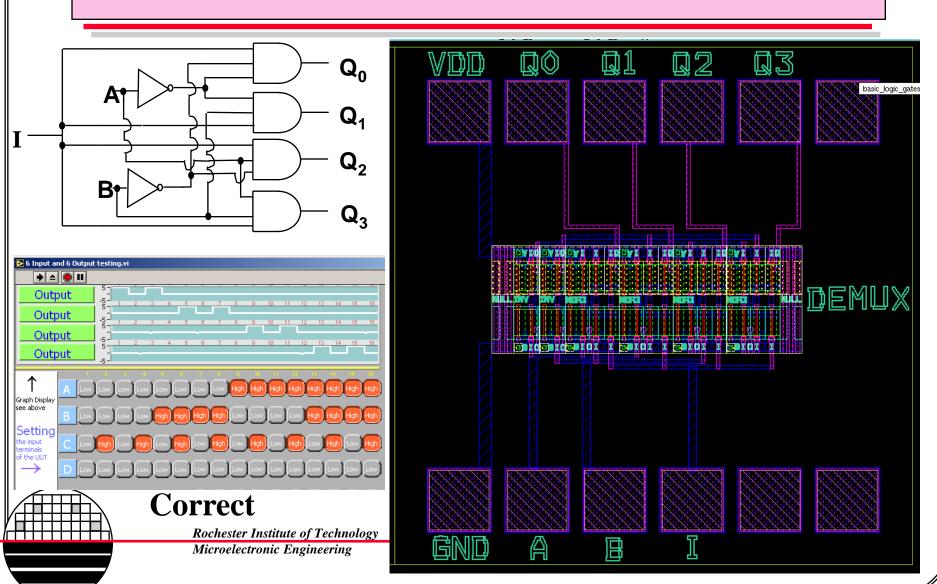

#### 1 TO 4 DEMULTIPLEXER

© October 12, 2014 Dr. Lynn Fuller

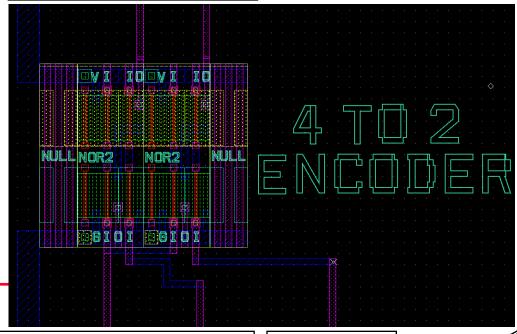

#### **ENCODER**

#### **Digital Encoder**

512 inputs can be coded into 9 lines which is a more dramatic benefit

| A | В | C | D | <b>Q</b> 0 | Q1 |

|---|---|---|---|------------|----|

| 1 | 0 | 0 | 0 | 0          | 0  |

| 0 | 1 | 0 | 0 | 0          | 1  |

| 0 | 0 | 1 | 0 | 1          | 0  |

| 0 | 0 | 0 | 1 | 1          | 1  |

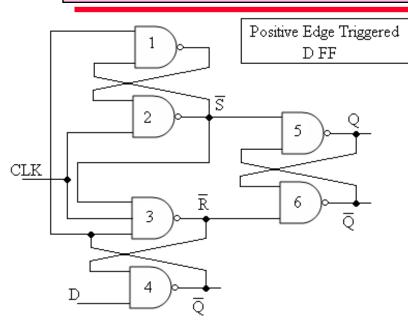

#### EDGE TRIGGERED D TYPE FLIP FLOP

Microelectronic Engineering

|   | Inp | uts        | Outputs |              |  |

|---|-----|------------|---------|--------------|--|

|   | D   | С          | Ċ       | <del>₹</del> |  |

|   | 0   | $\uparrow$ | 0       | 1            |  |

|   | 1   | $\uparrow$ | 1       | 0            |  |

|   | Х   | 0          | Q       | Q            |  |

|   | X   | 1          | Q       | Q            |  |

| l |     |            | ·       |              |  |

© October 12, 2014 Dr. Lynn Fuller

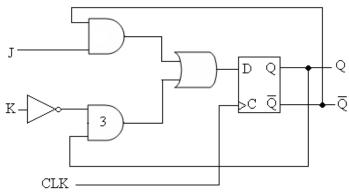

#### JK FLIP FLOP

| Positive Edge Triggered<br>JK FF |  |

|----------------------------------|--|

| J Q                              |  |

| Inputs | Outputs    |  |  |

|--------|------------|--|--|

| ЈКС    | ý Q<br>I   |  |  |

| 0 0 1  | 0 0        |  |  |

| 0 1 1  | 0 1        |  |  |

| 10 1   | <u>1</u> 0 |  |  |

| 1 1 1  | Q <u>Q</u> |  |  |

| X X 0  | Q <u>Q</u> |  |  |

| X X 1  | Q Q        |  |  |

|        |            |  |  |

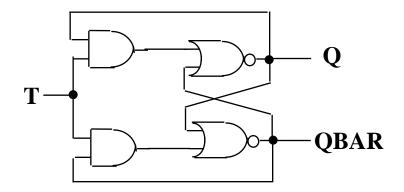

#### T-TYPE FILP-FLOP

#### TOGGEL FLIP FLOP

**Q:** Toggles High and Low with Each Input

| <u>T</u> | Qn-1 | Q |

|----------|------|---|

| 0        | 0    | 0 |

| 0        | 1    | 1 |

| 1        | 0    | 1 |

| 1        | 1    | 0 |

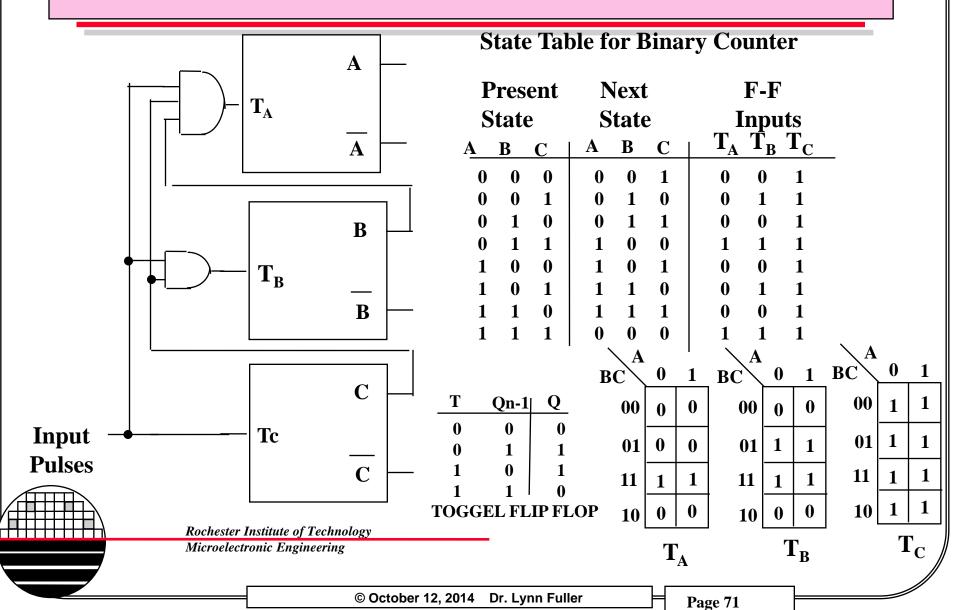

#### BINARY COUNTER USING T TYPE FLIP FLOPS

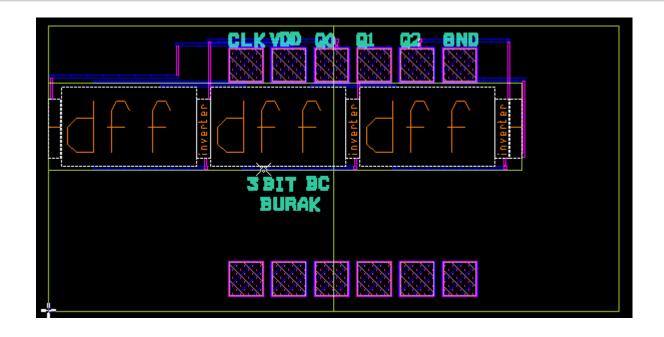

## 3-BIT BINARY COUNTER WITH D FLIP FLOPS

Rochester Institute of Technology

## **MACROCELLS**

# Binary Counter SRAM

Rochester Institute of Technology

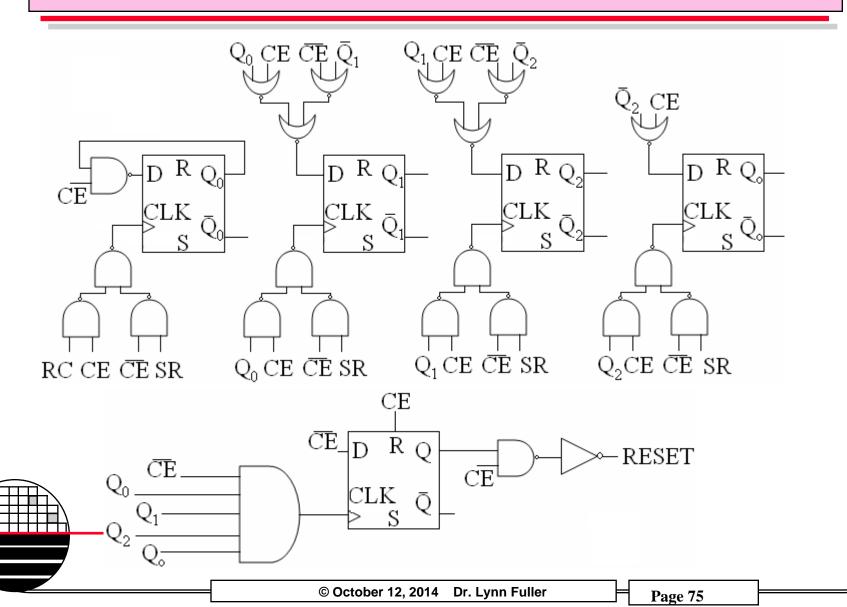

#### 3-BIT BINARY COUNTER/SHIFT REGISTER

Serial Output

Asynchronous Reset

Count Up Enable

Shift Out Clock Input

Count Up Clock Input

Start Bit and Stop Bit

# ADDITIONAL CIRCUITRY TO RESET, SHIFT, COUNT

## **MASKMAKING**

# Maskmaking

Rochester Institute of Technology

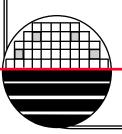

## MASK PROCESS FLOW

This process can take weeks and cost between \$1000 and \$20,000 for each mask depending on the design complexity.

#### OTHER MASKMAKING FEATURES

Fiducial Marks-marks on the edge of the mask used to align the mask to the stepper

Barcodes

**Titles**

Alignment Keys- marks on the wafer from a previous level used for wafer alignment

CD Resolution Targets- lines and spaces

Overlay Verniers- structures that allow measurement of x and y overlay accuracy

Tiling

Optical Proximity Correction (OPC)

Rochester Institute of Technology

# MEBES - Manufacturing Electron Beam Exposure System

Rochester Institute of Technology Microelectronic Engineering

#### **ASML RETICLE**

Chrome Side Mirrored 90° Chip Bottom at Bottom

> Rochester Institute of Technology Microelectronic Engineering

Non Chrome Side As loaded into Reticle Pod, Chrome Down, Reticle Pre-Alignment Stars Sticking out of Pod

#### ASML 5500/200

NA = 0.48 to 0.60 variable  $\sigma$ = 0.35 to 0.85 variable With Variable Kohler, or Variable Annular illumination Resolution = K1  $\lambda$ /NA =  $\sim 0.35 \mu m$  for NA=0.6,  $\sigma$  =0.85

Depth of Focus =  $k_2 \lambda/(NA)^2$ = > 1.0  $\mu$ m for NA = 0.6

i-Line Stepper  $\lambda = 365$  nm 22 x 27 mm Field Size

# **RIT SUB-CMOS PROCESS**

N-type Substrate 10 ohm-cm

# **RIT ADVANCED CMOS**

## 12 PHOTO LEVELS + 2 FOR EACH ADDITIONAL METAL LAYER

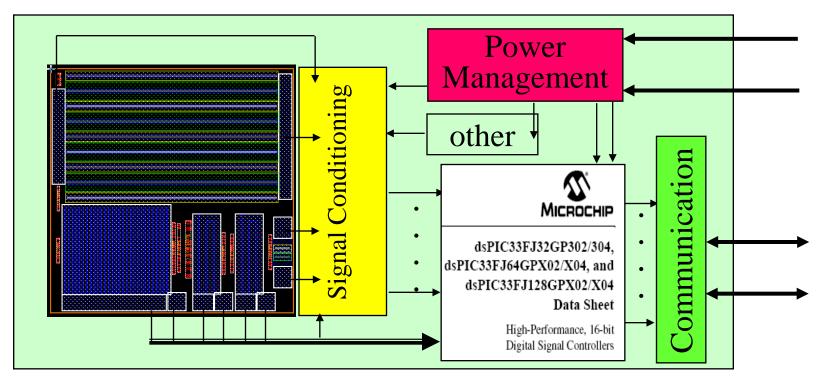

#### **MICROSYSTEM**

## Multi-Sensor MEMs Chip

#### Micro Controller

Signal Conditioning Electronics

#### REFERENCES

- 1. Silicon Processing for the VLSI Era, Volume 1 Process Technology, 2<sup>nd</sup>, S. Wolf and R.N. Tauber, Lattice Press.

- 2. The Science and Engineering of Microelectronic Fabrication, Stephen A. Campbell, Oxford University Press, 1996.

- 3. MOSIS Scalable CMOS Design Rules for Generic CMOS Processes, <a href="www.mosis.org">www.mosis.org</a>, and <a href="http://www.mosis.com/design/rules/">http://www.mosis.com/design/rules/</a>

#### HOMEWORK – INTRO TO DIGITAL ELECTRONICS

- 1. Do a SPICE simulation to obtain the VTC for the inverter shown on page 16. Let the load resistor be 10K, the NMOS transistor SPICE model RITSUBN7, L=1u and W=40u. Extract Voh, Vol, Vil, ViH, Vinv, Noise Margin Low, Noise Margin High and Maximum current.

- 2. Do a SPICE simulation to obtain the VTC for the inverter shown on page 20. Let the NMOS and PMOS transistor SPICE model RITSUBN7 and RITSUBP7, L=1u and W=40u. Extract Voh, Vol, Vil, ViH, Vinv, Noise Margin Low, Noise Margin High and Maximum current.

- 3. Do a SPICE simulation to obtain the RISE TIME and FALL TIME for the inverter in problem 2 with a load capacitance equal to a fan out of 5 gates.

- 4. Show that the XOR realized with AND and OR gates is equivalent to an all NAND gate realization.

### TRANSISTOR DIMENSIONS

L=2u

W=40u

$Ad=As=40u \times 17u$

=680p

Pd=Ps=2x(40u+17u)

=114u

Rd=Rs=100 ohm

Rochester Institute of Technology Microelectronic Engineering