#### **DOUBLE EXPOSURE FOR MOSFET POLYSILICON GATES**

By Alycia Roux Microelectronic Engineering MCEE 550 – CMOS Processing Fall 2013 Instructors: Stephanie Bolster and Lynn Fuller

#### **MOTIVATION**

- Polysilicon gate size is currently set by mask dimensions

(Smallest gate length on sub-cmos factory mask = 1 μm)

- Masks are expensive and time consuming to make

- ASML stepper has the ability to expose a wafer twice using the same mask and a small shift for the second exposure (double exposure)

- GOAL: To determine a method of double exposing a wafer in order to obtain smaller polysilicon gate lengths.

#### ASML 5500/200 Stepper

NA = 0.48 to 0.60 variable  $\sigma$ = 0.35 to 0.85 variable With Variable Kohler, or Variable Annular illumination Resolution = K1  $\lambda$ /NA = ~ 0.35 µm for NA=0.6,  $\sigma$  =0.85 Depth of Focus = k<sub>2</sub>  $\lambda$ /(NA)<sup>2</sup> = > 1.0 µm for NA = 0.6

i-Line Stepper  $\lambda = 365$  nm 22 x 27 mm Field Size

#### **PROCESS FLOW**

Coat, Expose with JG Active and Zero Level masks, and develop

2. Etch Silicon using Zero Etch recipe in the Drytek Quad and ash photoresist

3. Coat and Double Expose using JG Poly mask and develop

$R \cdot I \cdot T$

4

#### **DOUBLE EXPOSURE ON THE ASML**

Setting up the Double Exposure:

Main Menu → Job Definition → Modify Job → Select "poly\_double\_expo"

$\circ Wafer \ layout \rightarrow Image \ distribution$

- In this window, type \*, \* in the x, y cell Index and hit the Enter key after each

- Select image 2 (click the 3 bottom cells on the wafer layout)

- Hit Delete

$\mathbf{R} \cdot \mathbf{I} \cdot \mathbf{T}$

- Put desired shift into Y (mm) and hit Enter and click Apply

- Click Exit and continue the exposure as normal

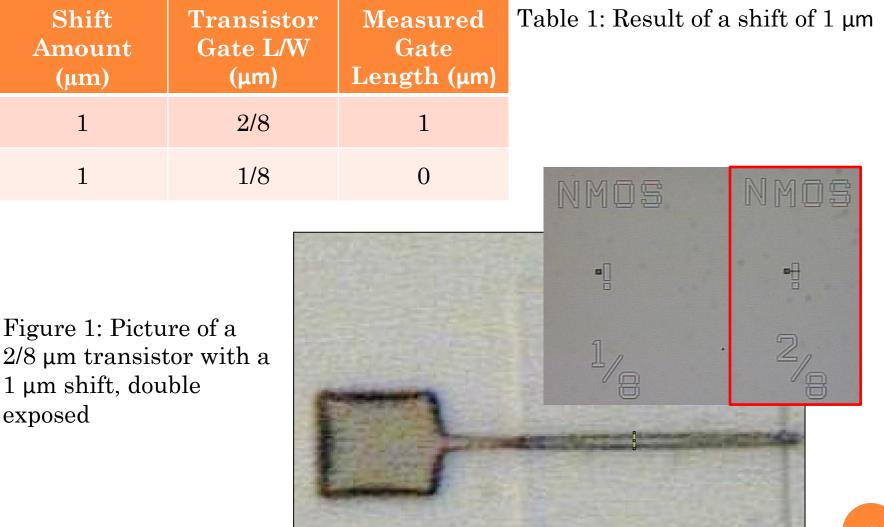

#### SHIFTS AND RESULTS

# $\mathbf{R} \cdot \mathbf{I} \cdot \mathbf{T}$

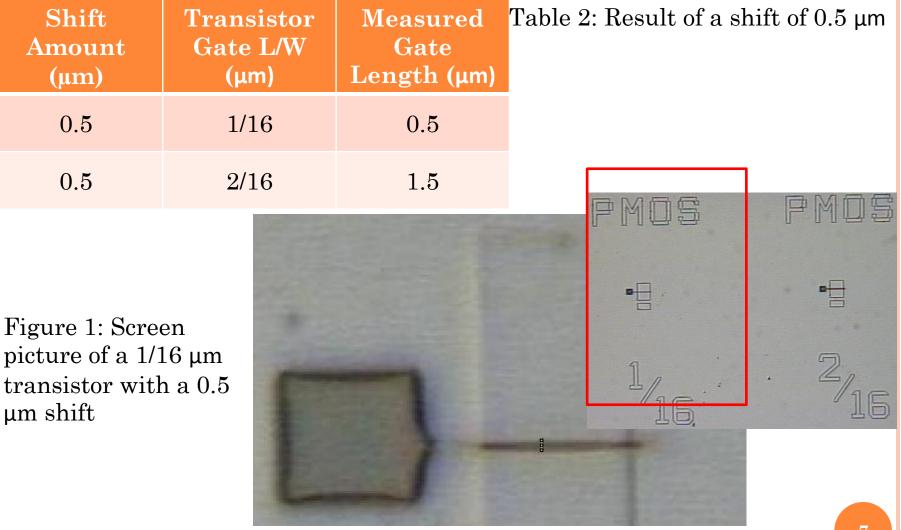

## SHIFTS AND RESULTS (CONTINUED)

# $R{\cdot}I{\cdot}T$

## SHIFTS AND RESULTS (CONTINUED)

#### **Exposure Matrix Dose Layout**

| 10<br>0 | 12<br>5 | 15<br>0 | 17<br>5 | 20<br>0 | 22<br>5 | 25<br>0 | 27<br>5 | 30<br>0 |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |         |

$\mathbf{R} \cdot \mathbf{I} \cdot \mathbf{T}$

To determine best exposure dose, exposure matrix was used with a center dose of 200 mJ/cm<sup>2</sup> and a step of 25 mJ/cm<sup>2</sup>. Exposure dose layout on the wafer is shown.

## SHIFTS AND RESULTS (CONTINUED)

Table 3: Result of a shift of 0.75  $\mu$ m at different exposure doses at 1/16  $\mu$ m transistors in the same die row (except for the 125 mJ/cm<sup>2</sup> dose which was a 1/8 transistor)

| Dose<br>(mJ/cm²) | Measured<br>Gate<br>Length<br>(µm) |  |

|------------------|------------------------------------|--|

| 100              | 1                                  |  |

| 125              | 0.875                              |  |

| 150              | 0.625                              |  |

| 175              | 0.375                              |  |

| 200 and up       | unattached                         |  |

#### **SUMMARY**

- Double exposure allows for smaller gate lengths.

- Size of an isolated photoresist line also depends on exposure dose.

- Height differences in the wafer surface affects photoresist size. (effect of different substrate reflection)

- Gate lengths below the resolution limit should be possible (i.e. <0.3um)