ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

# **CMOS Testchip 2009**

# Burak Baylav, Dr. Dhireesha Kudithipudi Dr. Lynn Fuller

Webpage: http://people.rit.edu/lffeee Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Fax (585) 475-5041 Email: Lynn.Fuller@rit.edu Department webpage: http://www.microe.rit.edu

Rochester Institute of Technology

Microelectronic Engineering

1-2-2010 CMOSTestchip2009.ppt

© January 2, 2010 Dr. Lynn Fuller

# **OUTLINE**

Introduction **Process Technology Design Rules** Chip Floor Plan **Structures for Fabrication Process and Evaluation** Sensors **Digital Circuits** Analog Circuits Projects References

**Rochester Institute of Technology**

Microelectronic Engineering

<u>CMOS Testchip 2009</u>

#### **INTRODUCTION**

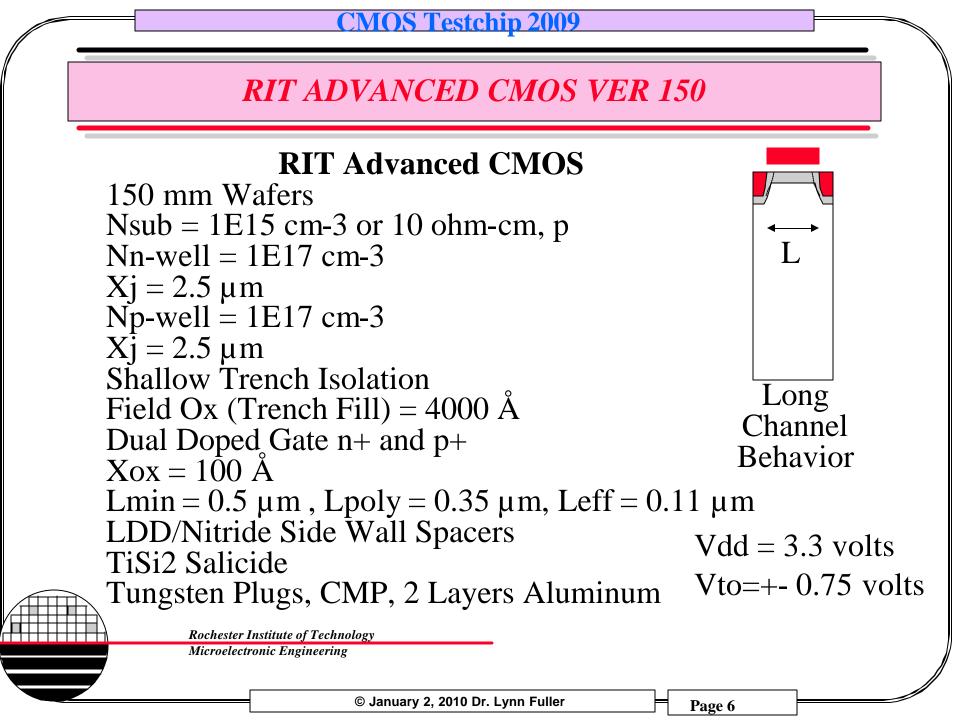

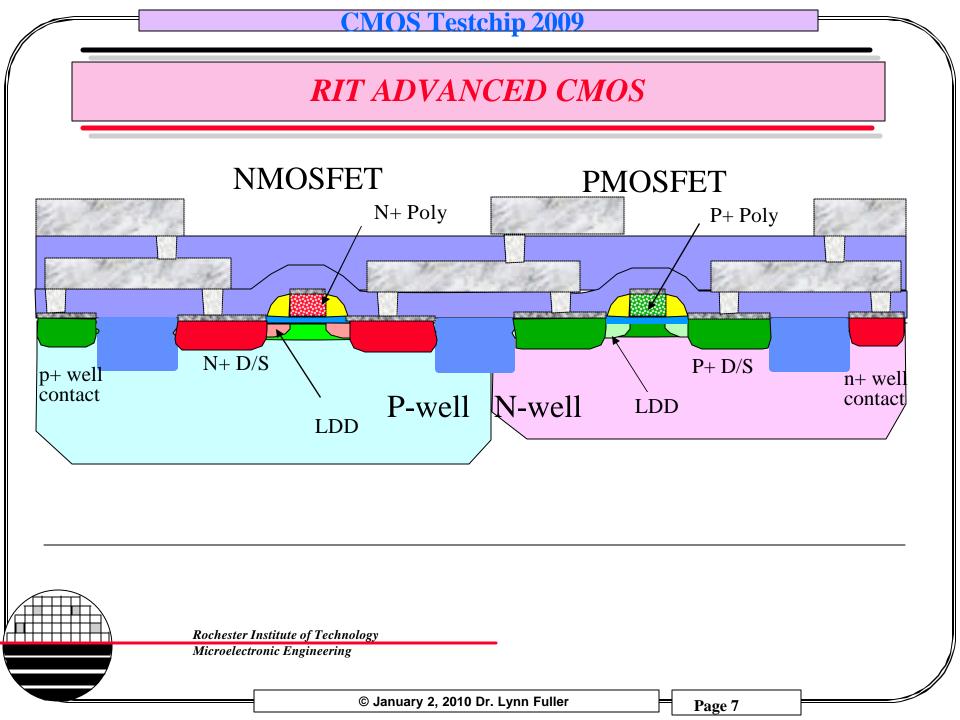

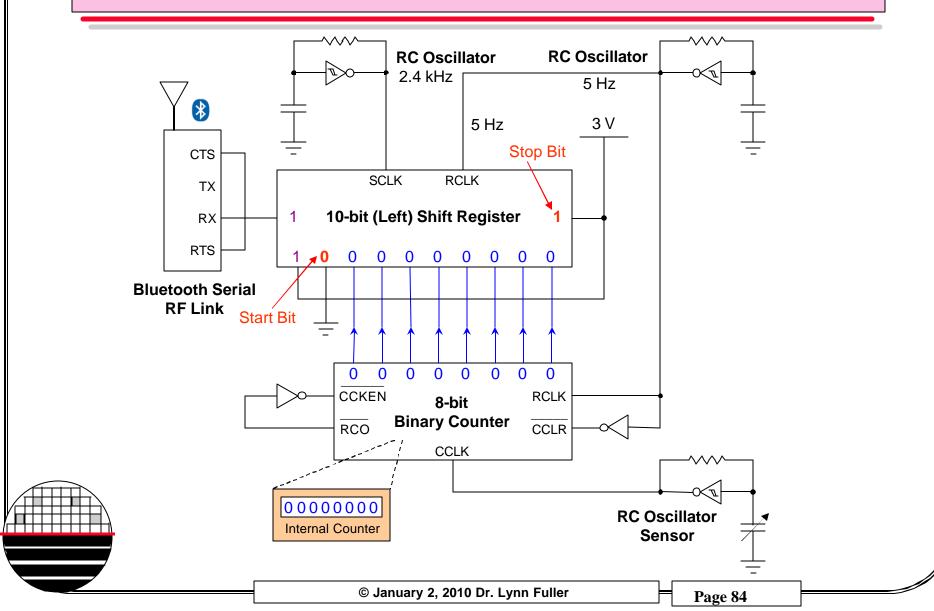

This document will describe a new CMOS test chip. The test chip will be used to develop CMOS process technology and to verify analog and digital circuit designs. In addition the test chip includes a variety of CMOS compatible sensors and signal processing electronics for those sensors. A section of the chip is for manufacturing process characterization and transistor parametric characterization. Other sections of the chip have basic digital and analog circuits, chip scale packaging designs and projects to evaluate various Microsystems architectures. For example a variable frequency oscillator, binary counter and shift register allows for capacitor sensor measurement and Blue-Tooth wireless transmission of data to a remote host. The test chip will be used with RIT's SUB-CMOS and ADV-CMOS processes.

**Rochester Institute of Technology**

Microelectronic Engineering

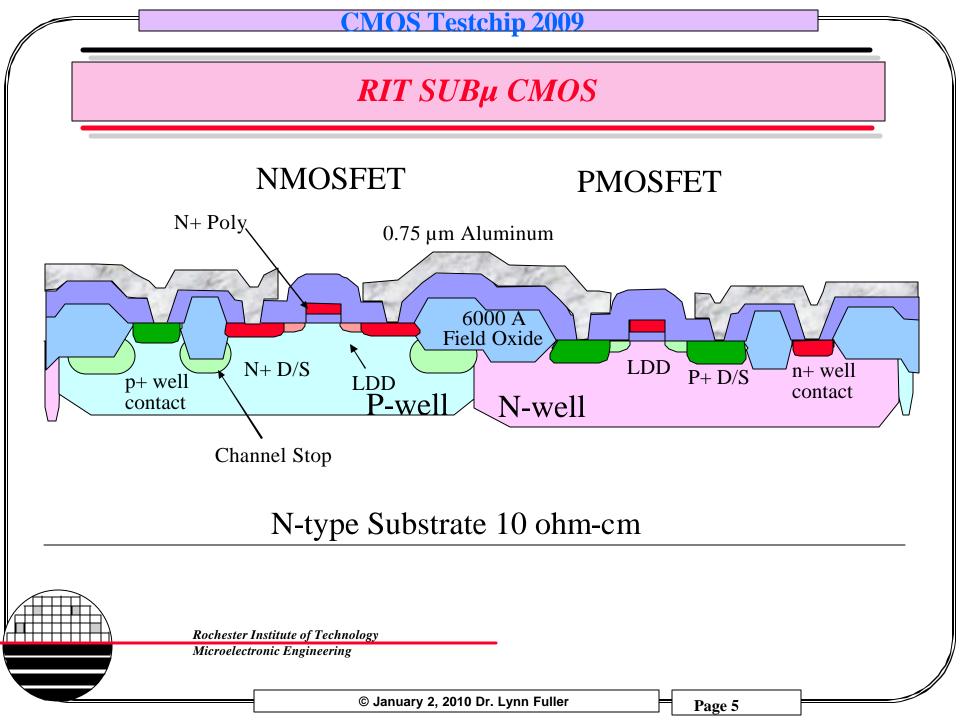

# RIT SUBµ CMOS

#### **RIT Subµ CMOS** 150 mm wafers Nsub = 1E15 cm-3Nn-well = 3E16 cm-3 $X_{j} = 2.5 \,\mu m$ Np-well = 1E16 cm-3 $X_{i} = 3.0 \,\mu m$ LOCOS Field Ox = 6000 ÅXox = 150 Å $Lmin=1.0 \mu m$ LDD/Side Wall Spacers 2 Layers Aluminum

Rochester Institute of Technology

Microelectronic Engineering

#### **DESIGN RULES**

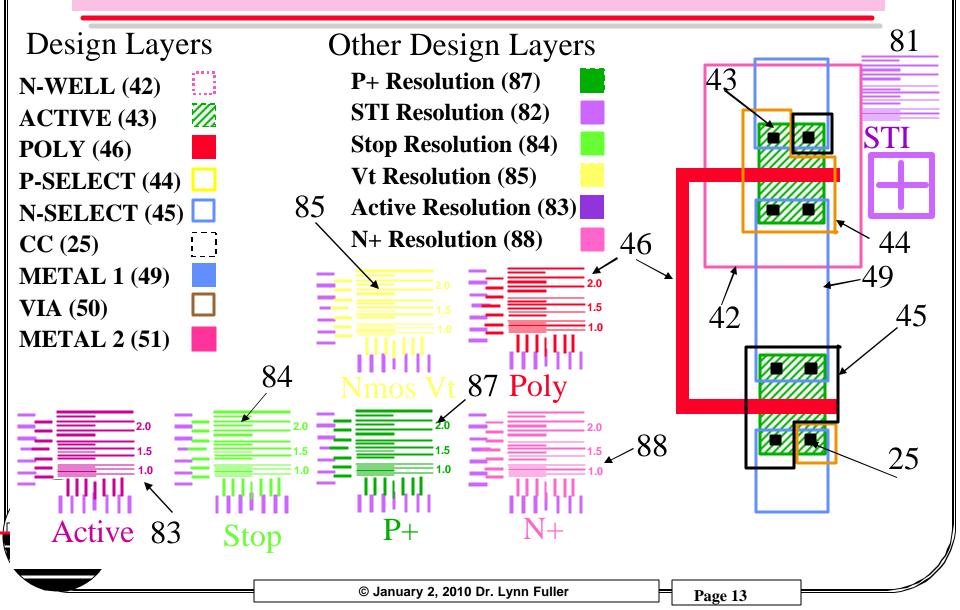

We will use a modified version of the MOSIS TSMC 0.35 2P 4M design rules. Eventually we hope to be compatible with MOSIS but new process technology needs to be developed at RIT to do that (PECVD Tungsten, improved lithography overlay, 4 layer metal). We plan to use one layer of poly and two layers of metal. We will use the same design layer numbers with additional layers as defined on the following pages for manufacturing/maskmaking enhancements. Many of the designs will use minimum drawn poly gate lengths of 2µm where circuit architecture is the main purpose of the design. Minimum size devices (Drawn Poly =  $0.5\mu$ m, etc.) are included to develop manufacturing process technology. These transistors (0.5µm drawn) yield 0.35µm Leff and are equivalent to the TSMC 0.35µm transistors.

**Rochester Institute of Technology**

Microelectronic Engineering

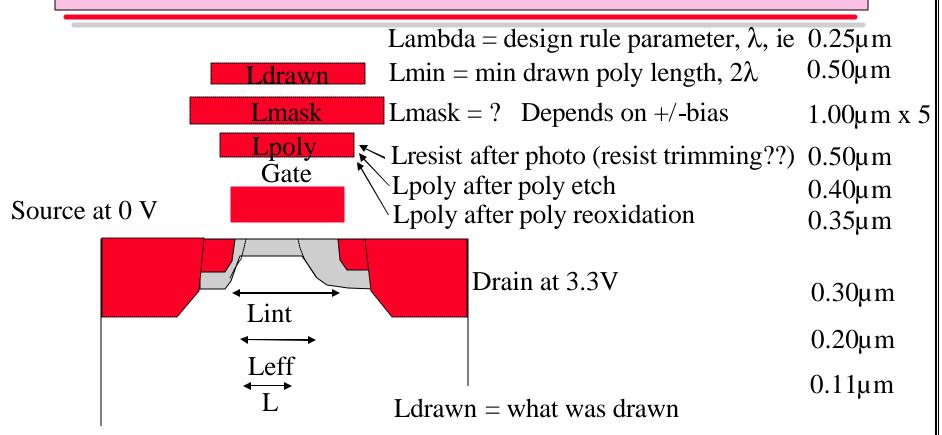

# LAMBDA, Lmin, Ldrawn, Lmask, Lpoly, Lint, Leff, L

Internal Channel Length, Lint =distance between junctions, including under diffusion Effective Channel Length, Leff = distance between space charge layers, Vd = Vs = 0Channel Length, L, = distance between space charge layers, when Vd= what it is Extracted Channel Length Parameters = anything that makes the fit good (not real)

#### **MOSIS TSMC 0.35 2POLY 4 METAL PROCESS**

#### **General Information**

About MOSIS Products Processes Prices Support User Group Events Job Openings News

#### Work with MOSIS

<u>Overview</u> <u>Getting Started</u> <u>Design and Test</u>

#### Requests

<u>Run Status</u> <u>Project Status</u> <u>Test Data</u>

Docs and Forms Documents

Forms/Agreements Web Forms

#### **Quick Reference**

New Users Experienced Users Purchasing Agents Design and Test Academic Institutions Export Program Submit A Project

#### Search MOSIS

Search

#### http://www.mosis.com/Technical/Designrules/scmos/scmos-main.html#tech-codes

#### MOSIS SCMOS Technology Codes and Layer Maps SCN4M and SCN4M SUBM

This is the layer map for the technology codes SCN4M and SCN4M\_SUBM using the MOSIS Scalable CMOS layout rules (<u>SCMOS</u>), and only for SCN4M and SCN4M\_SUBM. For designs that are laid out using other design rules (or <u>technology</u> <u>codes</u>), use the standard layer mapping conventions of that design rule set. For submissions in GDS format, the datatype is "0" (zero) unless specified in the map below.

SCN4M: Scalable CMOS N-well, 4 metal, 1 poly, silicided. Silicide block and thick oxide option available only on the TSMC process.

SCN4M\_SUBM: Uses revised layout rules for better fit to sub-micron processes (see MOSIS Scalable CMOS (SCMOS) Design Rules, <u>section 2.4</u>).

Fabricated on <u>TSMC</u>, <u>AMIS</u>, and <u>Agilent/HP</u> 0.35 micron process runs. See "Notes" section of layer map for foundry-specific options.

| Layer                | GDS | CIF | CIF Synonym | Rule<br>Section              |          |                 | Notes                    |          |        |  |  |  |

|----------------------|-----|-----|-------------|------------------------------|----------|-----------------|--------------------------|----------|--------|--|--|--|

| N WELL               |     | CWN |             | 1                            |          |                 |                          |          |        |  |  |  |

| ACTIVE               | 43  | CAA |             | 2                            |          |                 |                          |          |        |  |  |  |

| THICK ACTIVE         | 60  | СТА |             | <u>24</u>                    | Optional | for TSMC; not   | available for Agilent/HP | nor AMIS |        |  |  |  |

| POLY                 | 46  | CPG |             | <u>3</u>                     | 1        |                 |                          |          |        |  |  |  |

| SILICIDE BLOCK       | 29  | CSB |             | <u>20</u>                    | Optional | for Agilent/HF  | ; not available for AMI  |          |        |  |  |  |

| <u>N PLUS SELECT</u> | 45  | CSN |             | 4                            | ł        |                 |                          |          |        |  |  |  |

| <u>P PLUS SELECT</u> | 44  | CSP |             | <u>4</u>                     | Ł        |                 |                          |          |        |  |  |  |

| <u>CONTACT</u>       | 25  | ccc | CCG         | <u>5, 6, 13</u>              | 1        |                 |                          |          |        |  |  |  |

| POLY CONTACT         | 47  | ССР |             | 5 Can be replaced by CONTACT |          |                 |                          |          |        |  |  |  |

| ACTIVE CONTACT       | 48  | CCA |             | <u>6</u>                     | Can be r | eplaced by CO   | NTACT                    |          |        |  |  |  |

| METAL1               | 49  | CM1 | CMF         | 7                            | _        |                 |                          |          |        |  |  |  |

| VIA                  | 50  | CV1 | CVA         | <u>8</u>                     | 1        |                 |                          |          |        |  |  |  |

| METAL2               | 51  | CM2 | CMS         | <u>9</u>                     | <u>l</u> |                 |                          |          |        |  |  |  |

| <u>VIA2</u>          | 61  | CV2 | CVS         | <u>14</u>                    | Ł        | TSMC            | 0.35 micron              | 0.25     | SCN4ME |  |  |  |

| METAL3               | 62  | смз | CMT         | <u>15</u>                    | i        |                 | 2P4M (4 Metal            |          |        |  |  |  |

| VIA3                 | 30  | суз | CVT         | <u>21</u>                    |          |                 | Polycided, 3.3           |          |        |  |  |  |

| METAL4               | 31  | CM4 | CMQ         | <u>22</u>                    | 2        |                 | V/5 V)                   |          |        |  |  |  |

| GLASS                | 52  | COG |             | <u>10</u>                    | <u>l</u> | i               | i                        | i        | i      |  |  |  |

| PADS                 | 26  | ХР  |             |                              | Non-fab  | layer used to l | nighlight pads           |          |        |  |  |  |

| Comments             |     | сх  |             |                              | Commen   | its             |                          |          |        |  |  |  |

© January 2, 2010 Dr. Lynn Fuller

### MOSIS TSMC 0.35 2-POLY 4-METAL LAYERS

| MASK<br>LAYER NAME | MENTOR<br>NAME                        | GDS<br># | COMMENT                                  |

|--------------------|---------------------------------------|----------|------------------------------------------|

| N WELL             | N_well.i                              | 42       |                                          |

| ACTIVE             | Active.i                              | 43       |                                          |

| POLY               | Poly.i                                | 46       |                                          |

| N PLUS             | N_plus_select.i                       | 45       |                                          |

| P PLUS             | P_plus_select.i                       | 44       |                                          |

| CONTACT            | Contact.i                             | 25       | Active_contact.i 48<br>poly_contact.i 47 |

| METAL1             | Metal1.i                              | 49       |                                          |

| VIA                | Via.i                                 | 50       |                                          |

| METAL2             | Metal2.i                              | 51       |                                          |

| VIA2               | Via2.i                                | 61       | Under Bump Metal                         |

| METAL3             | Metal3.i                              | 62       | Solder Bump                              |

| These are t        | he main design<br>© January 2, 2010 D | ~        | up through metal two                     |

### MORE LAYERS USED IN MASK MAKING

| LAYER | NAME                            | GDS | COMMENT                                                      |  |  |  |  |  |

|-------|---------------------------------|-----|--------------------------------------------------------------|--|--|--|--|--|

|       | cell_outline.i                  | 70  | Not used                                                     |  |  |  |  |  |

|       | alignment                       | 81  | Placed on first level mask                                   |  |  |  |  |  |

|       | nw_res                          | 82  | Placed on nwell level mask                                   |  |  |  |  |  |

|       | active_lettering                | 83  | Placed on active mask                                        |  |  |  |  |  |

|       | channel_stop                    | 84  | <b>Overlay/Resolution for Stop Mask</b>                      |  |  |  |  |  |

|       | pmos_vt                         | 85  | <b>Overlay/Resolution for Vt Mask</b>                        |  |  |  |  |  |

|       | LDD                             | 86  | <b>Overlay/Resolution for LDD Masks</b>                      |  |  |  |  |  |

|       | p plus                          | 87  | Overlay/Resolution for P+ MaskOverlay/Resolution for N+ Mask |  |  |  |  |  |

|       | n plus                          | 88  |                                                              |  |  |  |  |  |

|       | tile_exclusion                  | 89  | Areas for no STI tiling                                      |  |  |  |  |  |

| Ra    | chester Institute of Technology | 1   | These are the additional layer                               |  |  |  |  |  |

|       | croelectronic Engineering       |     | used in layout and mask mak                                  |  |  |  |  |  |

# **OTHER LAYERS**

# MASK ORDER FORM

|          |            | uto of Tocha<br>Engineering |           | Date 6/25/2008<br>Requester Dr. Lynn Fuller |             |          |              |             |                 |          |         |             |

|----------|------------|-----------------------------|-----------|---------------------------------------------|-------------|----------|--------------|-------------|-----------------|----------|---------|-------------|

| Attech   | iont far l | Mark Order F                |           |                                             |             |          |              |             |                 |          |         | -           |

| Dariqa O | )escripti  | CMOS_TESTC                  | HIP_2008_ | final                                       | - 1         | de Fila  | e Isharodien | nartestch   | ip_2007/CM      | OS_TES   | TCHIP_2 | 008_final.q |

| turo Ro  | relation   | 0.5                         | 1         | Mirrar                                      | 135         | 1,       | Plate Size   |             | 5"×5"×0.09      | ō-       |         |             |

| Sceld    | • Fector   | 58                          | 1         | Rutate                                      | none        | ]        | a of laws    | - ledy lat  | . 1             |          |         |             |

|          | Arrey      | none                        | J         |                                             |             |          |              |             |                 |          |         |             |

| Design   |            | Hark                        |           |                                             |             |          |              |             |                 |          |         |             |

| Layer    |            | Lavel                       |           |                                             |             |          |              |             |                 |          |         |             |

| Hame     | Humber     |                             | Humber    |                                             |             |          | Common       | tr 👘        |                 |          |         |             |

| NWELL    | 1          | ntuelli                     |           | (42 OR 81                                   | OR \$2) IN  | VERT     | DarkField    | Mark        |                 |          | _       |             |

|          |            | alignment                   | 81        |                                             |             |          |              |             |                 |          |         |             |

|          |            | nu_rer                      | 82        |                                             |             |          |              |             |                 |          |         |             |

| ACTIVE   | 2          | activo-aroa.i               |           | (43 OR 83                                   | 0           |          | Clear Field  | Mark        |                 |          |         |             |

|          |            | activo-aroa.o               | 83        |                                             |             |          |              |             |                 | <u> </u> | _       |             |

| STOP     | Э          | n-well.i                    | 42        | (42 OR 84                                   | 0           |          | Cloar Field  | Mark        |                 | <u> </u> | _       |             |

|          |            | channel_stop                | 84        |                                             |             |          |              |             |                 |          | _       |             |

| PMOSVT   | 4          | p_plur_roloct.i             | 44        | (44 OR 85                                   | <u>)</u>    |          | DarkField    | Mark        |                 |          | _       |             |

|          |            | pmar_vt                     | 85        |                                             |             |          |              |             |                 |          | _       |             |

| POLY     | 5          | paly.i                      | 46        | nane                                        |             |          |              |             | ar layor 6 +0.9 | iµm      | _       |             |

| LDD-N    | 6          | n_plur_roloct.i             |           | (45 OR 86                                   | ) INVERT    |          | Dark Field I | <u>Mark</u> |                 |          | _       |             |

|          |            | LDD                         | 86        |                                             |             |          |              |             |                 | <u> </u> | _       |             |

| LDD-P    | 7          | p_plur_roloct.i             |           | (44 OR 86                                   | ) INVERT    |          | DarkField    | <u>Mark</u> |                 |          | _       |             |

|          |            | LDD                         | 86        |                                             |             |          |              |             |                 | <u> </u> | _       |             |

| N+DS     | 3          | n_plur_roloct.i             |           | (45 OR 88                                   | E) INVERT   |          | DarkField    | <u>Mark</u> |                 | <u> </u> | _       |             |

|          |            | nplur                       | 88        |                                             |             |          |              |             |                 | <u> </u> | _       |             |

| P+DS     | 9          | p_plur_roloct.i             |           | (44 OR 87                                   | () INVERT   |          | DarkField    | <u>Mark</u> |                 | <u> </u> | _       |             |

|          |            | pplur                       | 87        |                                             |             |          |              |             |                 | <b>I</b> | _       |             |

| CC       | 10         | contact                     |           | (25 OR 81                                   | 7 OR 47) IN | IVERT    | DarkField    | Mark        |                 | <b>I</b> | _       |             |

|          | · ·        | Active_contact              |           |                                             |             | <u> </u> |              |             | <u> </u>        |          | _       |             |

|          |            | Poly_contact.i              | 47        |                                             |             | <u> </u> |              |             | <u> </u>        |          | _       |             |

| METAL1   | 11         | motal1.i                    | 49        | none                                        |             |          | Clear Field  |             |                 |          | _       |             |

| VIA      | 12         | Via.i                       | 50        | INVERT                                      |             |          | Dark Field I | Mark        |                 | -        | _       |             |

|          |            |                             |           |                                             |             |          |              |             |                 | -        | _       |             |

| METAL2   | 13         | motal2.i                    | 51        | none                                        |             |          | Clear Field  |             |                 | -        | _       |             |

| VIA2     | 14         | Via2                        | 61        | nane                                        |             |          | DarkField    |             |                 | -        | _       |             |

| METAL3   | 15         | motal3                      | 62        | none                                        |             |          | Cloar Field  | Mark        |                 |          |         |             |

© January 2, 2010 Dr. Lynn Fuller

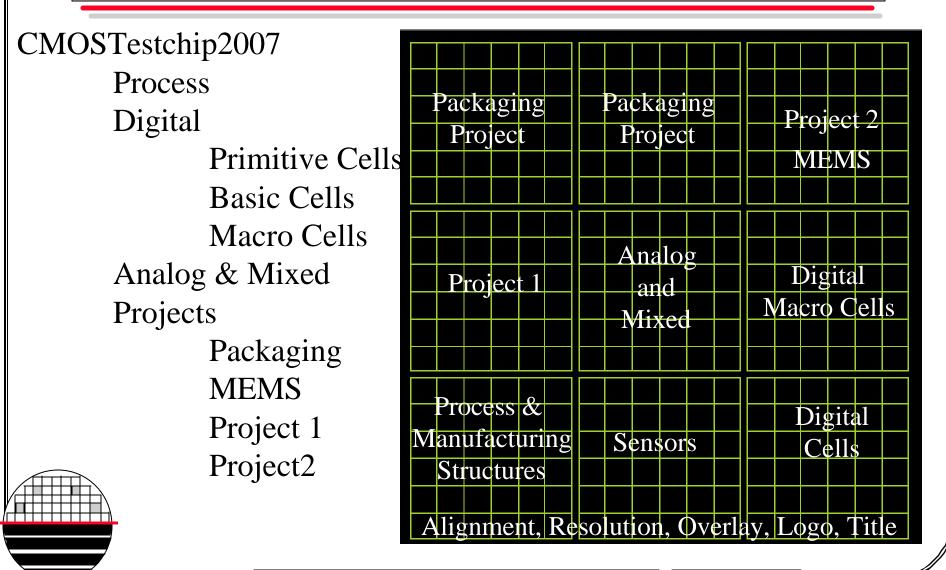

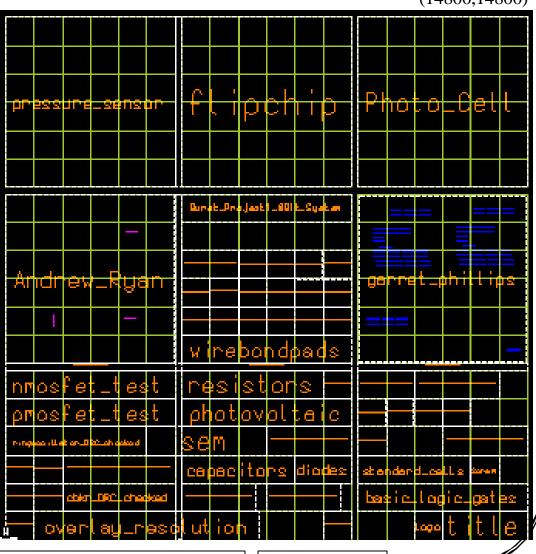

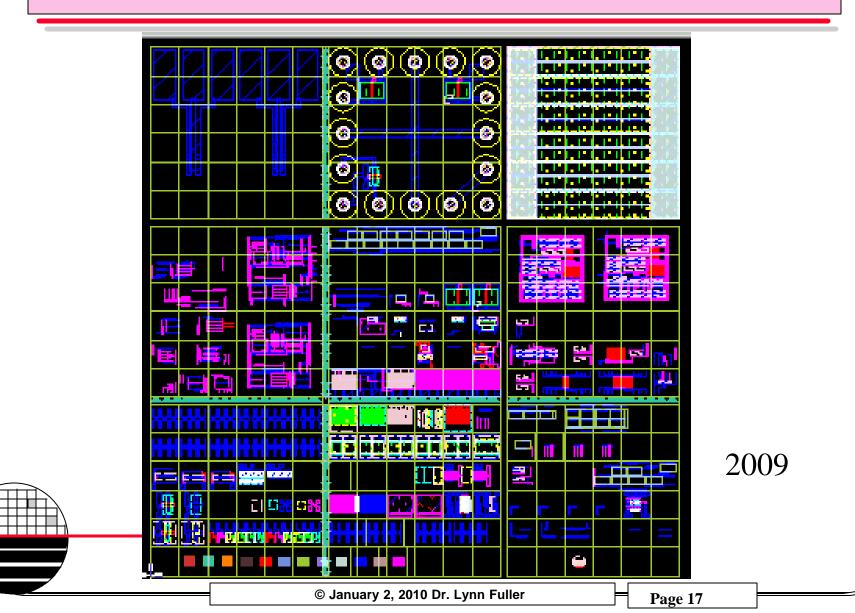

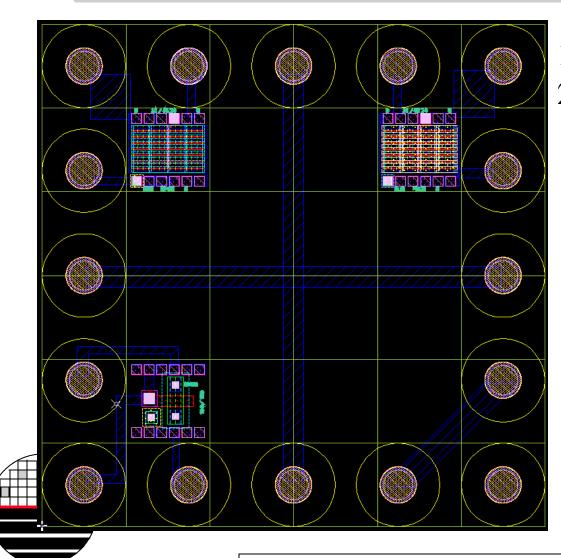

# FLOORPLAN AND HIERARCHY

#### **OVERALL CHIP LAYOUT**

(14800, 14800)

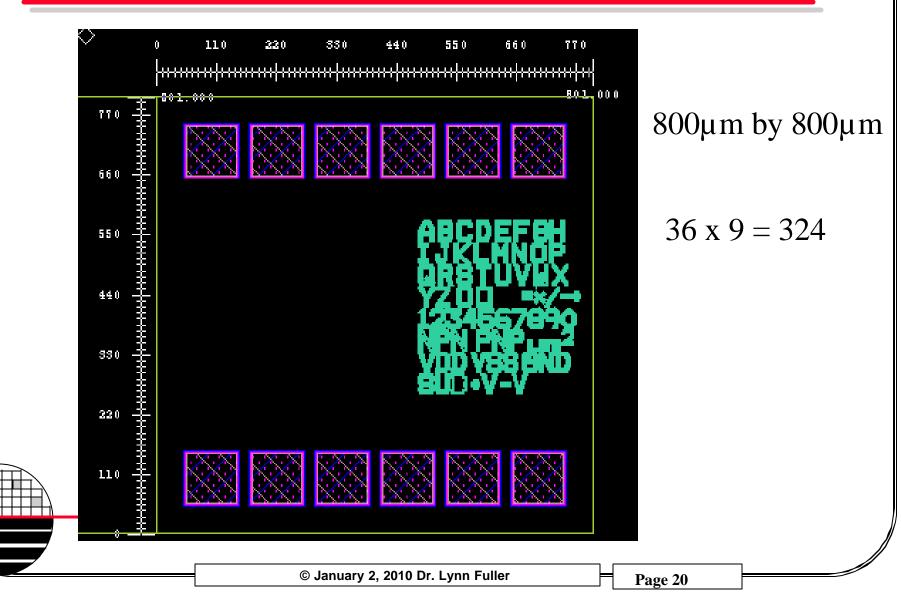

The test chip is divided into nine cells each 5 mm by 5 mm. The cells are divided into 36 individual tiny cells each 800 µm by 800 µm in size plus 200 µm sawing streets. Most structures fit into the tiny cells including a 12 probe pad layout for probe card testing. The overall chip size is 14800 µm by 14800µm plus 200 µm sawing street to give x and y step size of 15 mm by 15 mm.

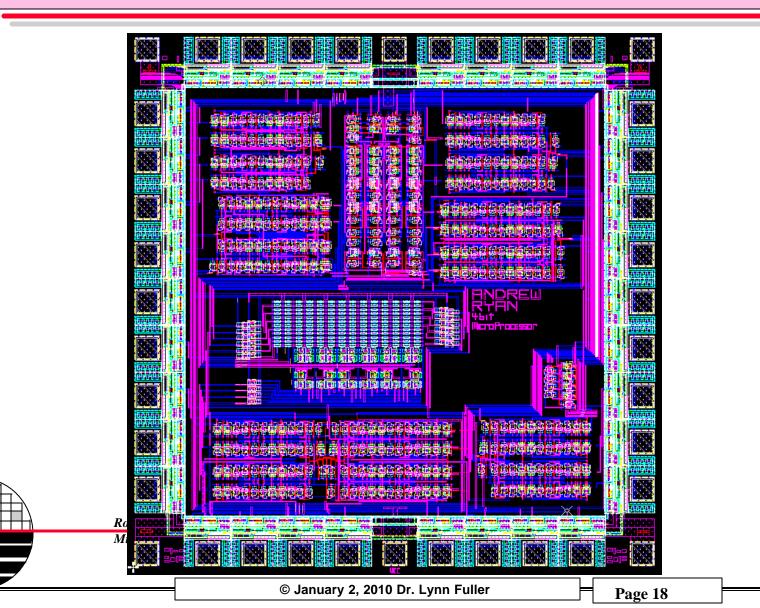

#### JOHN GALT CMOS TESTCHIP

#### **4-BIT MICROPROCESSOR**

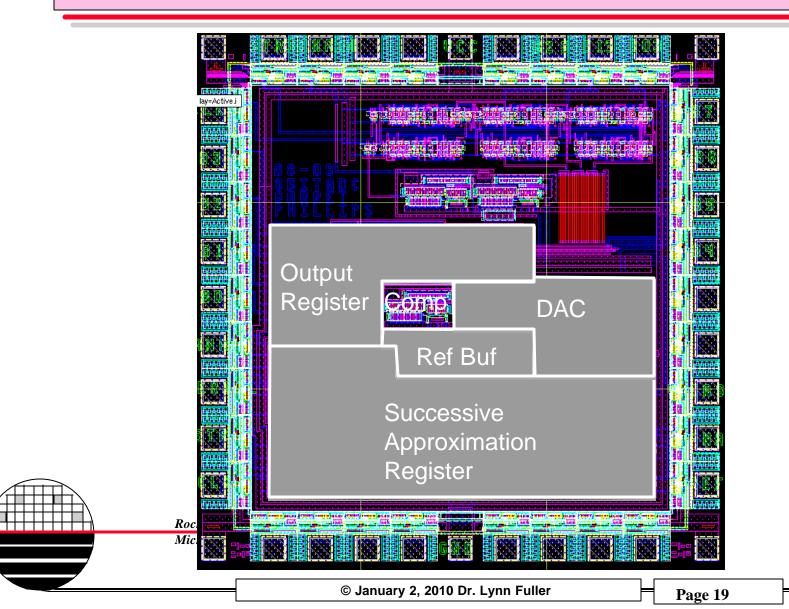

### ANALOG TO DIGITAL CONVERTER

#### TINY CELL

**STRUCTURES FOR FAB PROCESS & EVALUATION**

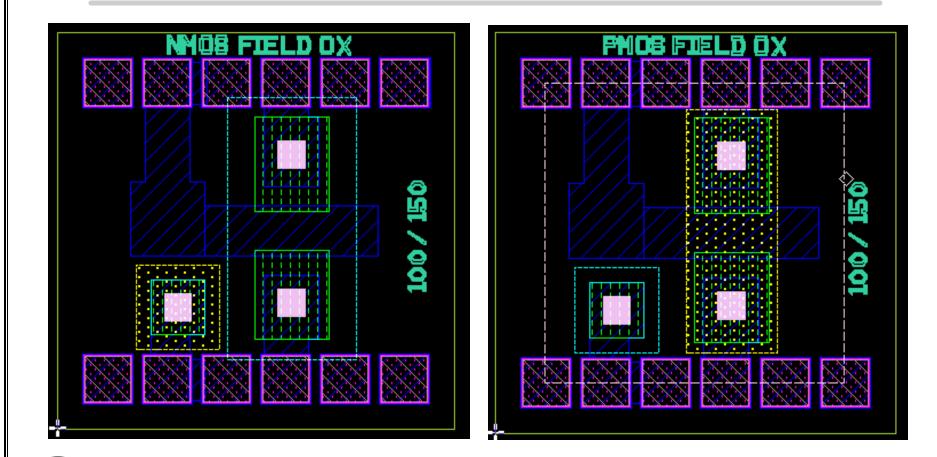

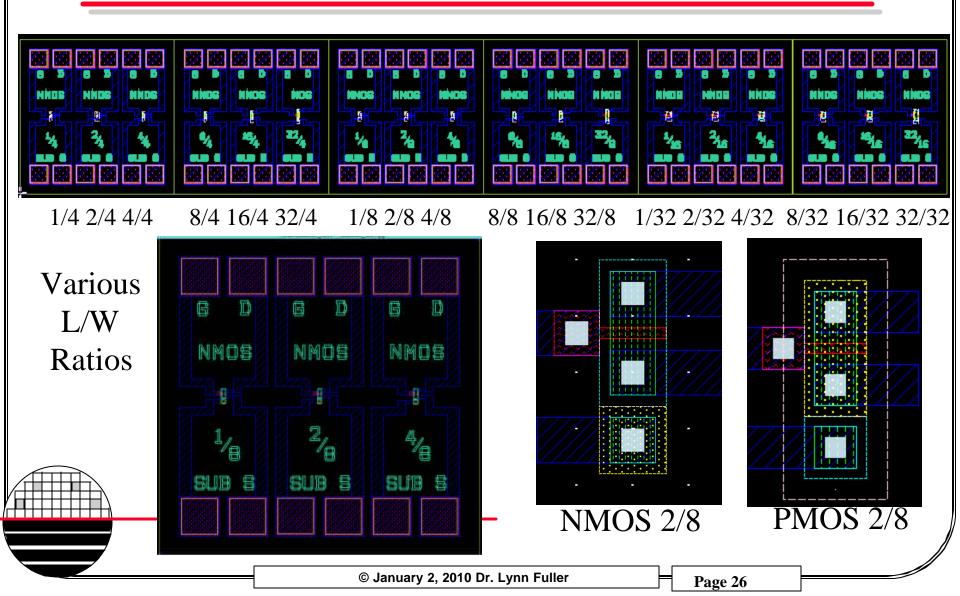

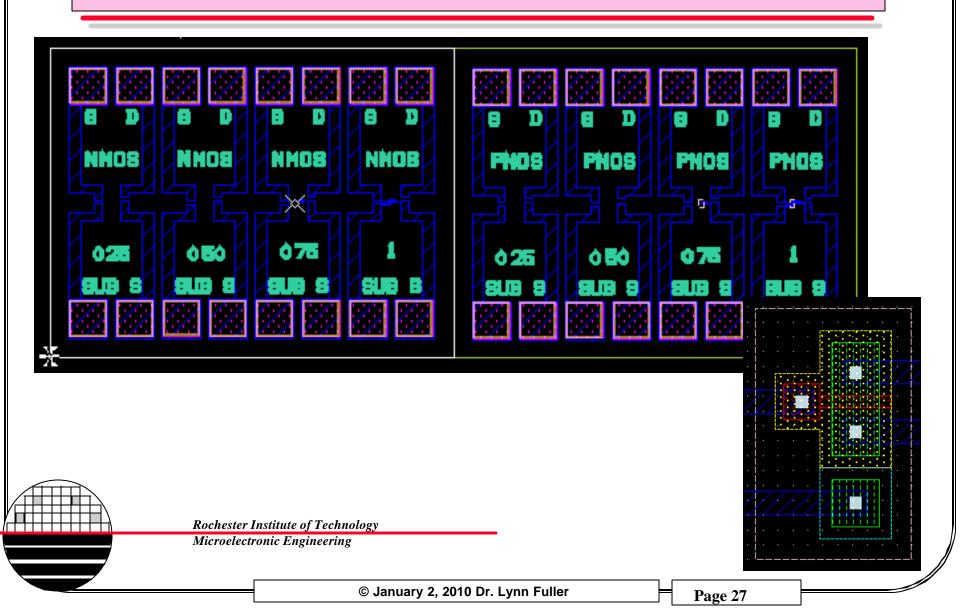

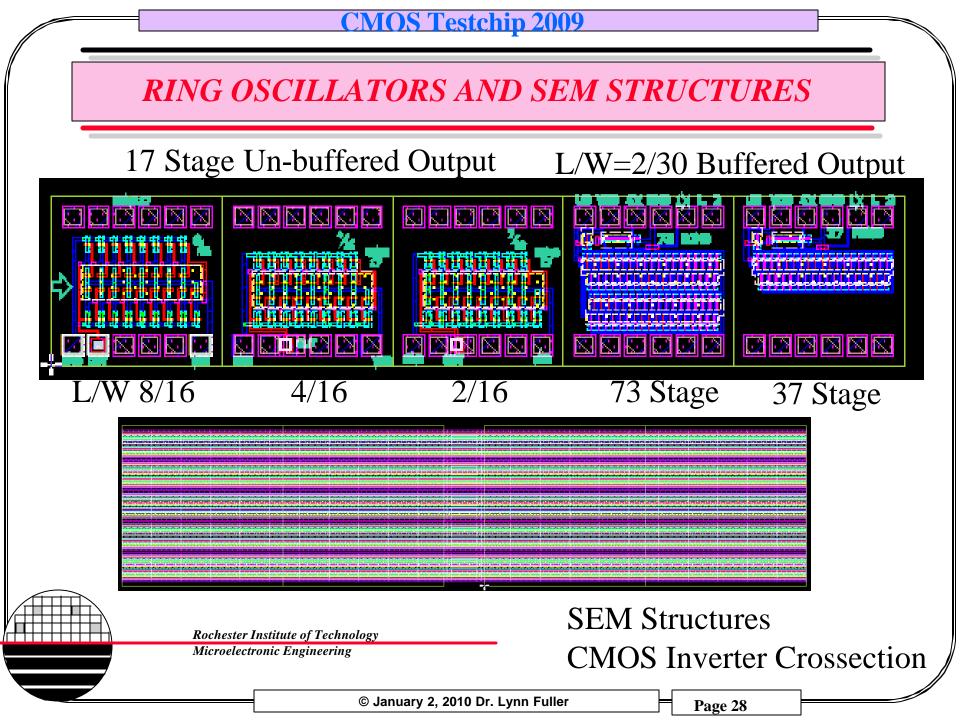

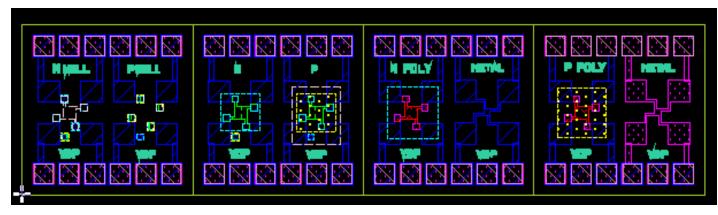

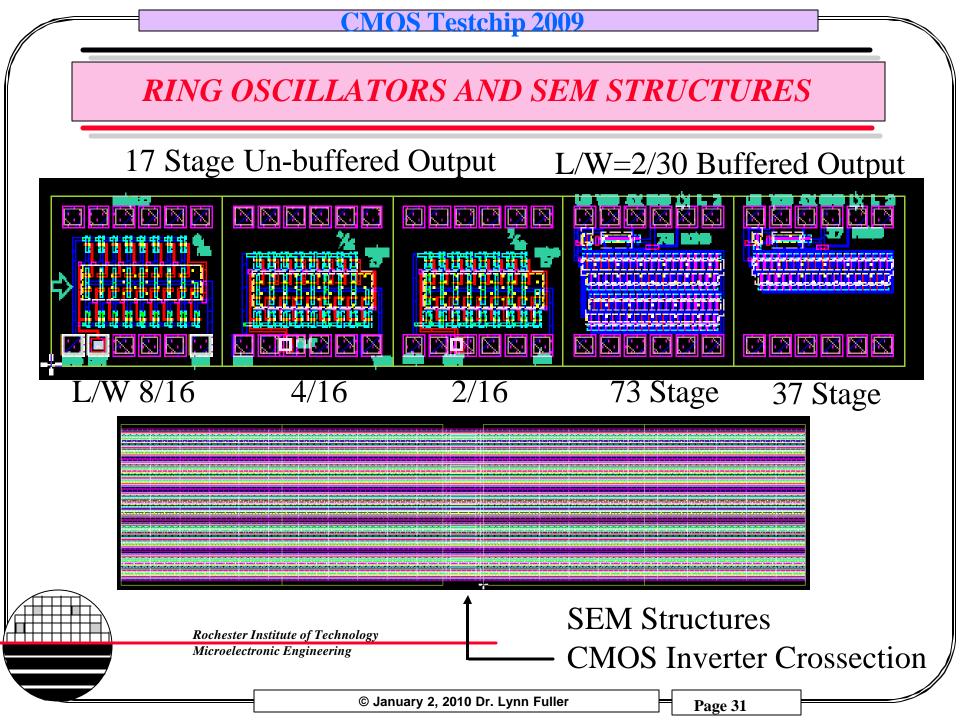

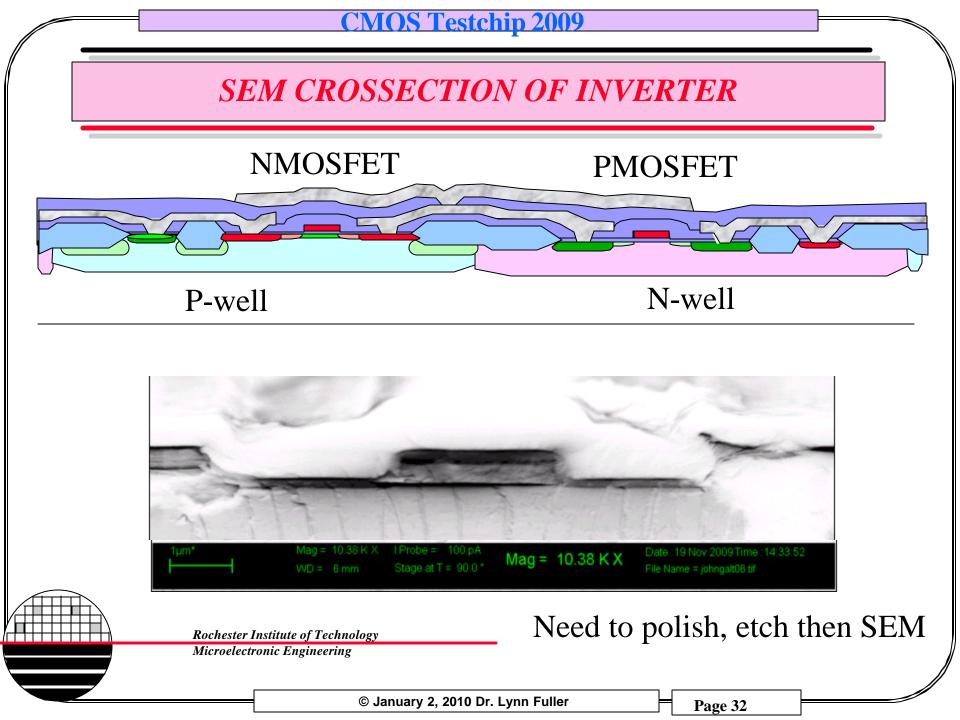

Alignment Structures **Overlay and Resolution Structures** Big areas for measurement (Big Transistors) **SEM Structures CC** Chains Serpentines and Fingers for M1-M2 open and shorts Van Der Pauw's CBKR's NMOS and PMOS Transistors of Various Sizes **Fully Scaled Sub-Micron Transistors** Field Oxide Transistors **Ring Oscillators** Package Test Structures

**Rochester Institute of Technology**

Microelectronic Engineering

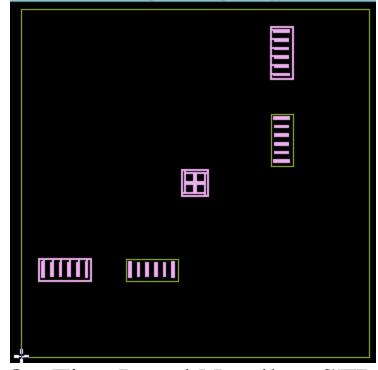

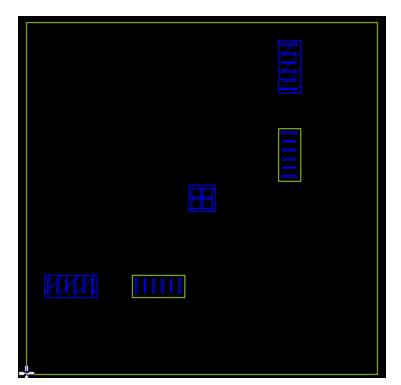

### **ALIGNMENT KEYS**

### On First Level Nwell or STI

### On Metal 1

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

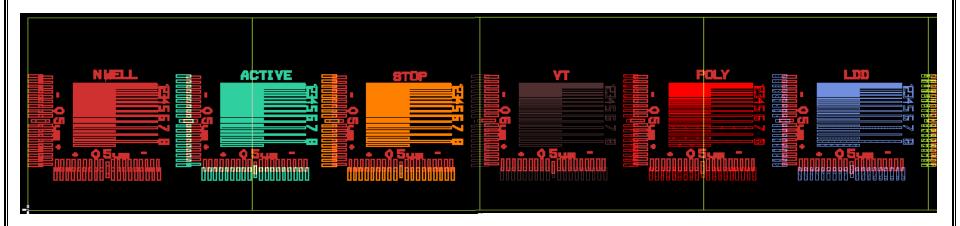

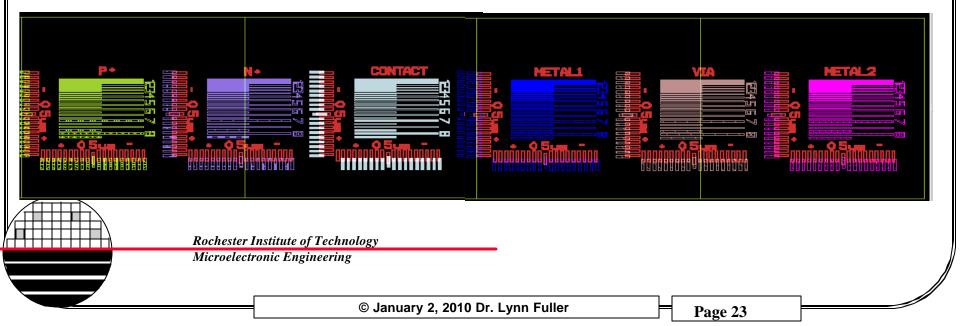

# **RESOLUTION AND OVERLAY**

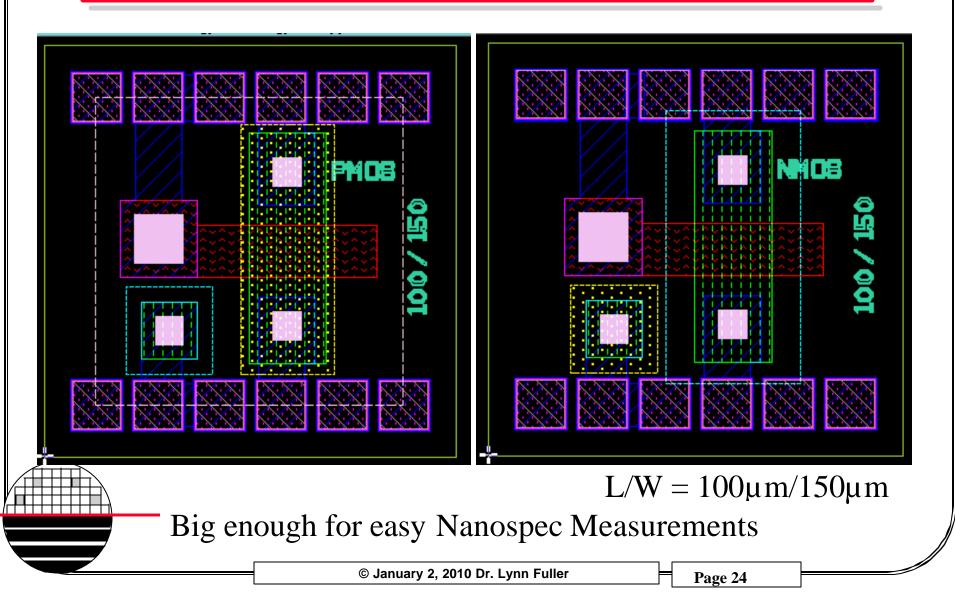

**BIG NMOS AND PMOS FETS**

FIELD OXIDE NMOS AND PMOS FET'S

Rochester Institute of Technology

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

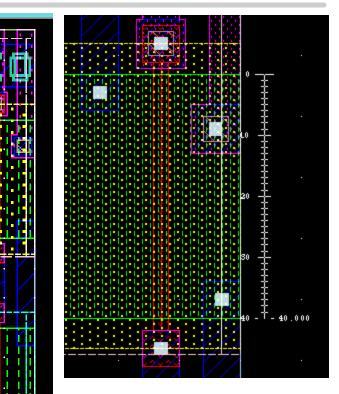

#### **NMOS AND PMOS TRANSISTORS**

#### FULLY SCALED SUB MICRON TRANSISTORS

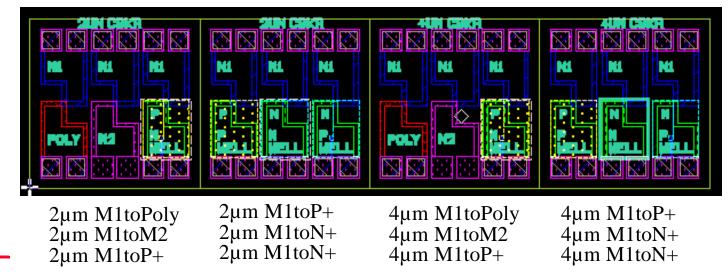

### VAN DER PAUWS AND CBKR's

#### NWELL PWELL N+ P+ N-POLY M1 P-POLY M2

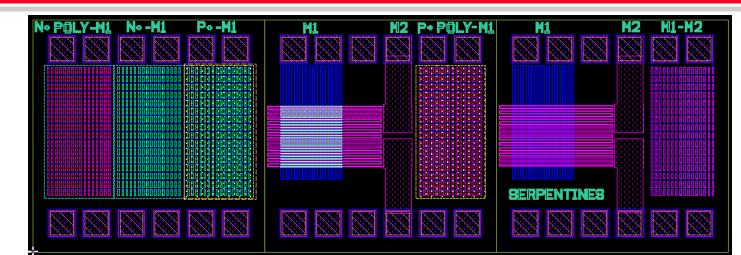

#### SERPENTINES, COMBS, AND VIA CHAINS

# To evaluate metal1, metal2, CC and Via layer quality.

© January 2, 2010 Dr. Lynn Fuller

# **SENSORS**

Interdigitated and Plate Capacitors Diodes and Heaters Resistors Photovoltaic Cells, 1x, 2x, 4x Two side by side pn diode sensors for differential readout

**Rochester Institute of Technology**

Microelectronic Engineering

### **DIODES AND HEATERS**

# Poly Heater on top of Diodes

© January 2, 2010 Dr. Lynn Fuller

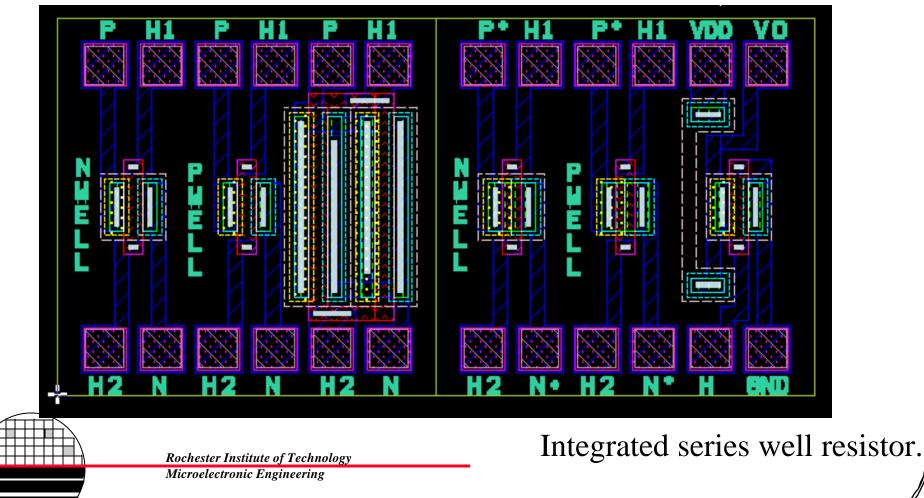

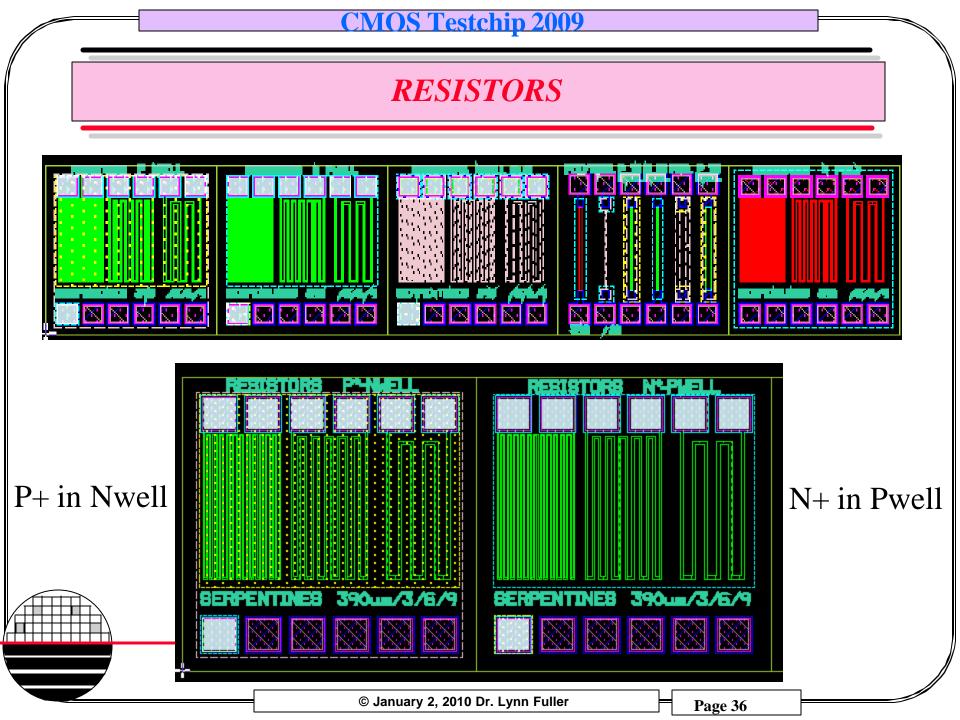

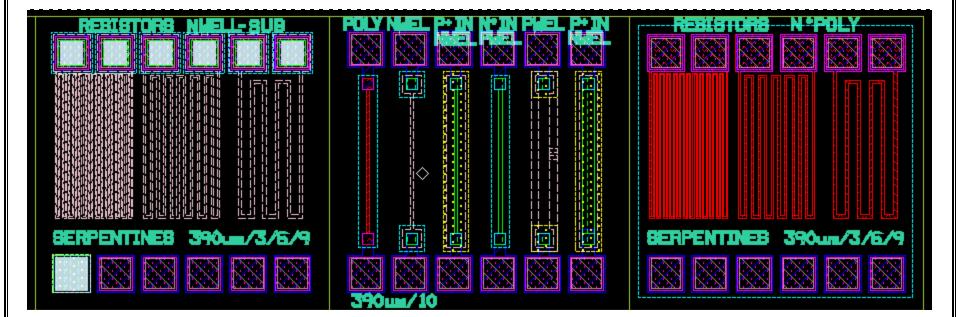

### **RESISTORS**

Nwell in P substrate

#### 6 different Resistor Designs

N+ Poly

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

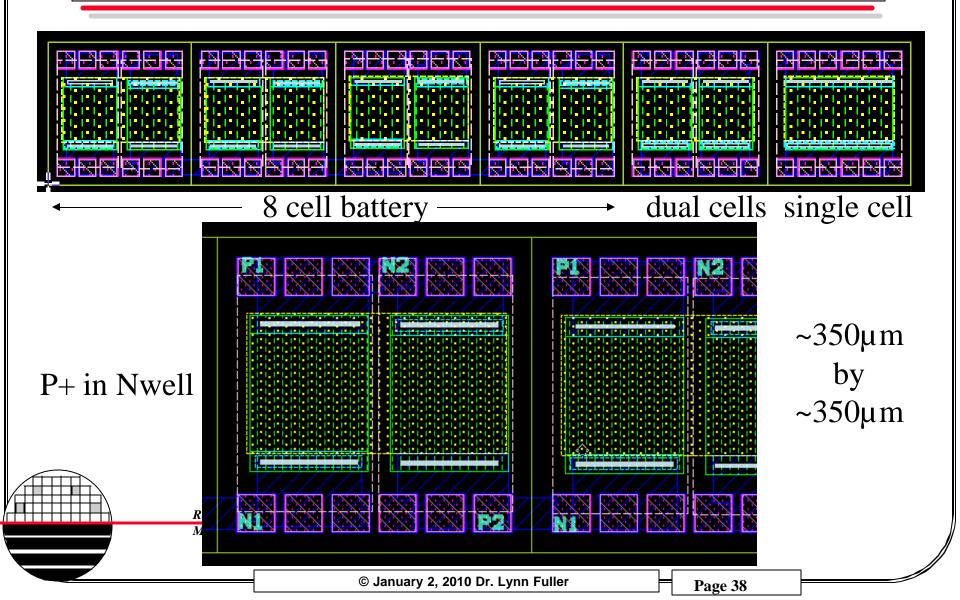

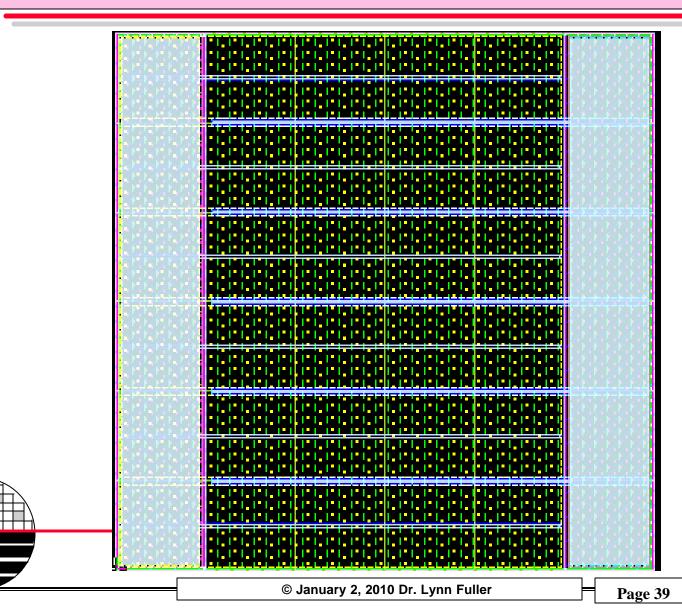

### **PHOTOVOLTAIC DEVICES**

### **BIG PHOTO VOLTAIC CELL**

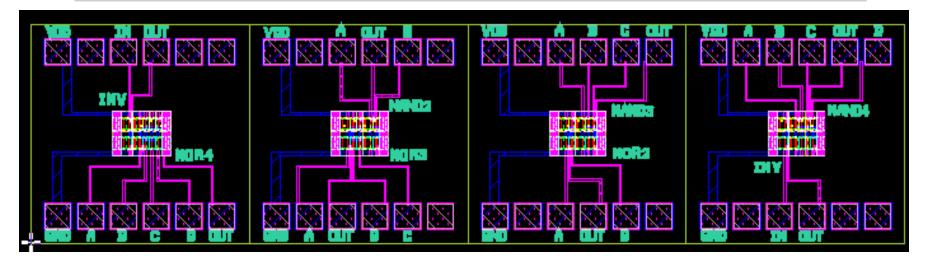

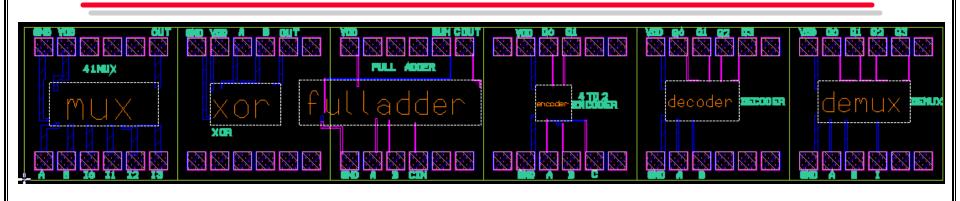

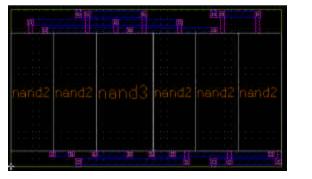

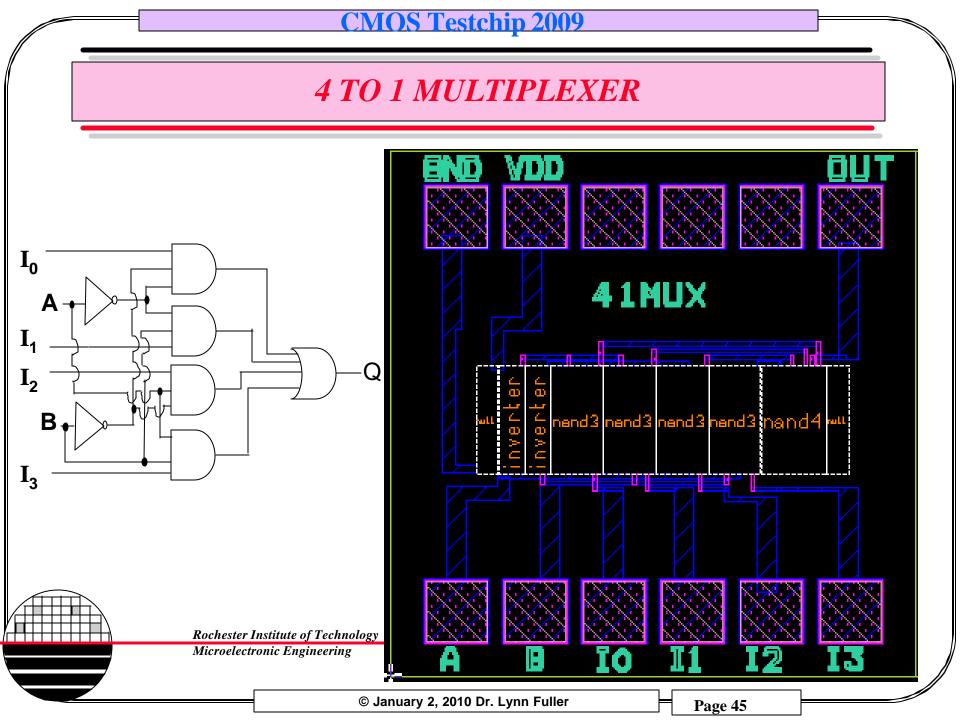

## **DIGITAL CIRCUITS**

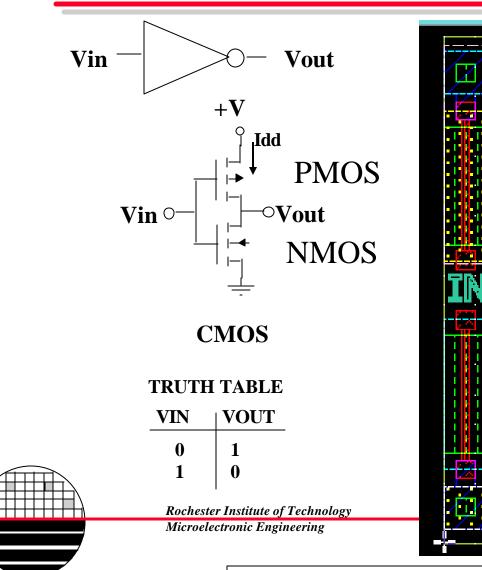

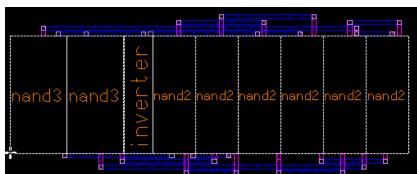

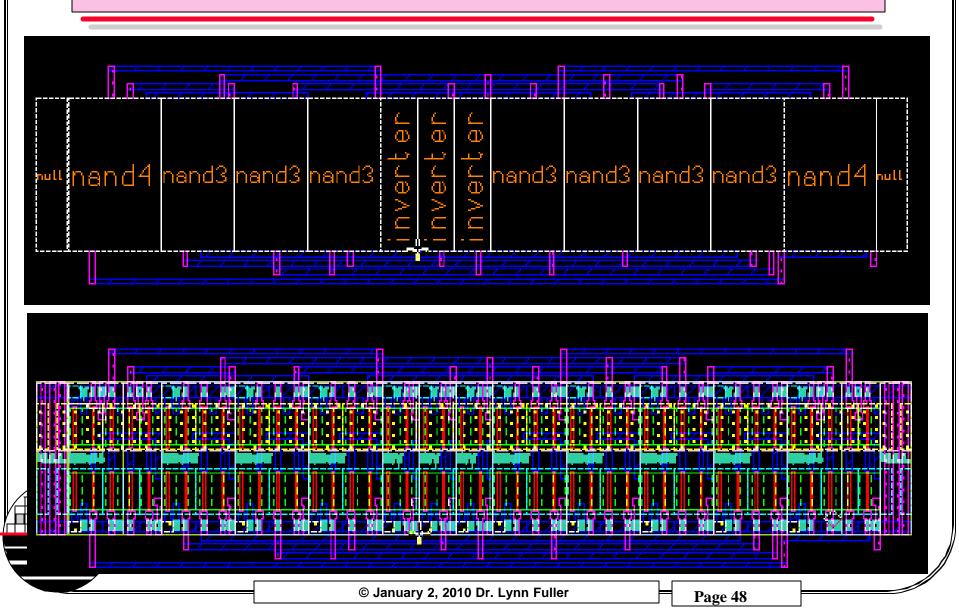

## Primitive Cells INVERTER, NAND2,3,4, NOR2,3,4, NULL

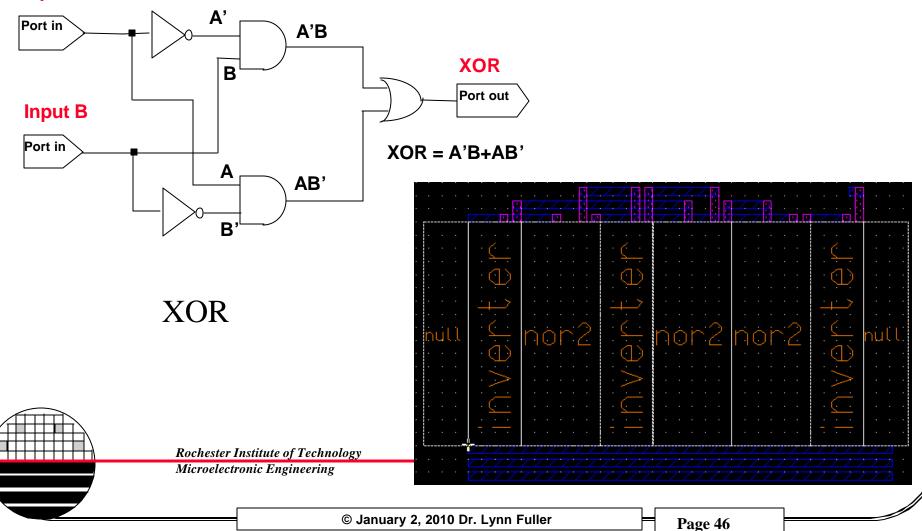

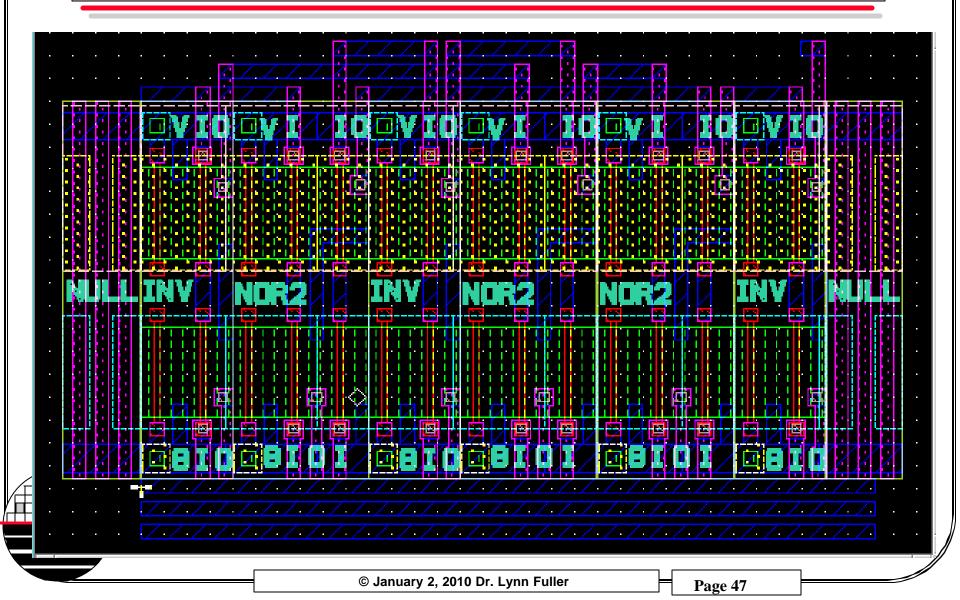

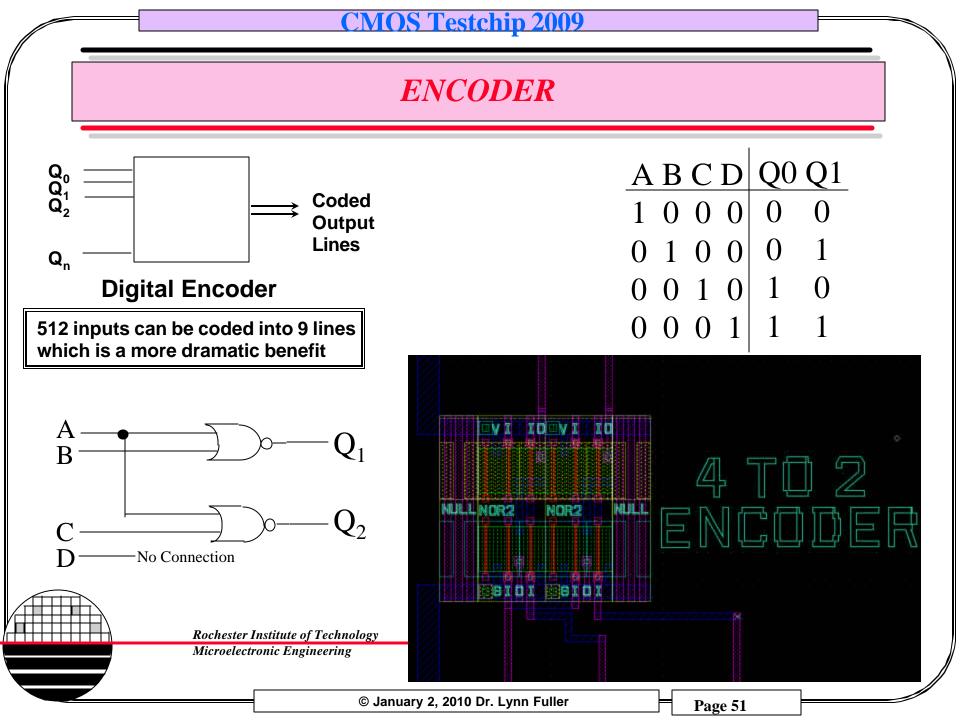

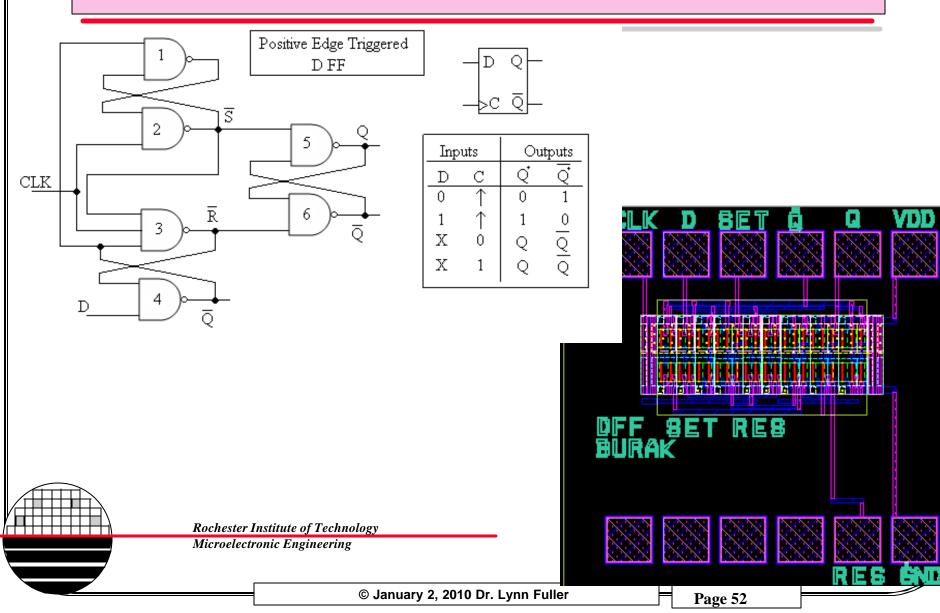

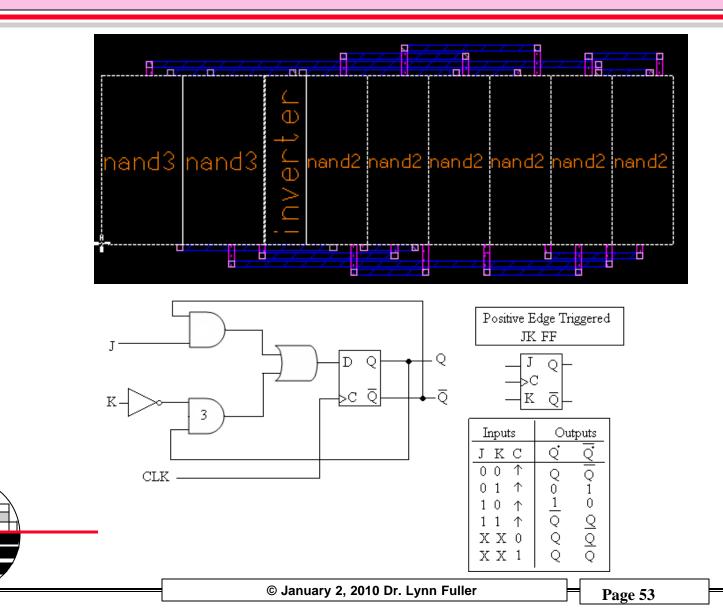

## Basic Cells XOR, MUX, DEMUX, ENCODER, DECODER FULL ADDER, FLIP FLOPS

Macro Cells BINARY COUNTER SRAM

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

**PRIMITIVE CELLS WITH PADS**

# INV/NOR4 NOR3/NAND2 NOR2/NAND3 INV/NAND4

Rochester Institute of Technology

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

### **CMOS INVERTER**

$W = 40 \ \mu m$ Ldrawn = 2.5 $\mu m$ Lpoly = 1.0 $\mu m$ Leff = 0.35  $\mu m$

© January 2, 2010 Dr. Lynn Fuller

**PRIMITIVE CELLS** Š i ar وانبي 5 F Ø 4----X [\* | |\* | i." i | " | • i-i 5 H., 15<sup>°</sup> 7, 艺 Ż ۴t) <mark>21. 1</mark>2 1/H HH ПY i i i 111 121 •  $\mathbb{P}$ <u>. 7</u>7 - F - 7 F 6 Z 77 11 1 1 10 4 1 Þ I. I . **1837** B **F**all ø Ê

CMOS Testchip 2009

© January 2, 2010 Dr. Lynn Fuller

1

3

Æ

---

stitute

nic En

2

Ę

<u>, ' ,</u>

7

Page 43

K

-

E

7

**BASIC DIGITAL CELLS WITH PADS**

Multiplexer XOR Full

### Demux

JK FF

Edge Triggered D FF

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

## BASIC CELL XOR

#### Input A

XOR

## FULL ADDER

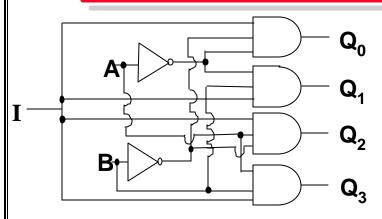

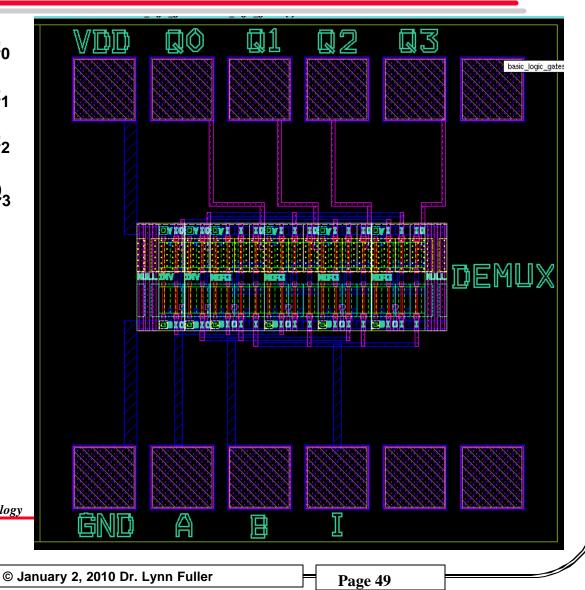

### **1 TO 4 DEMULTIPLEXER**

Rochester Institute of Technology Microelectronic Engineering

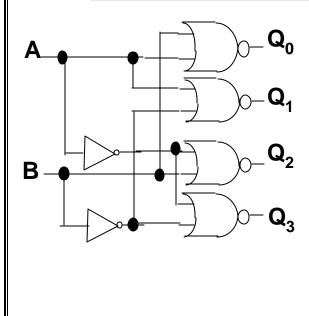

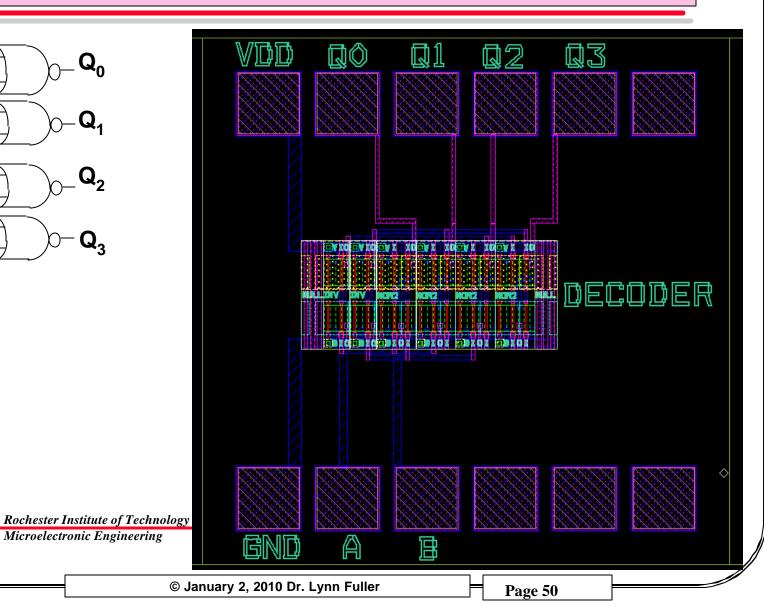

### **DECODER**

### EDGE TRIGGERED D TYPE FLIP FLOP

### JK FLIP FLOP

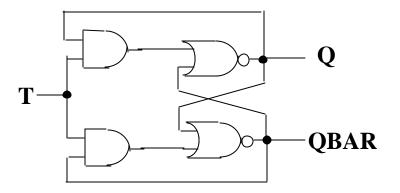

## **T-TYPE FILP-FLOP**

#### **TOGGEL FLIP FLOP**

**Q:** Toggles High and Low with Each Input

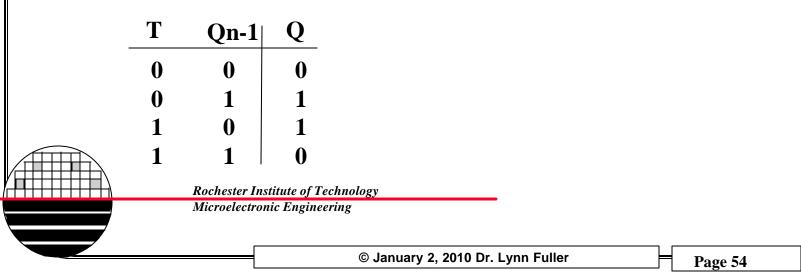

### **BINARY COUNTER USING T TYPE FLIP FLOPS**

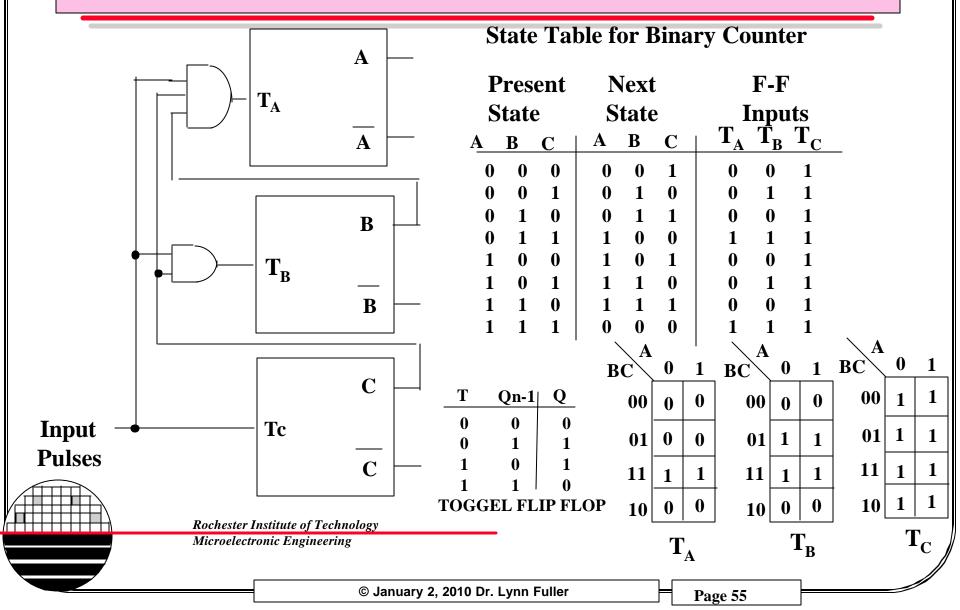

**3-BIT BINARY COUNTER WITH D FLIP FLOPS**

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

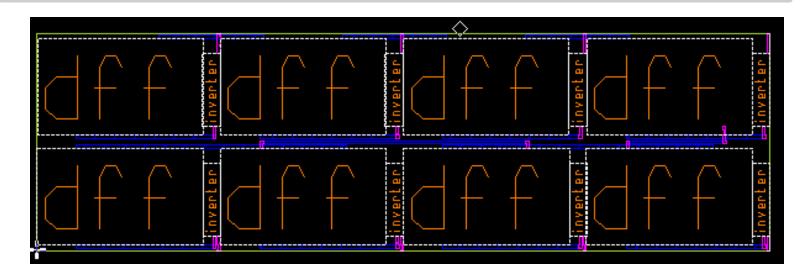

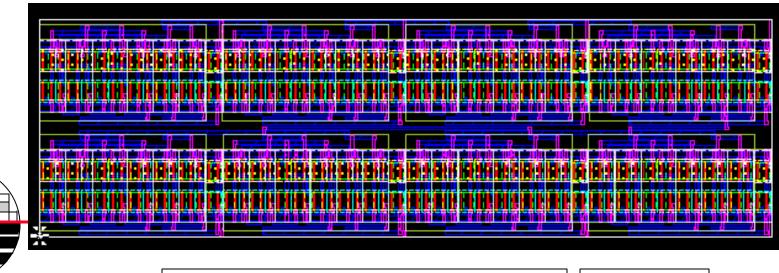

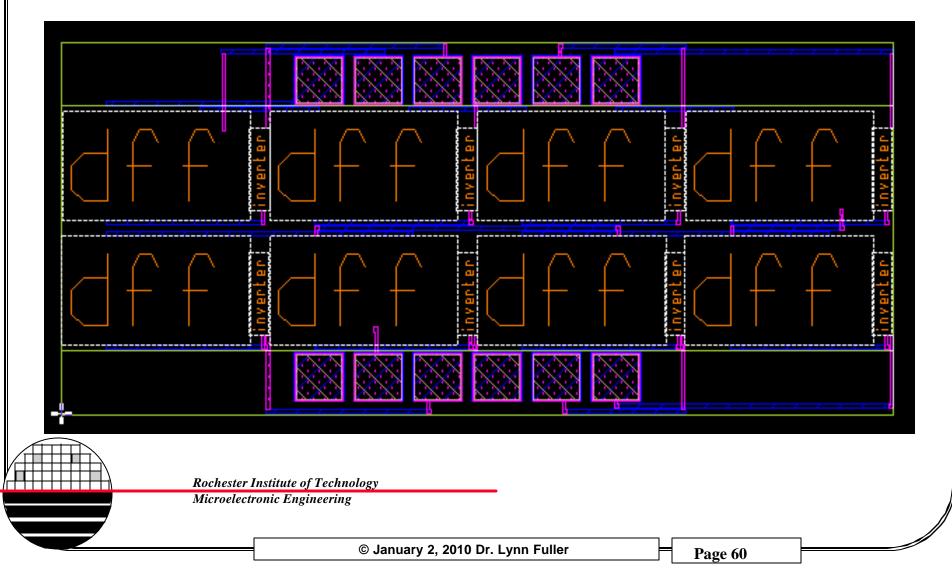

## **MACROCELLS**

# Binary Counter SRAM

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

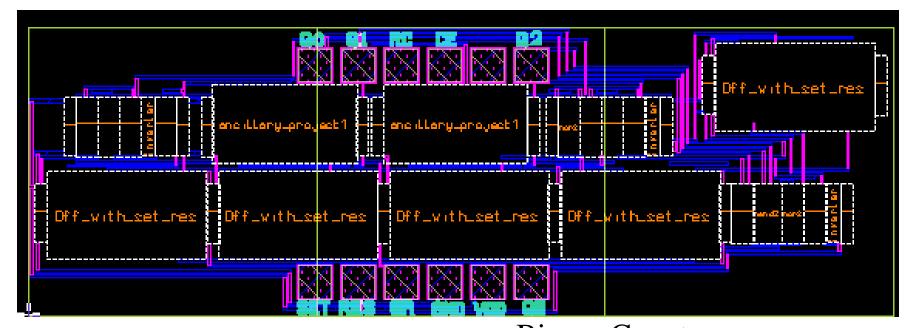

### **3-BIT BINARY COUNTER/SHIFT REGISTER**

Binary Counter Serial Output Asynchronous Reset Count Up Enable Shift Out Clock Input Count Up Clock Input Start Bit and Stop Bit

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

## **8-BIT BINARY COUNTER**

© January 2, 2010 Dr. Lynn Fuller

## **8-BIT BINARY COUNTER WITH PADS**

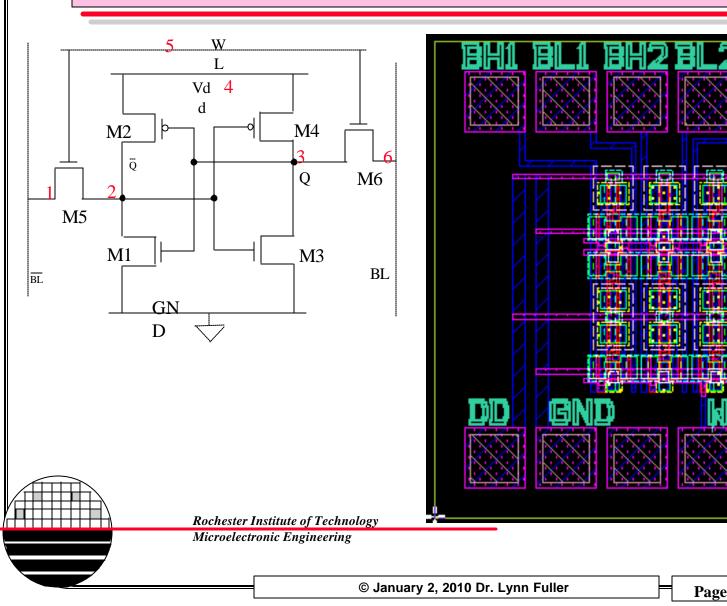

### **SRAM**

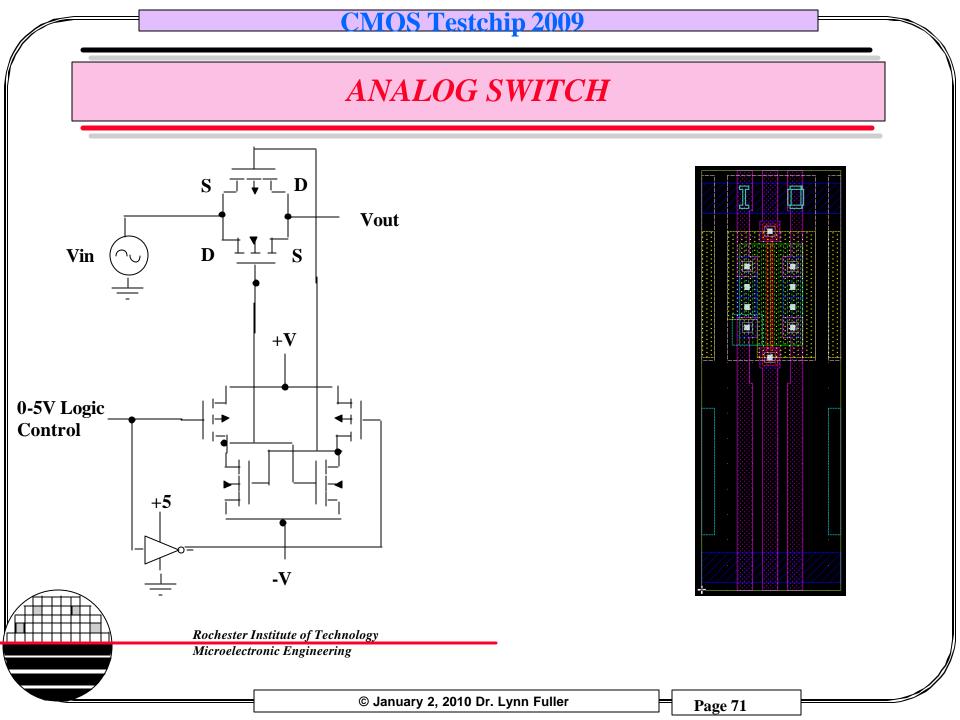

### ANALOG AND MIXED MODE CIRCUITS

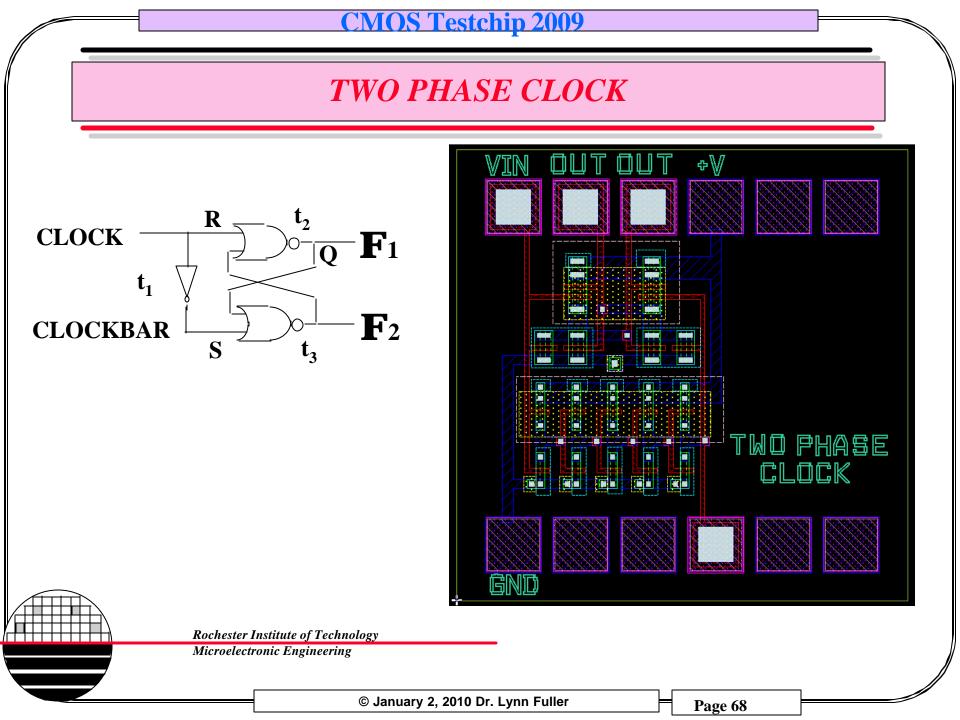

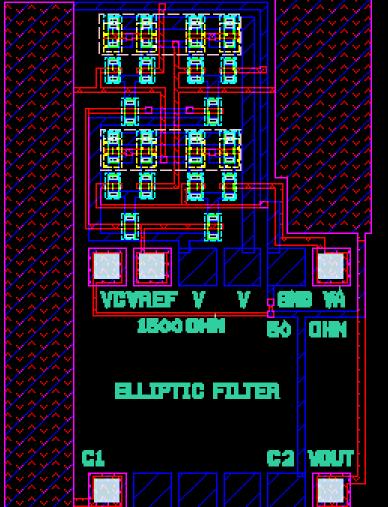

**Operational Amplifier** Inverter with Hysteresis **RC** Oscillator Two Phase Clock **Analog Switches** Voltage Doubler, Tripler Analog Multiplexer Comparator with Hysteresis A-to-D D-to-A OTA, Biquad Filter, Elliptic Filter Programmable Binary Weighted Resistors

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

\*1-17-2007 FROM DR. FULLER'S SPREADSHEET WITH VT0=-0.75 .MODEL RITSUBP49 PMOS (LEVEL=49 VERSION=3.1 CAPMOD=2 MOBMOD=1 +TOX=1.5E-8 XJ=2.26E-7 NCH=7.12E16 NSUB=3.16E16 XT=8.66E-8 NSS=3E11 PCLM=5 +XWREF= 2.0E-7 XLREF=3.61E-7 VTH0=-0.75 U0= 376.72 WINT=2.0E-7 LINT=2.26E-7 +RSH=1347 JS=3.51E-8 JSW=3.51E-8 CJ=5.28E-4 MJ=0.5 PB=0.94 +CJSW=1.19E-10 MJSW=0.5 PBSW=0.94 NGATE=5E20 +CGS0=4.5E-10 CGD0=4.5E-10 CGB0=5.75E-10)

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

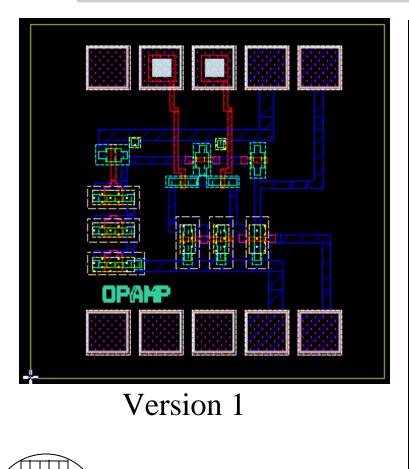

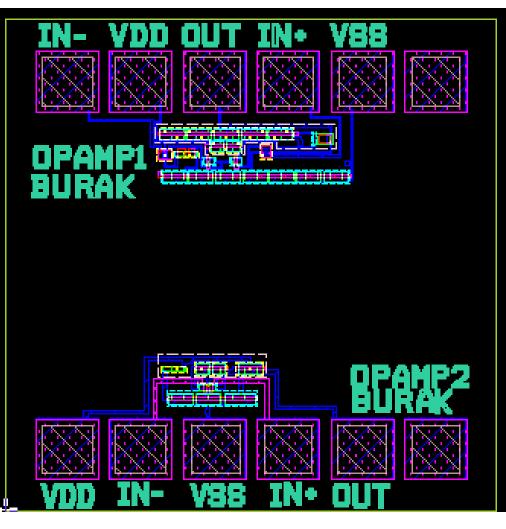

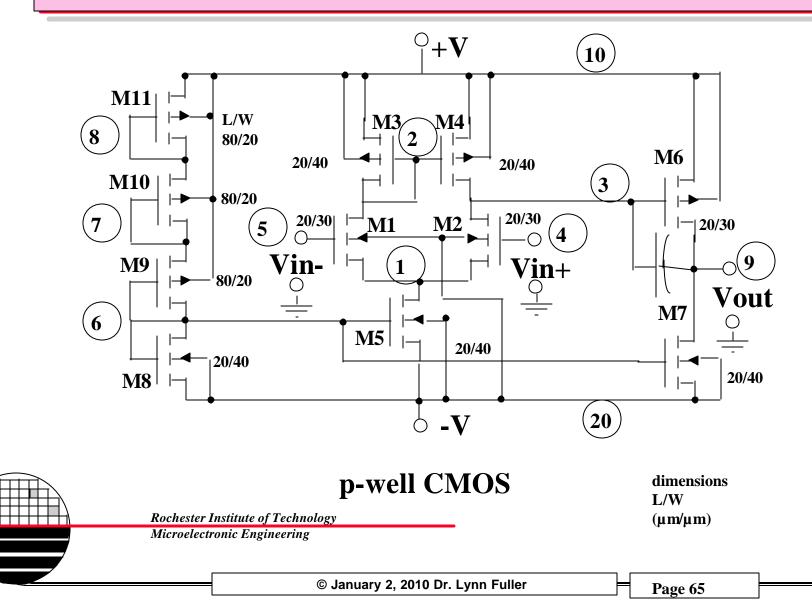

**OPERATIONAL AMPLIFIER**

Rochester Institute of Technology Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

**VERSION 1 OPERATIONAL AMPLIFIER**

#### <u>CMOS Testchip 2009</u>

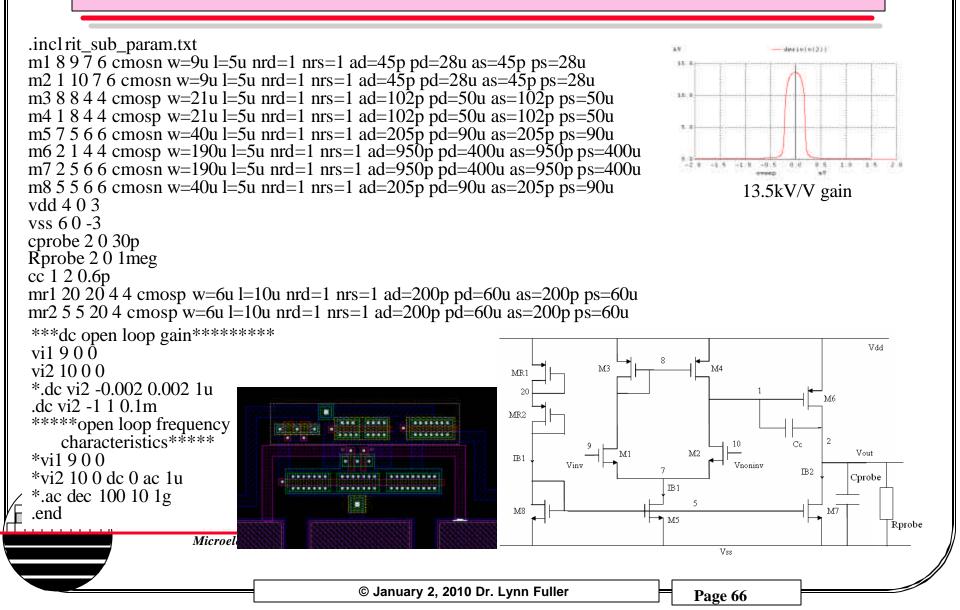

#### **SPICE ANALYSIS OF OP AMP VERSION 2**

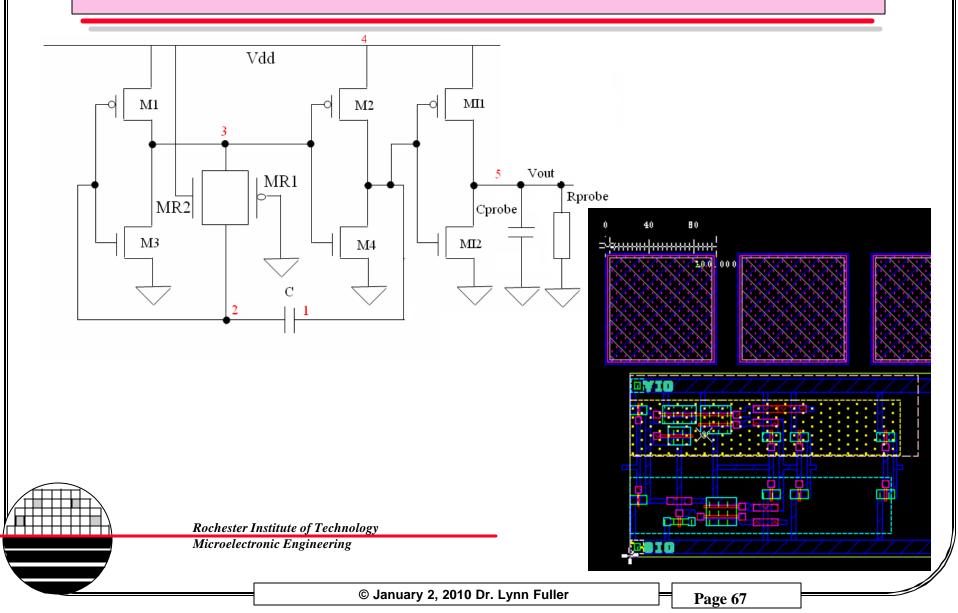

### **INVERTER WITH HYSTERESIS – RC OSCILLATOR**

**WINSPICE SIMULATION FOR VERSION TWO + BUFFERS**

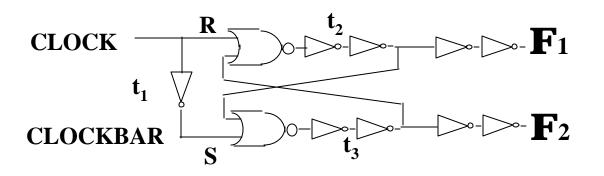

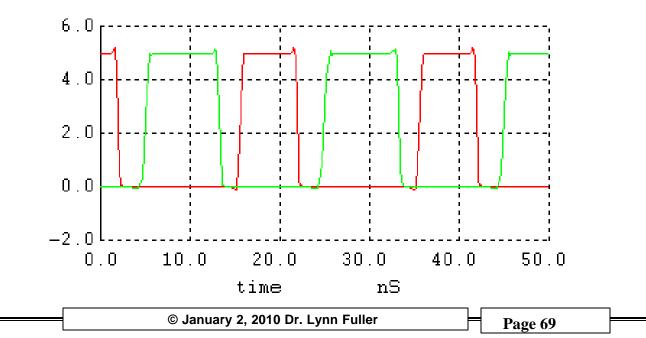

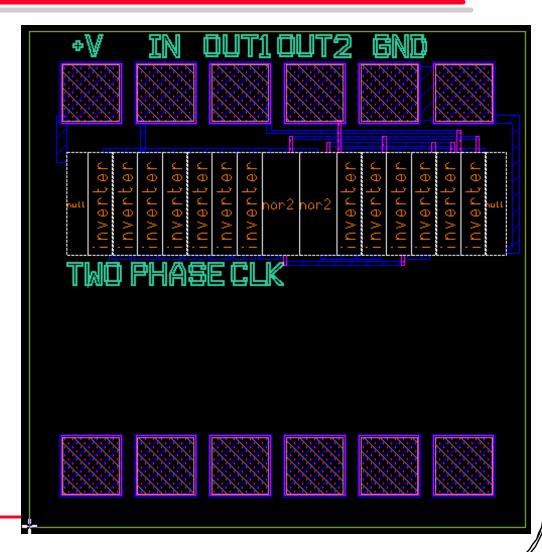

### **TWO PHASE CLOCK WITH BUFFERS**

Rochester Institute of Technology Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

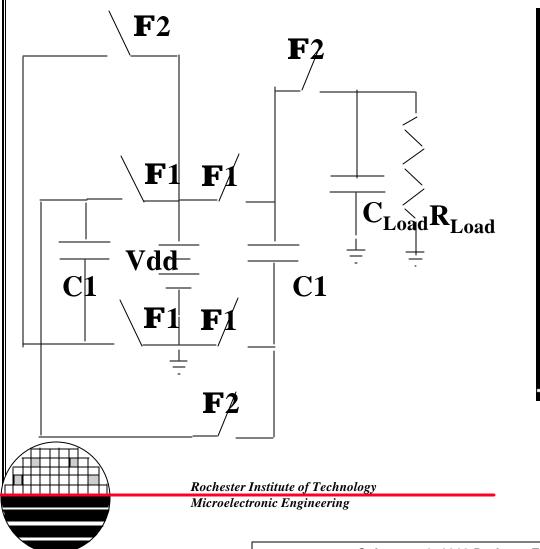

### **VOLTAGE DOUBLER**

## Voltage Tripler

© January 2, 2010 Dr. Lynn Fuller

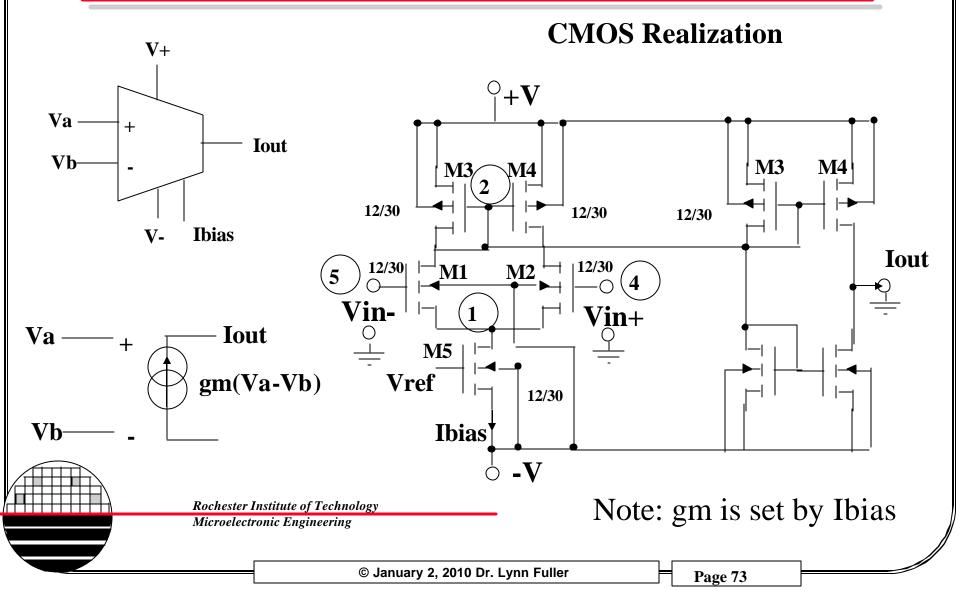

**OPERATIONAL TRANSCONDUCTANCE AMPLIFIER**

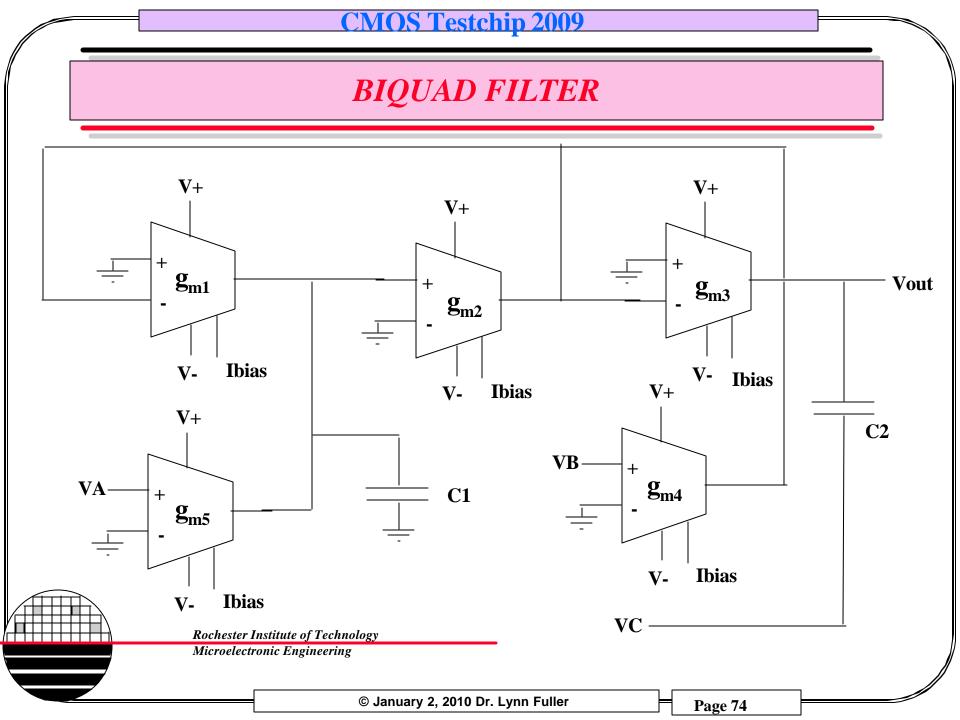

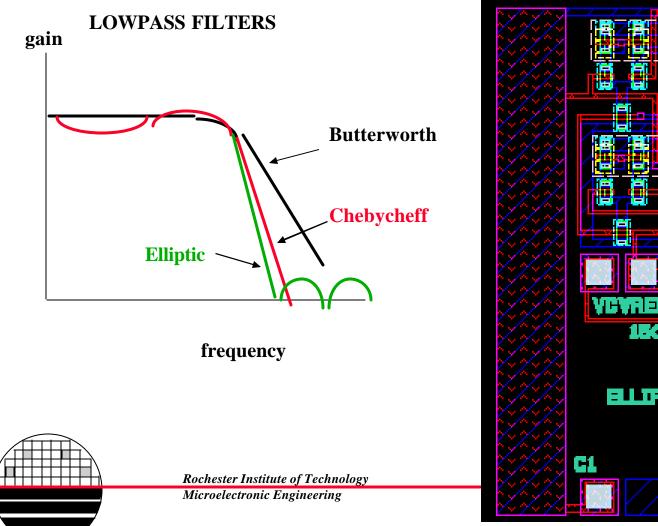

# **BIQUAD FILTER**

$$\mathbf{V}_{\text{out}} = (\mathbf{s}^2 \mathbf{C}_1 \mathbf{C}_2 \mathbf{V}_c + \mathbf{s} \ \mathbf{C}_1 \ \mathbf{g}_{\text{m4}} \ \mathbf{V}_b + \mathbf{g}_{\text{m2}} \ \mathbf{g}_{\text{m5}} \mathbf{V}_a) / (\mathbf{s}^2 \mathbf{C}_1 \mathbf{C}_2 + \mathbf{s} \mathbf{C}_1 \mathbf{g}_{\text{m3}} + \mathbf{g}_{\text{m2}} \mathbf{g}_{\text{m1}})$$

This filter can be used as a low-pass, high-pass, bandpass, bandrejection and all pass filter. Depending on the C and gm values a Butterworth, Chebyshev, Elliptic or any other configuration can be achieved

For example: let Vc=Vb=0 and Va=Vin, also let all  $g_m$  be equal, then

Vout = Vin /

$$(s^2C_1C_2/g_mg_m + sC_1/g_m + 1)$$

which is a second order low pass filter with corner frequency at

$$\omega_{\rm c} = {\rm g_m}/{\rm \sqrt{C_1C_2}} \quad {\rm and} \ {\rm Q} = {\rm \sqrt{C_2/C_1}}$$

Rochester Institute of Technology

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

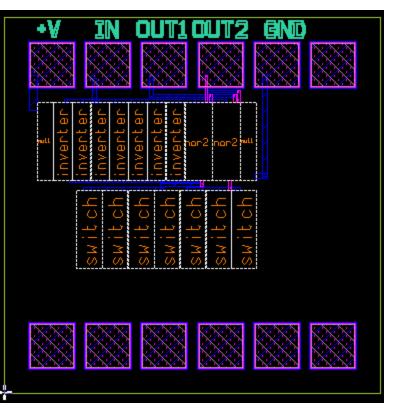

**OTA, BIQUAD ELLIPTIC FILTER**

© January 2, 2010 Dr. Lynn Fuller

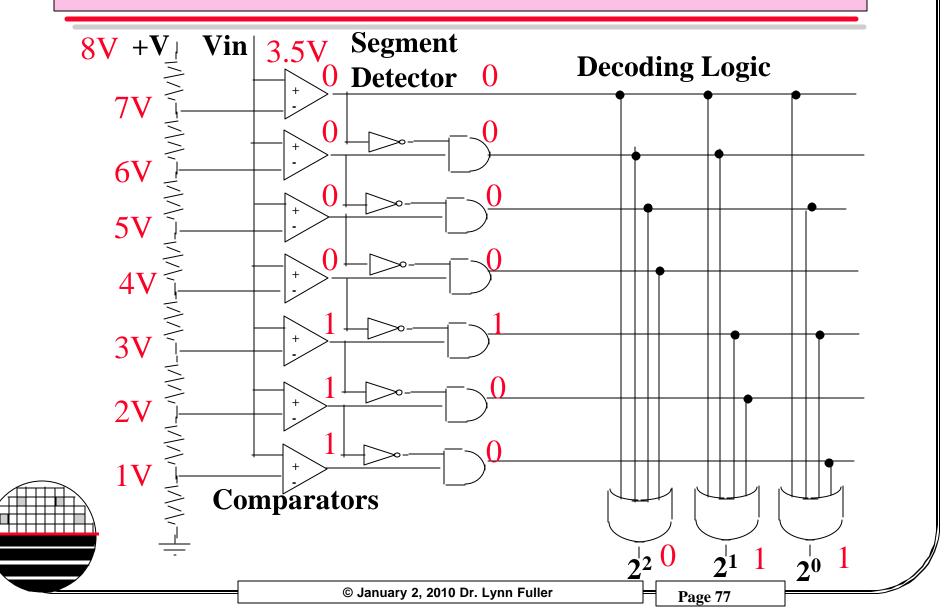

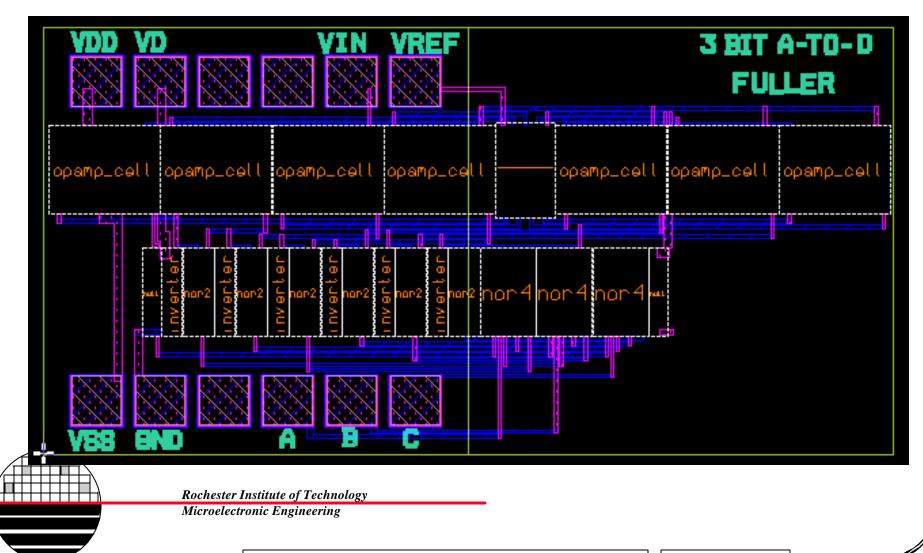

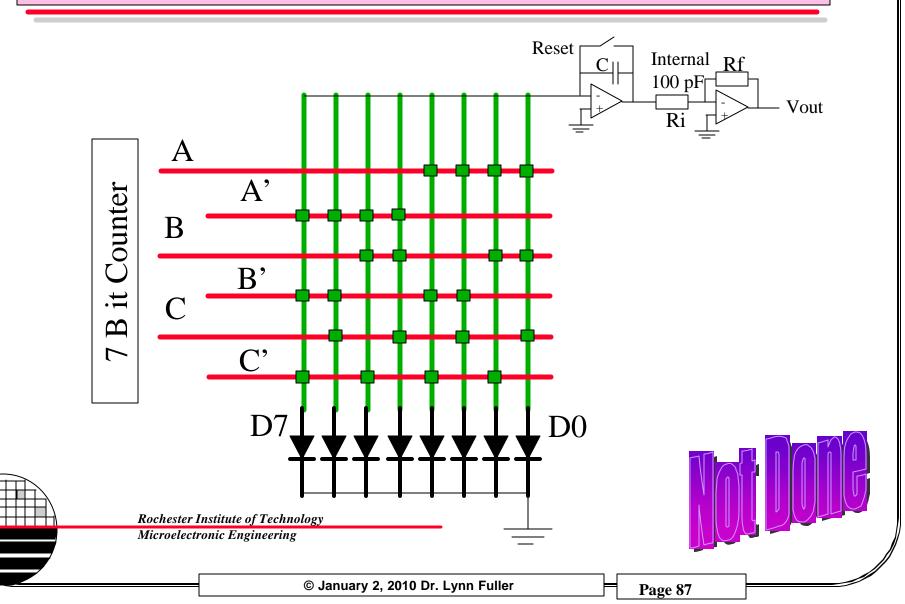

## **3 BIT ANALOG TO DIGITAL CONVERTER**

## **3 BIT ANALOG TO DIGITAL CONVERTER**

© January 2, 2010 Dr. Lynn Fuller

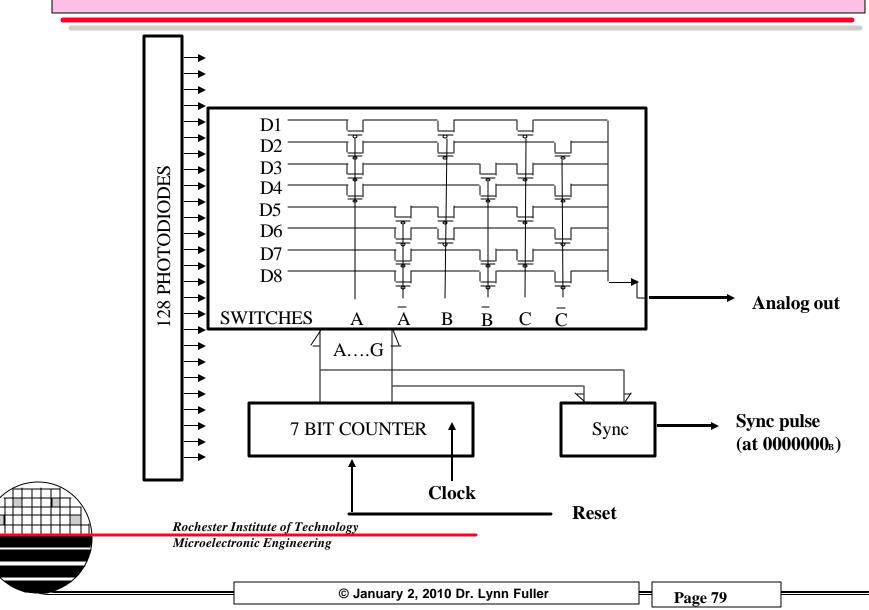

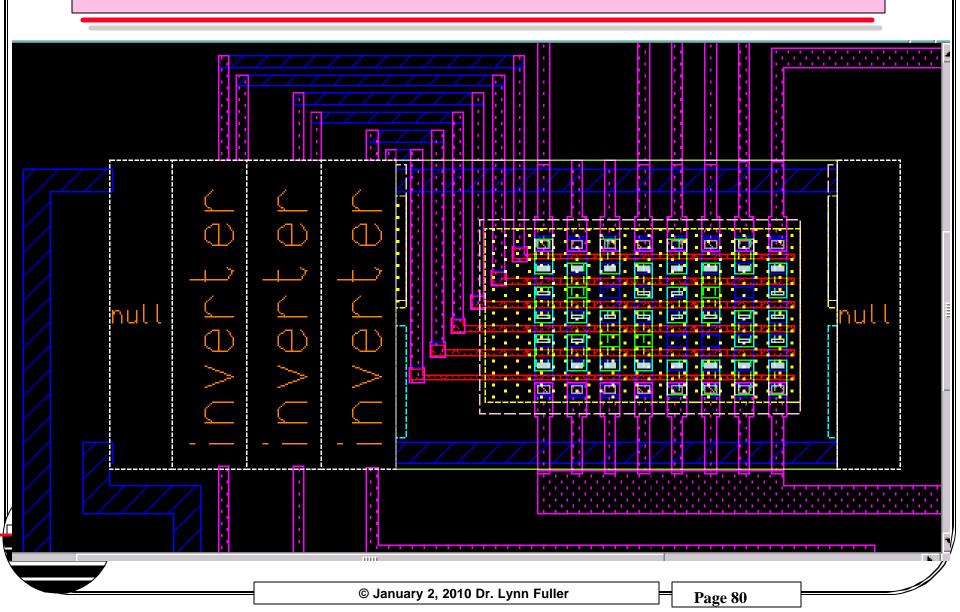

## ANALOG MULTIPLEXER

### 8 TO 1 ANALOG MUX

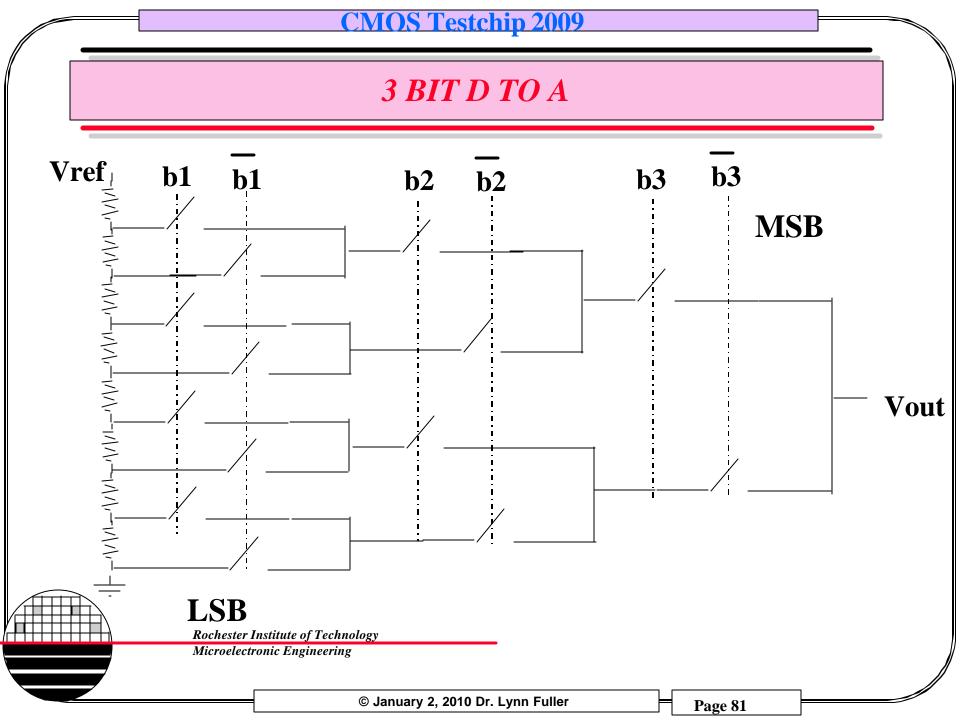

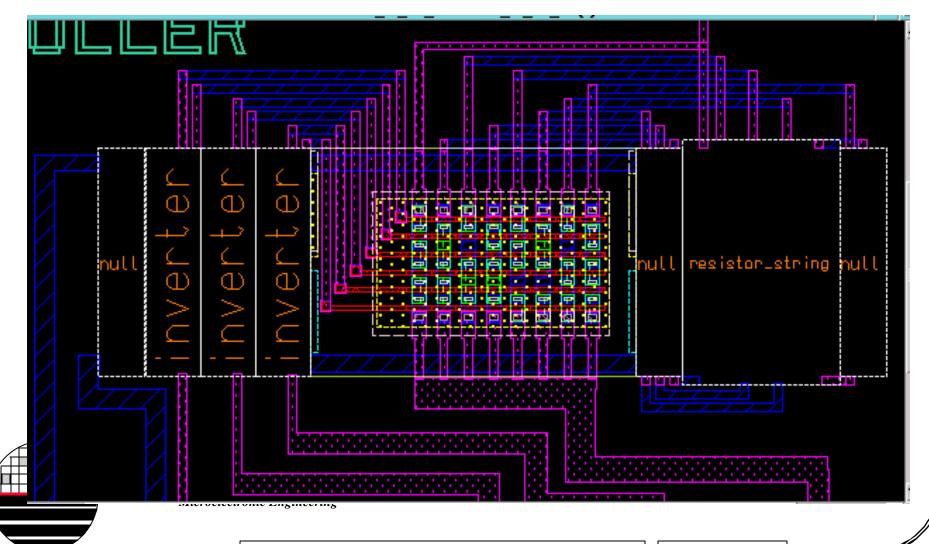

# 3 BIT D TO A

© January 2, 2010 Dr. Lynn Fuller

# **PROJECTS**

Wireless Capacitive Sensor MEMS Pressure Sensor Spectro Photometer Hearing Aid CCD CCD Imager

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

### WIRELESS CAPACITIVE SENSOR PROJECT

# WIRELESS CAPACITIVE SENSOR PROJECT

Rochester Institute of Technology

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller

### **MEMS PRESSURE SENSOR**

© January 2, 2010 Dr. Lynn Fuller

**SPECTRO PHOTOMETER PROJECT**

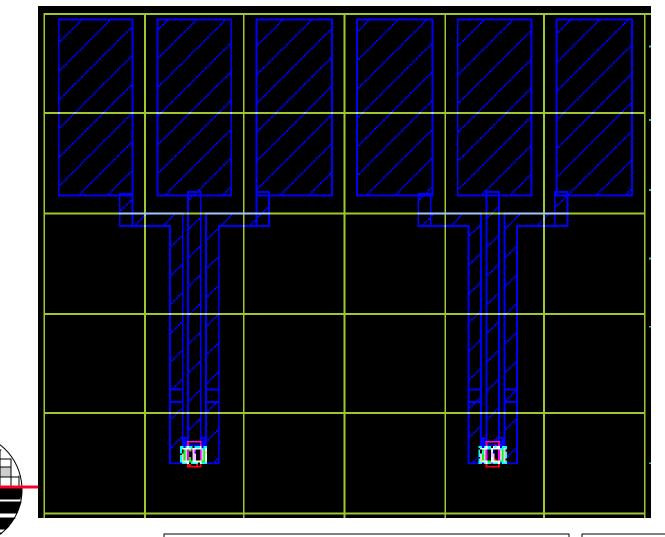

### **SOLDER BUMP TEST CHIP**

1000µm center-to-center 225µm diameter circle

Under bump metal is Cr/Ni and is defined by a lift-off lithography.

The solder is printed using a 150um photoresist and solder paste. (or 500um solder ball is placed over circle)

## **REFERENCES**

- 1. <u>Introduction to VLSI Systems,</u> Carver Mead and Lynn Conway, Addison-Wesley Publishing Company, 1980.

- 2. <u>Analog VLSI Design nMOS and CMOS</u> Malcomb R. Haskard and Ian C. May, Prentice Hall Publishing Company.

- 3. <u>Principles of CMOS VLSI Design A Systems Perspective</u>, Neil Weste, and Kaman Eshraghian, Addison-Wesley Publishing Company, 1985.

- 4. <u>CMOS Analog Circuit Design</u>, Phillip E. Allen and Douglas R. Holberg, Holt, Rinehart and Winston Publishers, 1987.

- 5. <u>Analysis and Design of Analog Integrated Circuits</u>, Paul R. Gray and Robert G. Meyer, John Wiley and Sons Publishers, 1977.

- 6. <u>Switched Capacitor Circuits</u>, Phillip E. Allen and Edgar Sanchez-Sinencio, Van Nostrand Reinhold Publishers, 1984.

- "Active Filter Design Using Operational Transconductance Amplifiers: A Tutorial," Randall L. Geiger and Edgar Sanchez-Sinencio, IEEE Circuits and Devices Magazine, March 1985, pg. 20-32.

- 8. <u>Digital Principles and Design</u>, Donald Givone, 2003, pg 321

- 9. MOSIS SCMOS at http://www.mosis.com

ľ

10. Texas Instruments, Data Sheet for inverter with hysteresis.

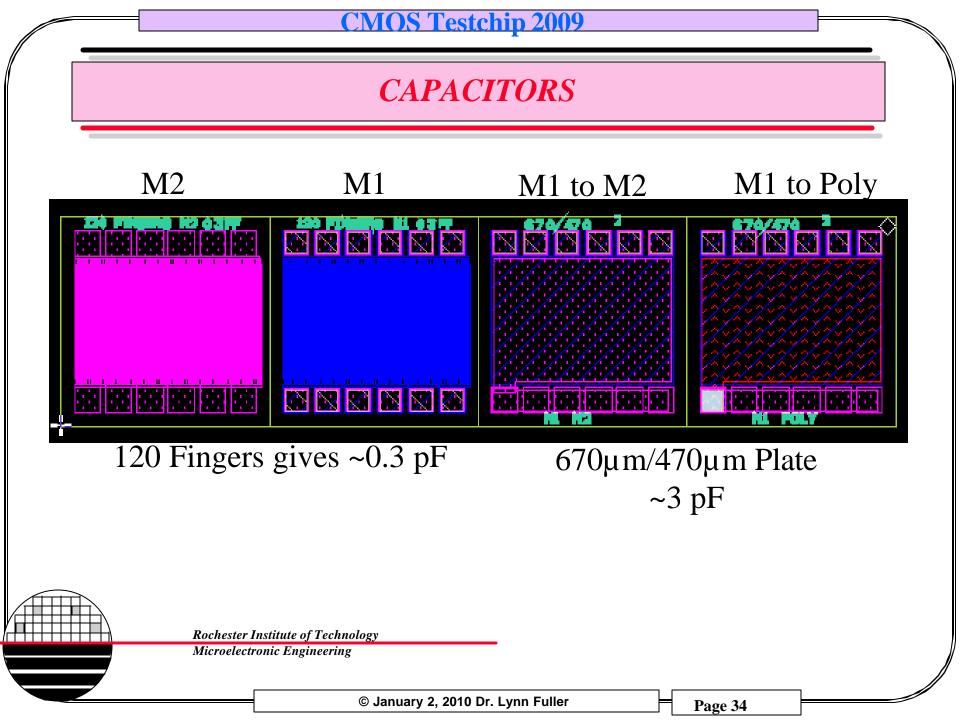

- 1. Calculate the expected values of some of the resistor test structures.

- 2. Calculate the expected values of some of the capacitor test structures.

**Rochester Institute of Technology**

Microelectronic Engineering

© January 2, 2010 Dr. Lynn Fuller