## **OUTLINE**

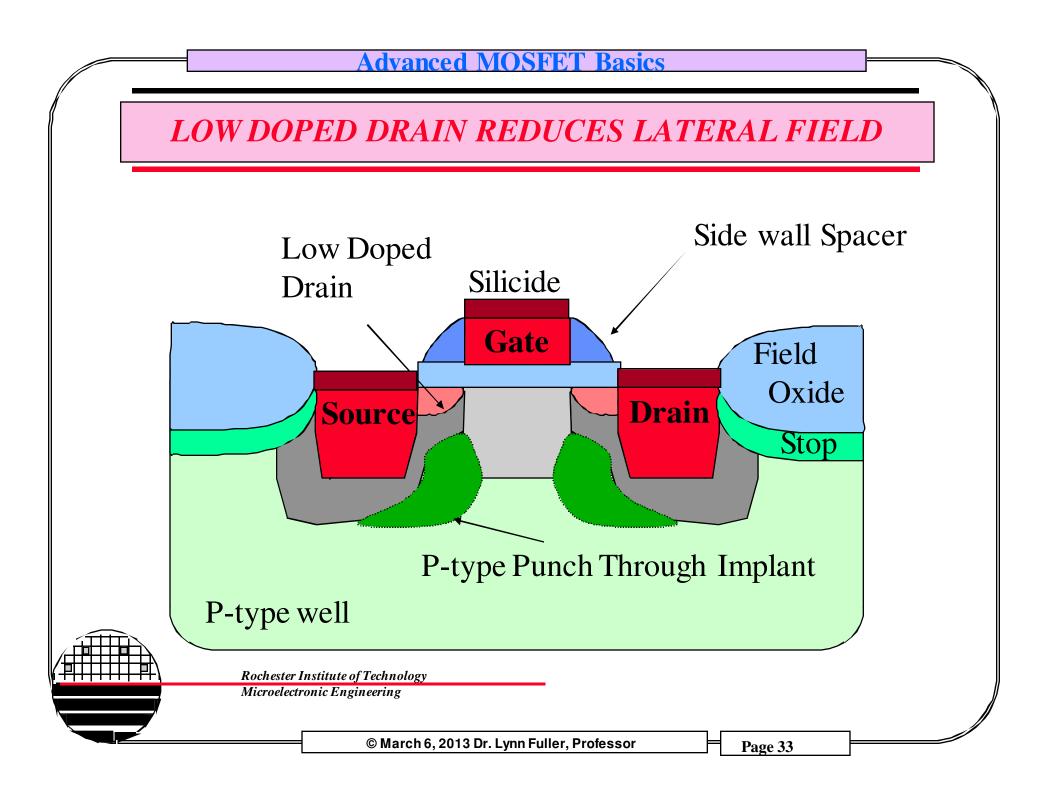

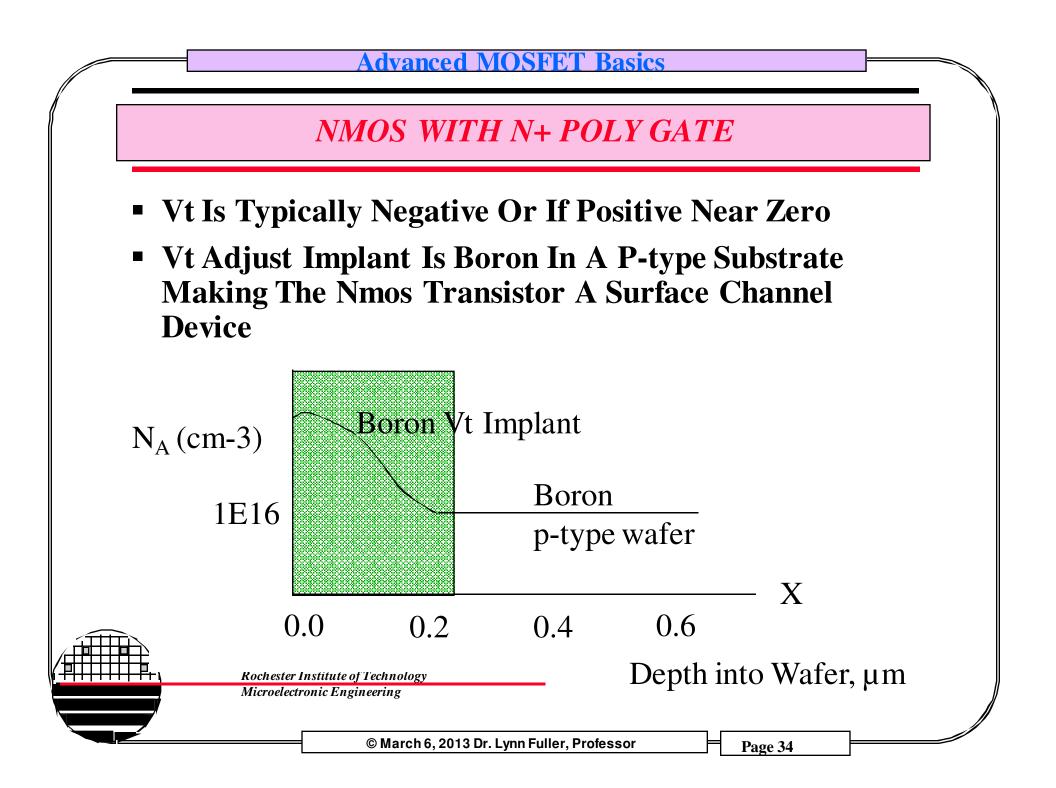

Introduction Short Channel vs Long Channel Effective Channel Length Sub Threshold Effects Low Doped Drain NMOS with N+ Poly Gate PMOS with N+ Poly Gate PMOS with P+ Poly Gate References

Rochester Institute of Technology Microelectronic Engineering

© March 6, 2013 Dr. Lynn Fuller, Professor

Page 2

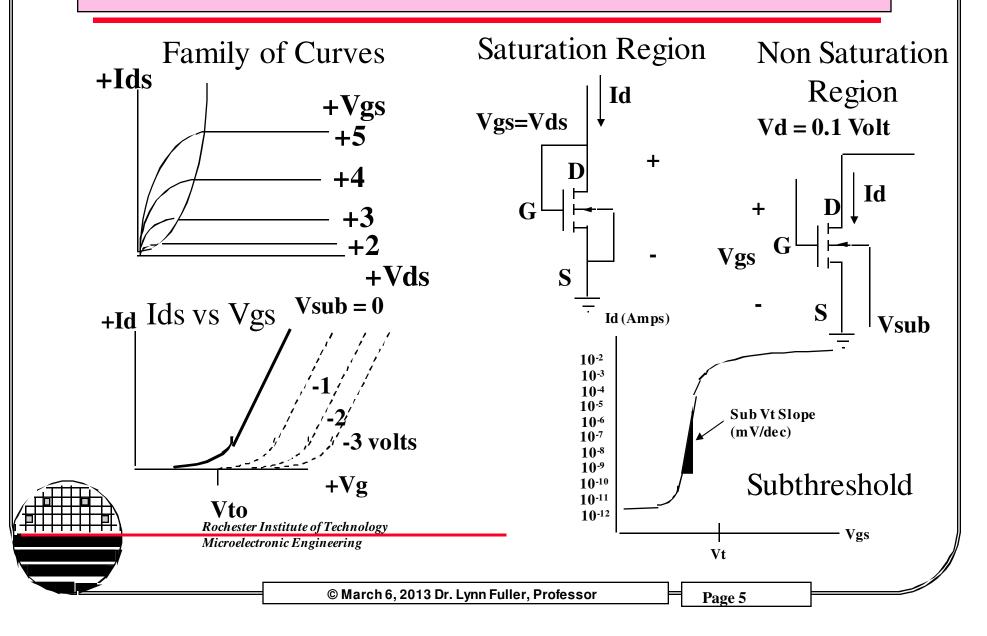

LONG CHANNEL MOSFET I-V CHARACTERISTICS

### **EXAMPLE CALCULATIONS**

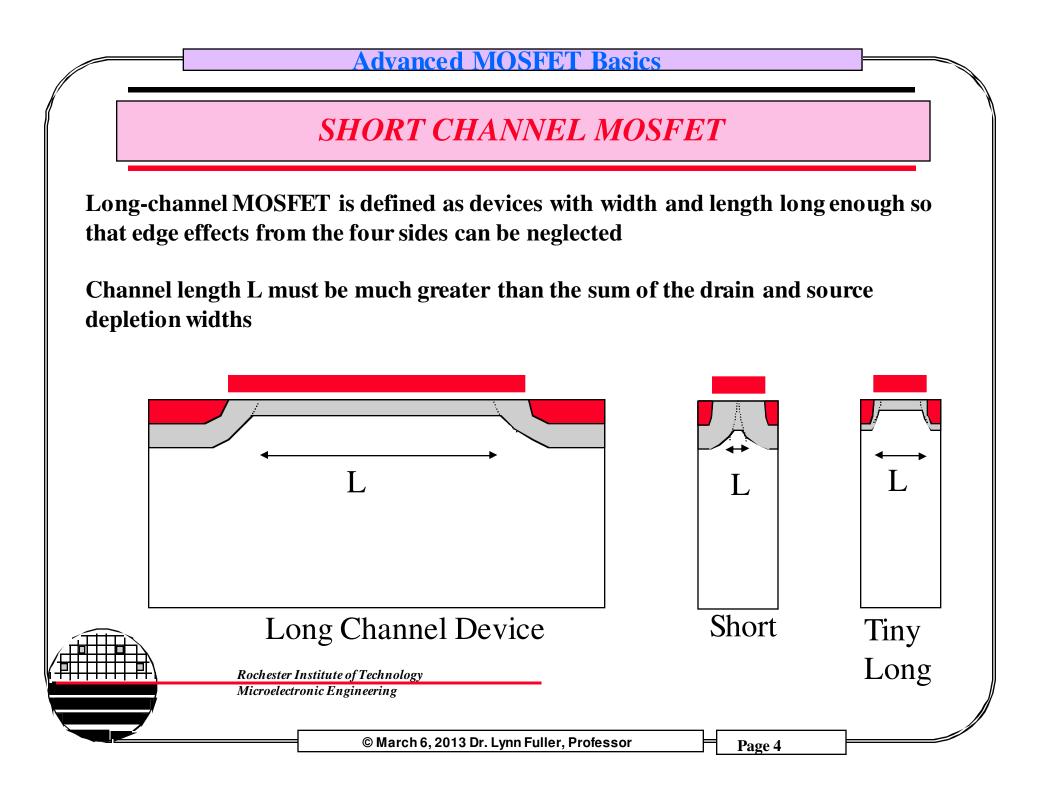

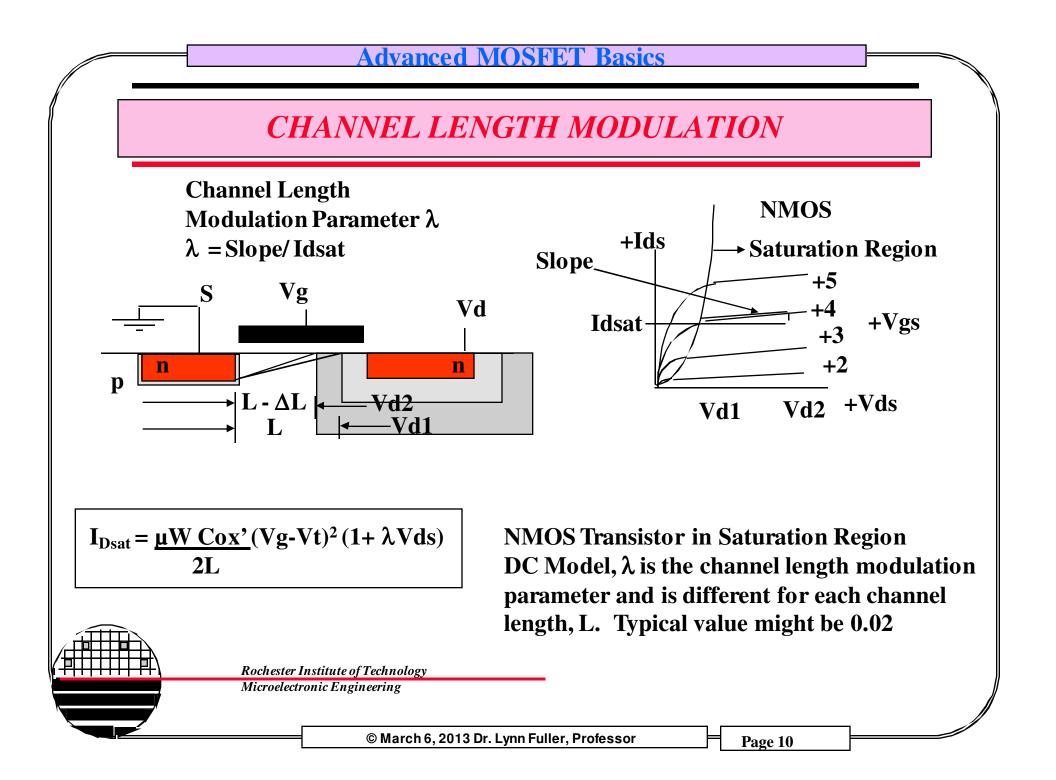

Advanced MOSFET Basics THE SHORT CHANNEL MOSFET Sort channel MOSFET is defined as devices with width and length short enough such that the edge effects can not be neglected. Channel length L is comparable to the depletion widths associated with the drain and source. Gate Drain Source Space Charge Space Charge **Rochester Institute of Technology** Microelectronic Engineering © March 6, 2013 Dr. Lynn Fuller, Professor Page 9

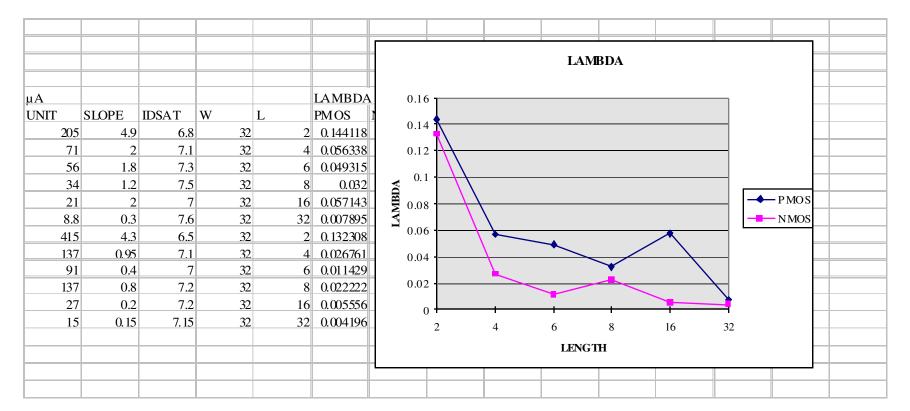

## LAMBDA VERSUS CHANNEL LENGTH

Some MOSFET models use lambda but you would need a different lambda for each different length transistor. More advanced models use and equation to find a lambda as a function of the length Leff

© March 6, 2013 Dr. Lynn Fuller, Professor

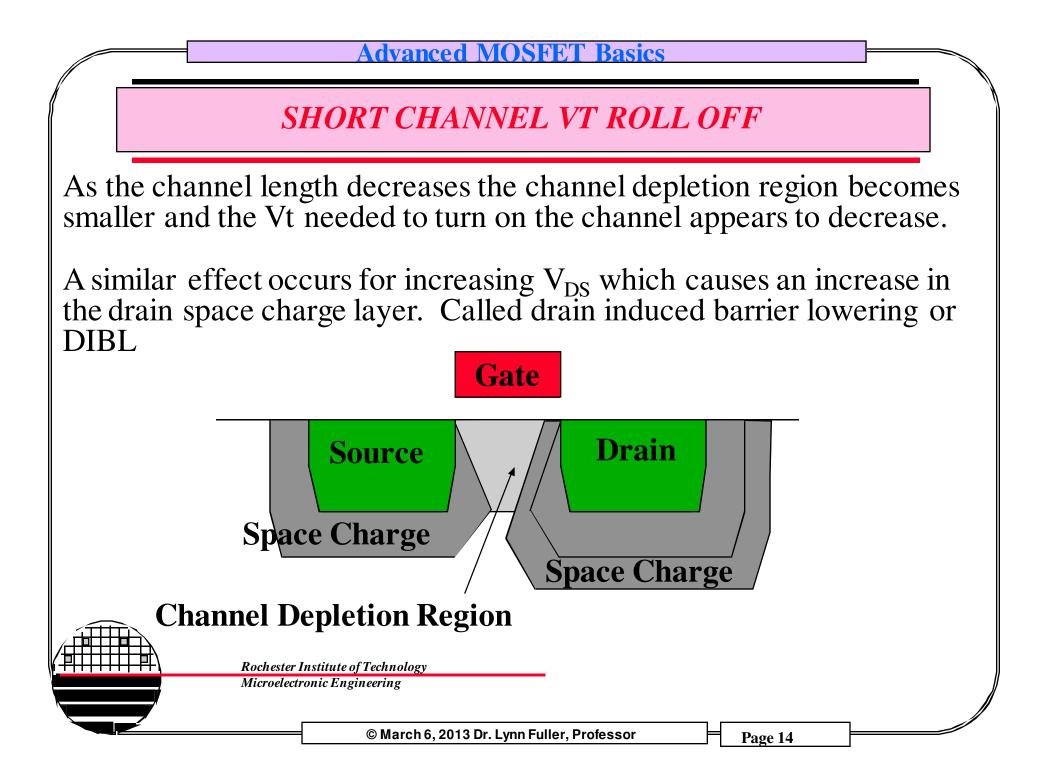

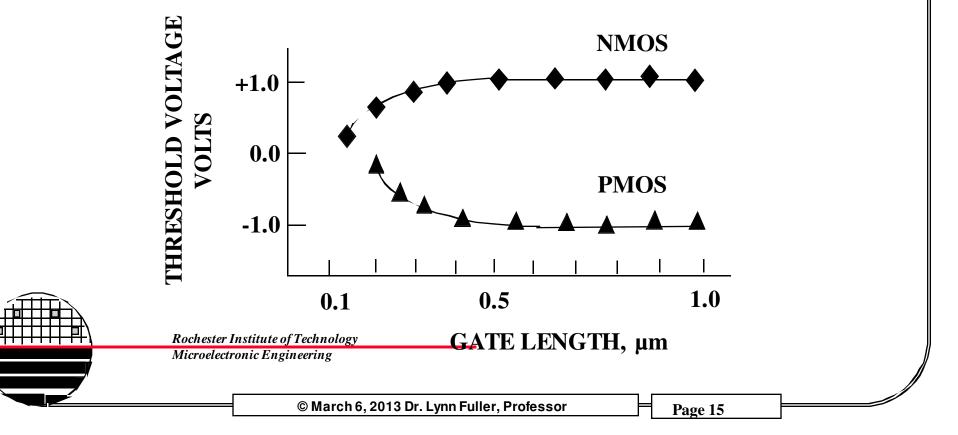

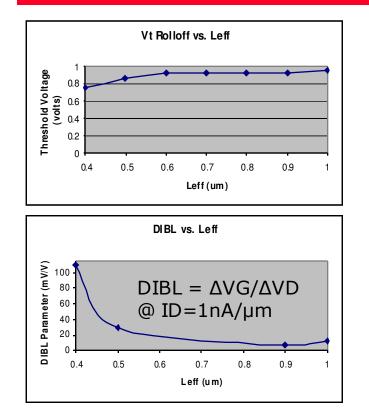

# THRESHOLD VOLTAGE ROLL OFF

A Test Chip is used that includes nMOS and pMOS transistors of various lengths from 0.1  $\mu$ m to 5.0  $\mu$ m and the threshold voltage is plotted versus channel length. The threshold voltage needs to be high enough so that when the input is zero or +Vsupply the transistor current is many decades lower than when it is on. Vt and sub-Vt slope interact.

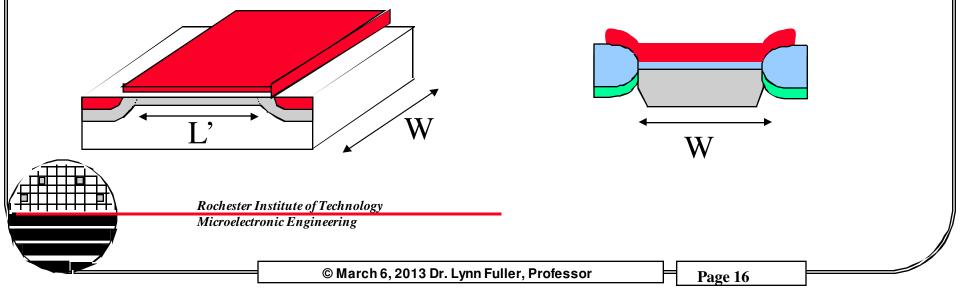

## NARROW GATE WIDTH EFFECTS

Fringing field causes channel depletion region to extend beyond the gate in the width direction Thus additional gate charge is required causing an apparent increase in threshold voltage. In wide channel devices this can be neglected but as the channel becomes smaller it is more important

In NMOS devices encroachment of the channel stop impurity atoms under the gate edges causing the edges to be heavier doped requiring more charge on the gate to turn on the entire channel width. In PMOSFETs the phosphorous pile up at the surface under the field region causes a similar apparent increase in doping at the edges of the channel width

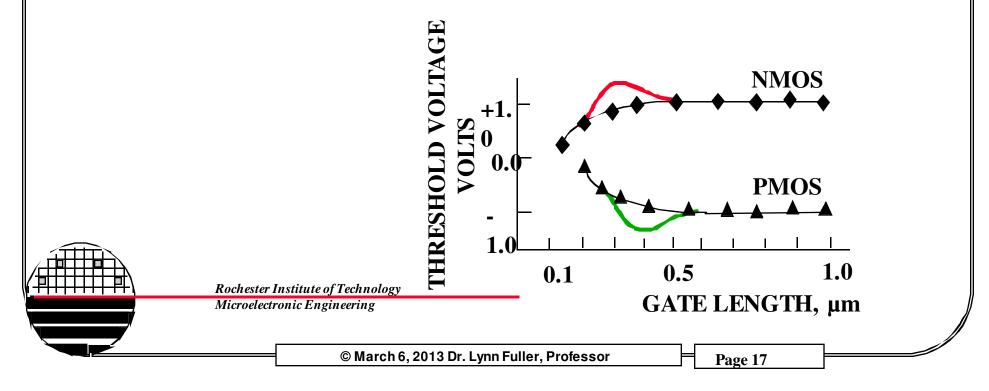

### **REVERSE THRESHOLD VOLTAGE ROLLOFF**

Vt initially increases with decrease in channel length then decreases. This is caused by various effects that result in lateral dopant nonuniformity in the channel.

Example: Oxidation Enhanced Diffusion or enhanced diffusion due to implant damage causing the dopant concentration to be higher in the channel near the drain and source edges of the poly gate.

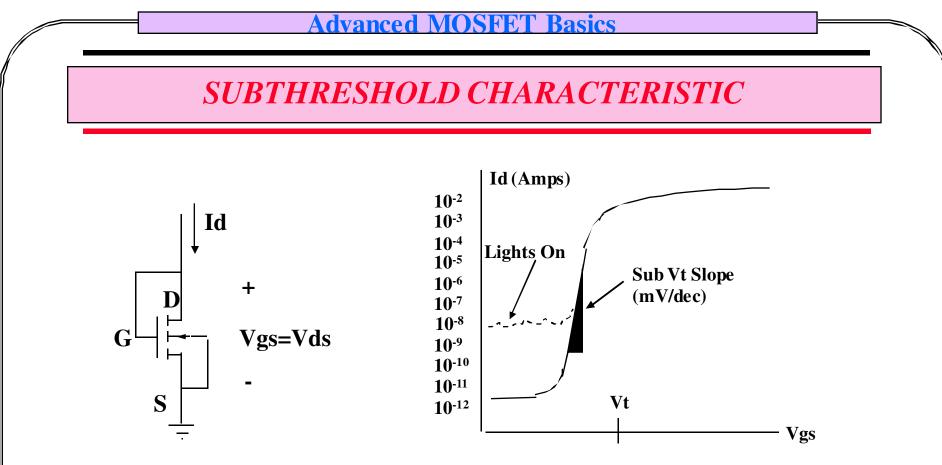

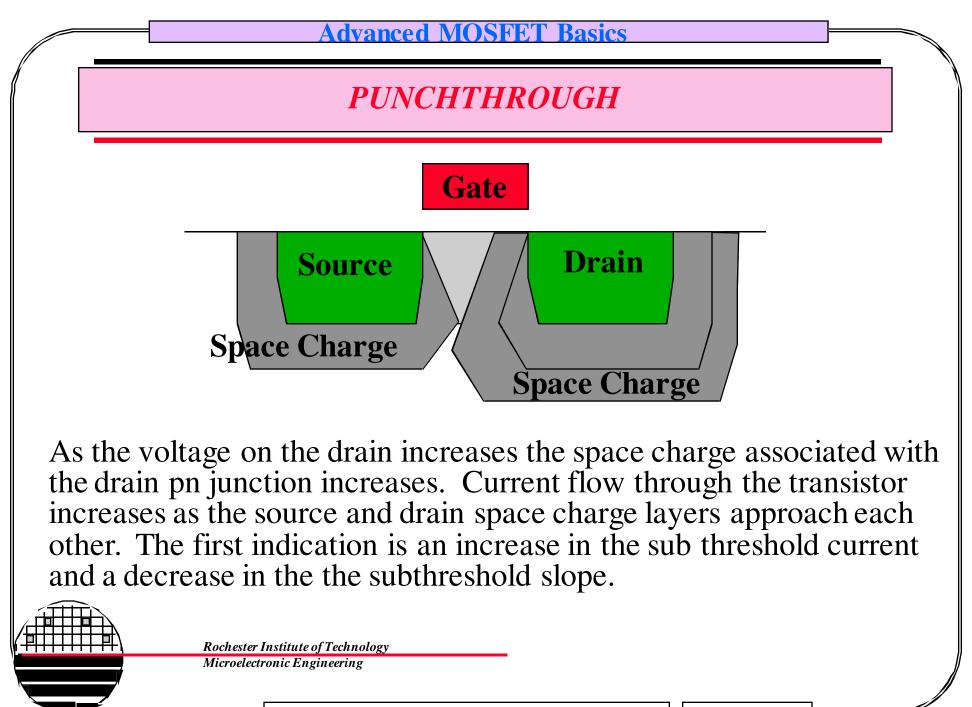

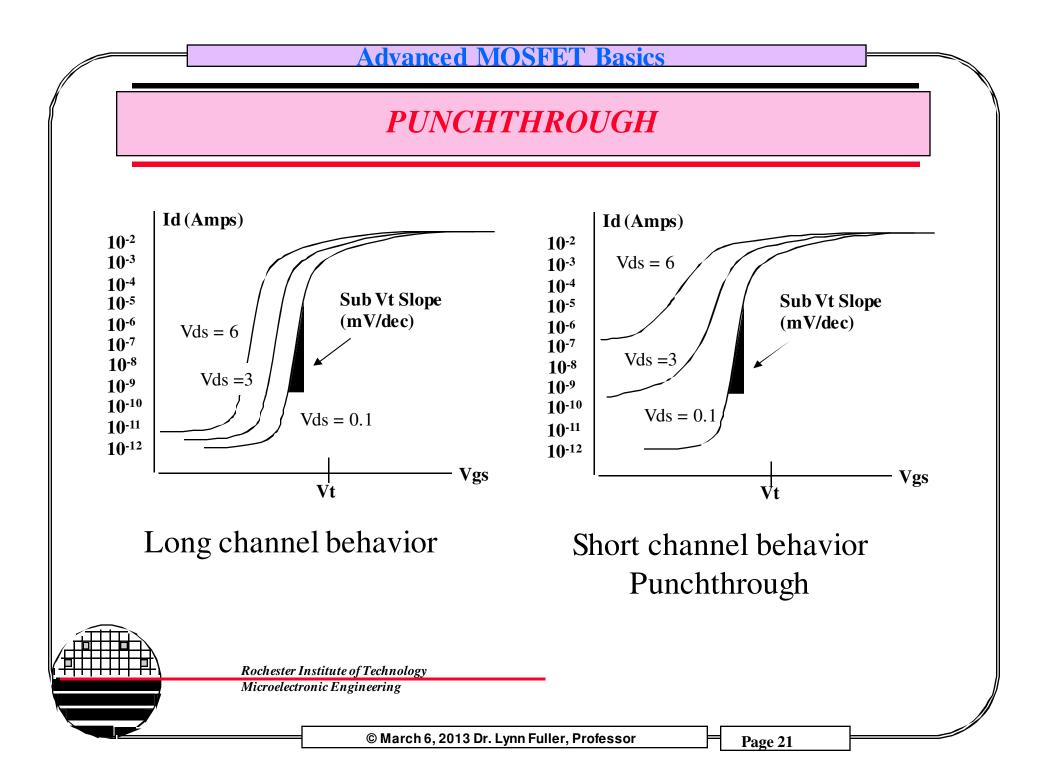

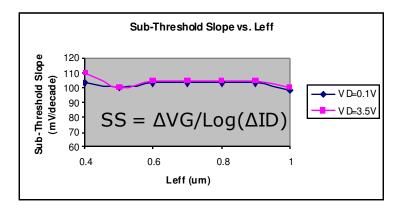

The subthreshold characteristics are important in VLSI circuits because when the transistors are off they should not carry much current since there are so many transistors. (typical value about 100 mV/decade). Thinner gate oxide makes subthreshold slope larger. Surface channel has larger slope than buried channel.

© March 6, 2013 Dr. Lynn Fuller, Professor

Page 20

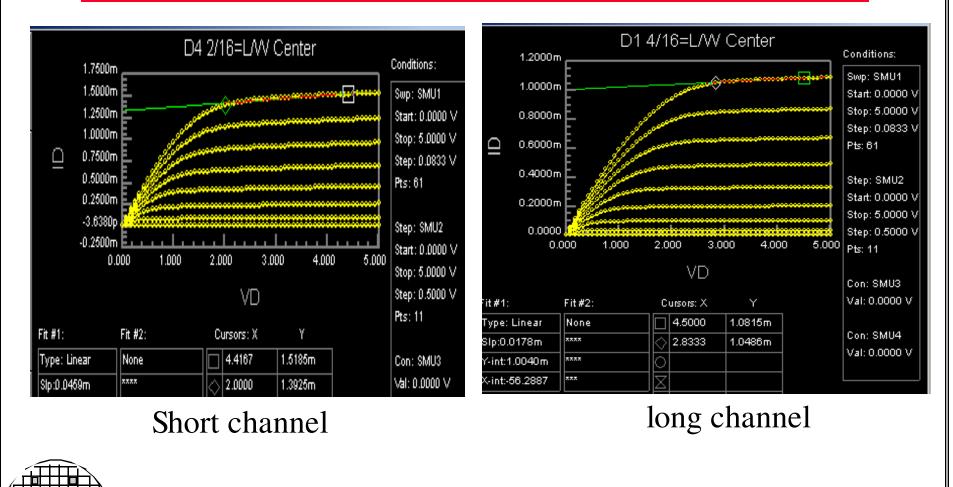

### **MEASURED Id-Vds Family**

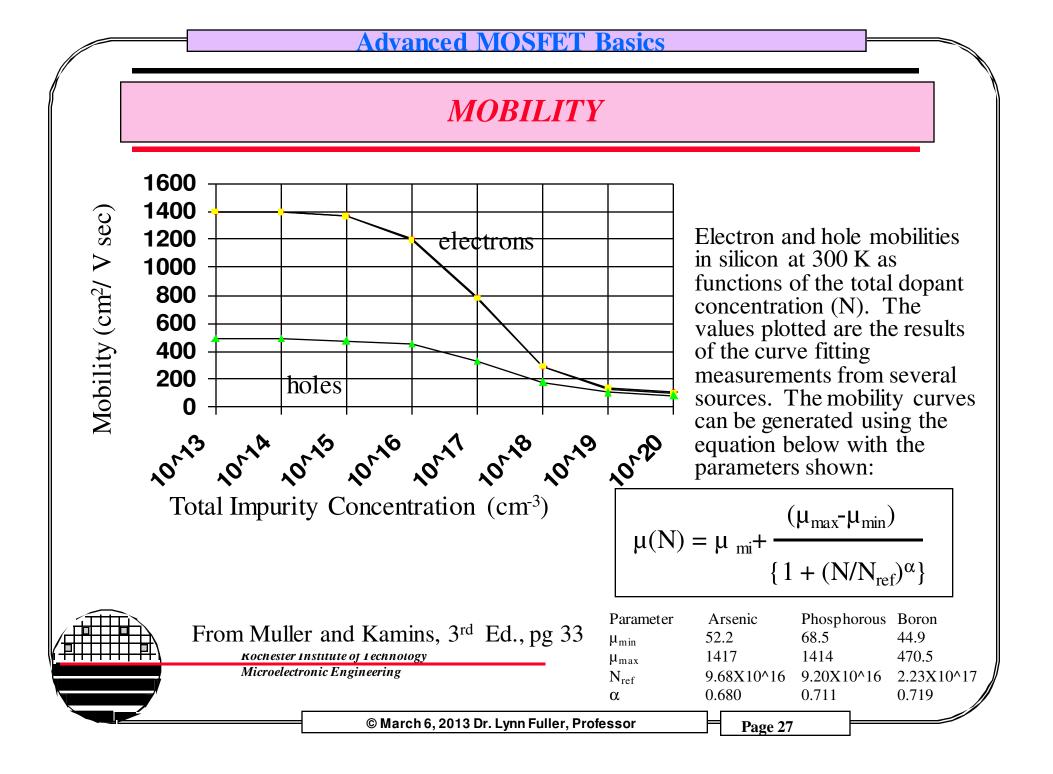

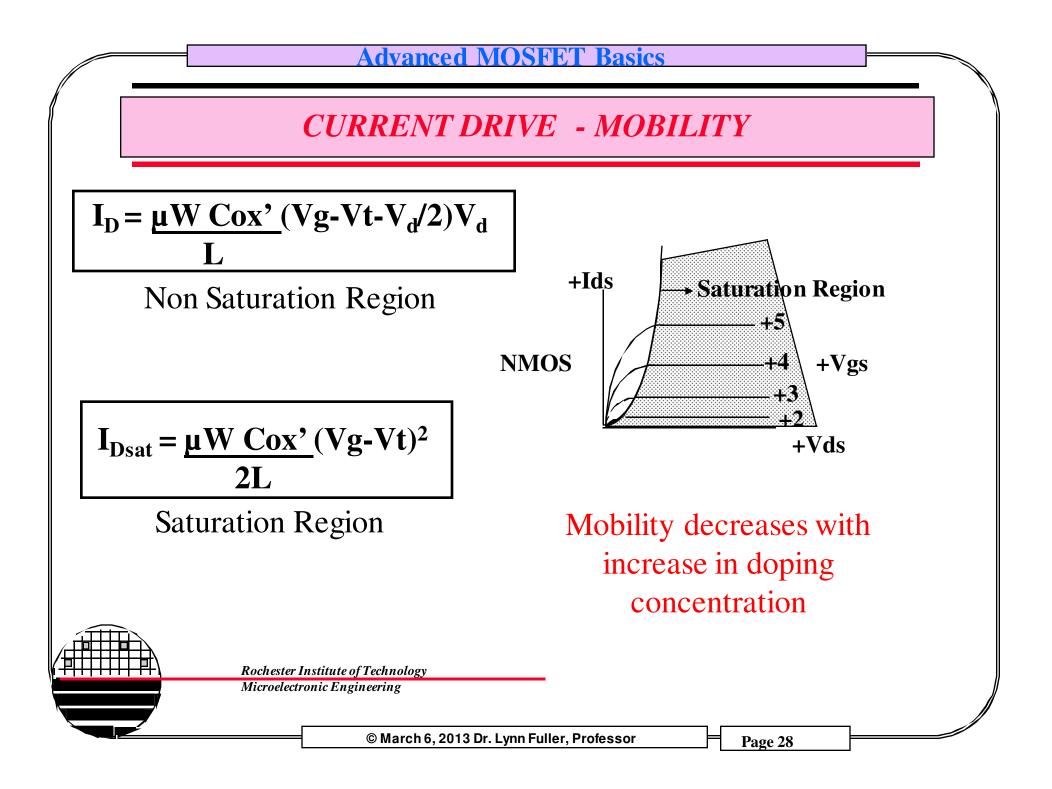

## **MOBILITY DEGRADATION**

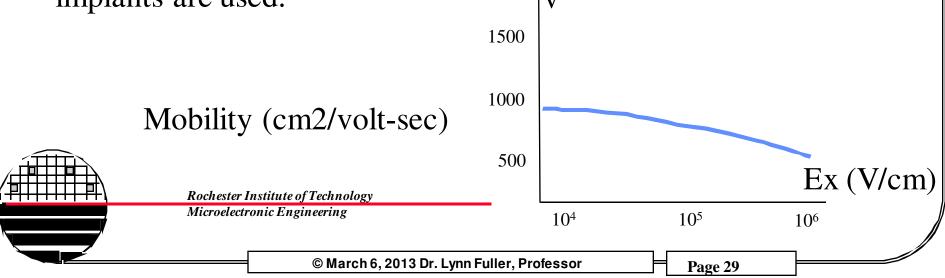

In a MOSFET the mobility is lower than the bulk mobility because of the scattering with the Si-SiO2 interface. The vertical electric field causes the carriers to keep bumping into the interface causing the mobility to degrade. The electric fields can be 1E5 or 1E6 V/cm and at that level the collisions with the interface reduce the mobility even more. The vertical electrical field is higher for heavier doped substrates and when Vt adjust implants are used.

### **MOBILITY DEGRADATION**

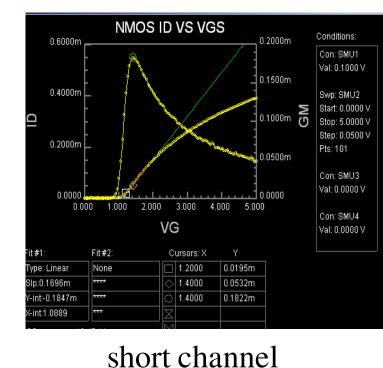

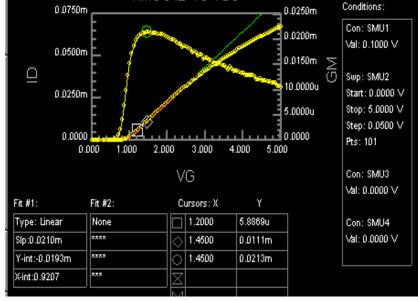

NMOS ID VS VGS

long channel

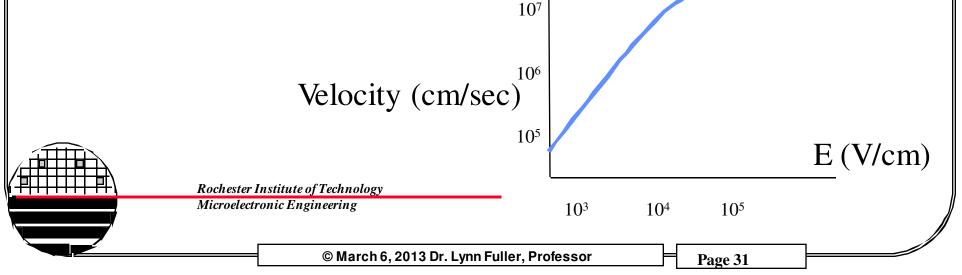

## **VELOCITY-SATURATION**

Carriers in semiconductors typically move in response to an applied electric field. The carrier velocity is proportional to the applied electric field. The proportionality constant is the mobility. Velocity = mobility x electric field =  $\mu$  E At very high electric fields this relationship ceases to be accurate. The carrier velocity stops increasing (or we say saturates) In a one micrometer channel length device with one volt across it the electric field is 1E4 V/cm.

### **VELOCITY SATURATION**

Note: Id should increase with (Vgs-Vt)<sup>2</sup> in long channel devices

© March 6, 2013 Dr. Lynn Fuller, Professor

Page 32

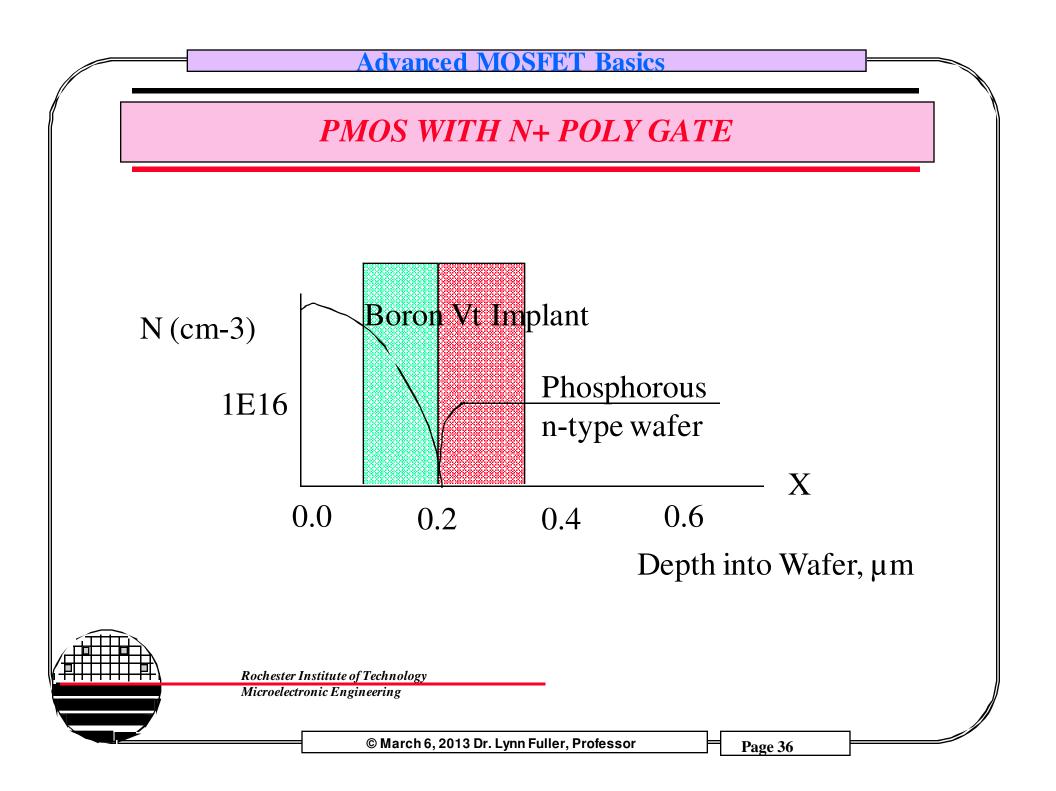

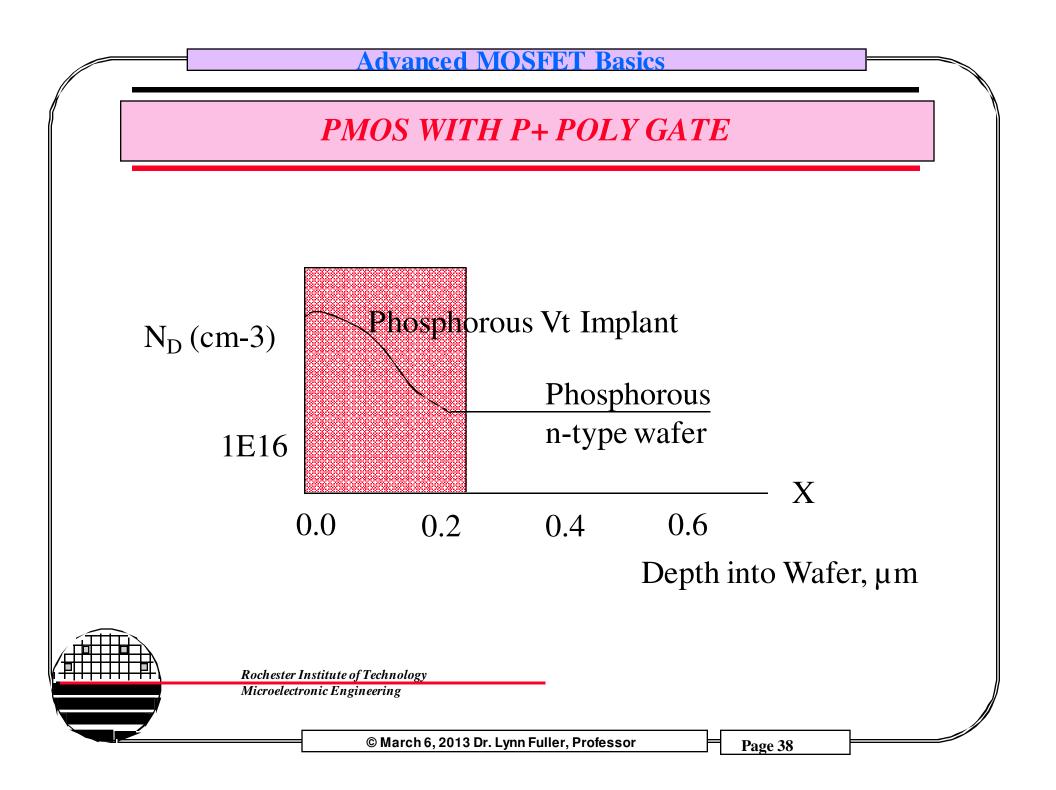

# **PMOS WITH N+ POLY GATE**

- Vt Can Not Be Positive Because All The Contributors To The Vt Are Negative. Even Making Qss=0 And Nd = Zero Does Not Make Vt Positive

- Vt Is Typically More Negative Than Desired Like -2 Volts

- Vt Adjust Implant Is Boron In An N-type Substrate Making The Pmos Transistor A Buried Channel Device (Charge Carriers Move Between Drain And Source At Some Distance Away From The Gate Oxide/Silicon Interface

Rochester Institute of Technology Microelectronic Engineering

Rochester Institute of Technology Microelectronic Engineering

© March 6, 2013 Dr. Lynn Fuller, Professor

© March 6, 2013 Dr. Lynn Fuller, Professor

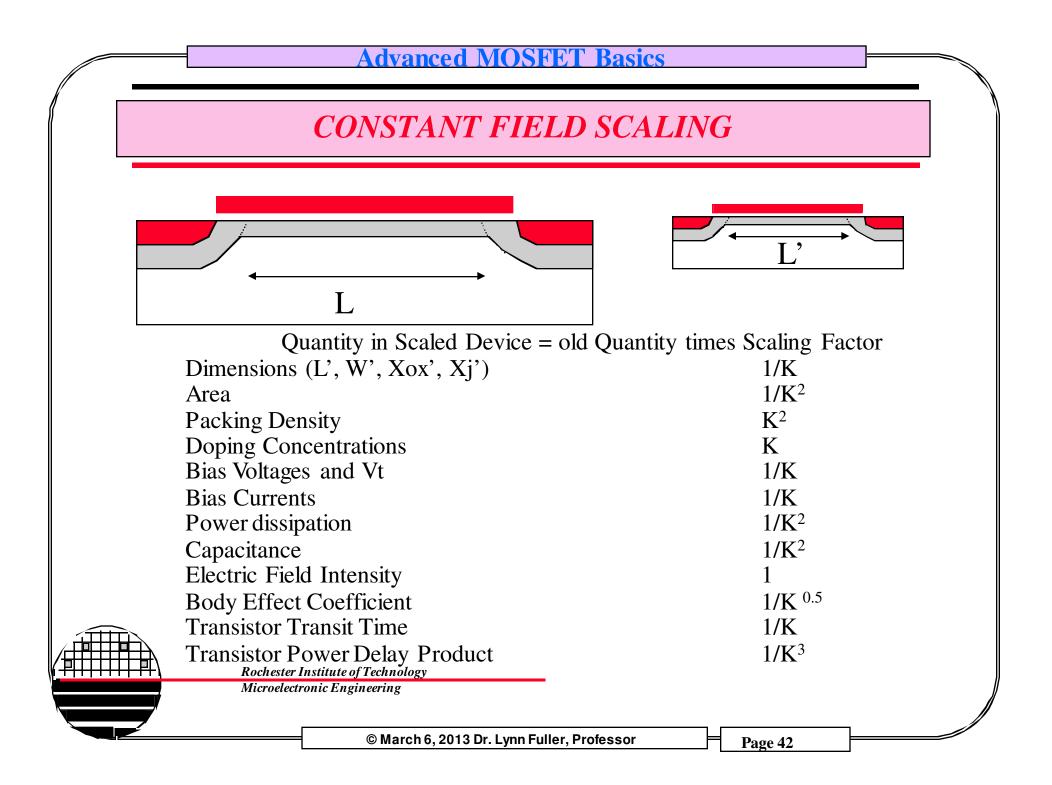

## **SCALING OF MICROCHIPS**

| Micron, Boise ID                                             |      | Lmin   | Chip Area            |

|--------------------------------------------------------------|------|--------|----------------------|

| 16 Meg DRAM                                                  | 1992 | 0.5 µm | $140.1 \text{ mm}^2$ |

|                                                              | 1993 | 0.43   | 96.2                 |

|                                                              | 1994 | 0.35   | 57.0                 |

| single level metal                                           | 1995 | 0.35   | 59.6                 |

|                                                              | 1996 | 0.35   | 43.6                 |

|                                                              | 1996 | 0.30   | 38.3                 |

|                                                              | 1996 | 0.25   | 30.6                 |

|                                                              | 1997 | 0.30   | 29.2                 |

| 64 Meg DRAM                                                  | 1994 | 0.35   | 191.0                |

|                                                              | 1996 | 0.30   | 123.3                |

|                                                              | 1997 | 0.25   | 93.2                 |

| Rochester Institute of Techno<br>Microelectronic Engineering |      |        |                      |

© March 6, 2013 Dr. Lynn Fuller, Professor

| Advanced MOSFET Basics OTHER SCALING RULES |                                                              |                                |                        |                     |  |

|--------------------------------------------|--------------------------------------------------------------|--------------------------------|------------------------|---------------------|--|

| Quantity                                   | Constant<br>Field                                            | Constant<br>Voltage            | Quasi-Const<br>Voltage | tant<br>Generalized |  |

| W, L                                       | 1/K                                                          | 1/K                            | 1/K                    | 1/K                 |  |

| Xox                                        | 1/K                                                          | 1/β                            | 1/K                    | 1/K                 |  |

| N                                          | Κ                                                            | K                              | K                      | $K^2/\beta$         |  |

| V, Vt                                      | 1/K                                                          | 1                              | 1/β                    | 1/β                 |  |

|                                            |                                                              | 1 < β < K                      |                        |                     |  |

|                                            |                                                              | -                              |                        |                     |  |

|                                            | Rochester Institute of Techno<br>Microelectronic Engineering |                                |                        |                     |  |

|                                            | © Ma                                                         | rch 6, 2013 Dr. Lynn Fuller, F | Professor Pag          | e 43                |  |

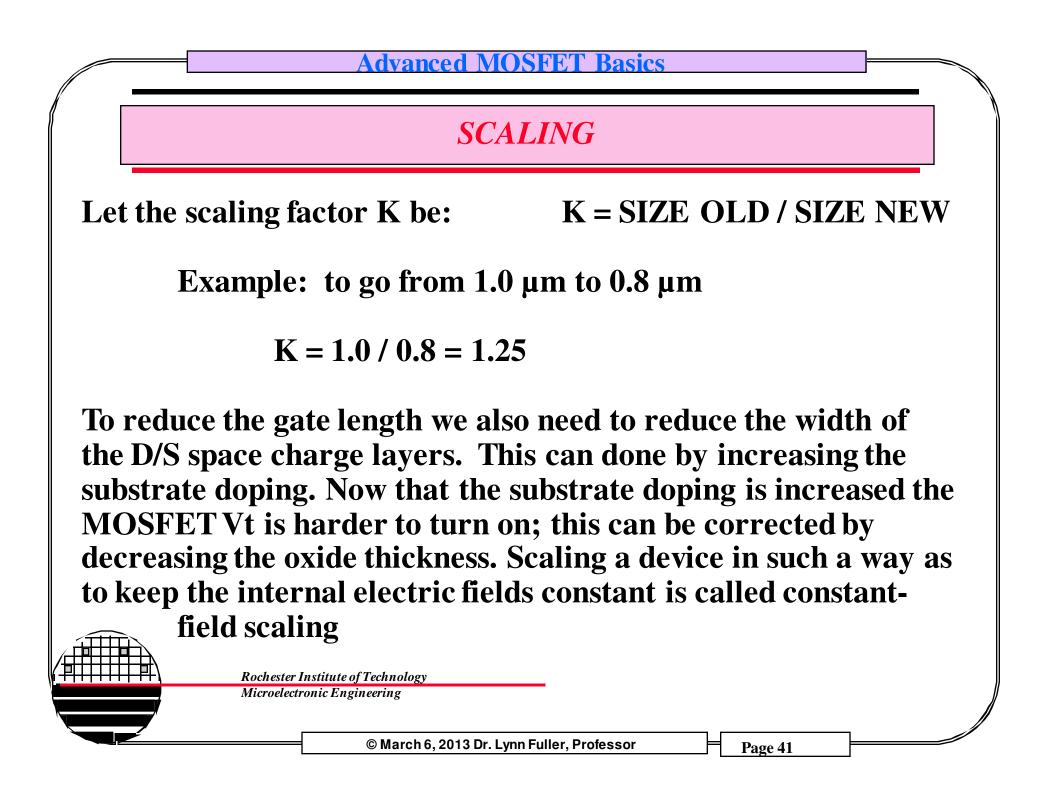

### **SCALING EXAMPLES**

**Example:** 5 Volt, L=1.0  $\mu$ m NMOS, Na = 5E16, Xox=250 Å Scale to 0.8  $\mu$ m NMOS. Constant Field Scaling

K = 1.0/0.8 = 1.25

Xox= 250/1.25 = 200 Å

$N = 5E16 (1.25) = 2.5E17 \text{ cm}^{-3}$

Vsupply = 5Volts/ 1.25 = 4 Volts and Vt = 1/1.25 = 0.8 Volts

|            | Institute of Technology                    |         |   |

|------------|--------------------------------------------|---------|---|

| Microelect | ronic Engineering                          |         |   |

|            | © March 6, 2013 Dr. Lynn Fuller, Professor | Page 44 | ] |

# **GATE OXIDE THICKNESS**

The gate should be as thin as possible to reduce the short channel effects. In addition there is a limit imposed by considerations that affect the long term reliability of the gate oxide. This requirement imposes a maximum allowed electric field in the oxide under the long term normal operating conditions. This limit is chosen as 80% of the oxide field value at the on-set of Fowler-Nordheim (F-N) tunneling through the oxide. Since the latter is 5 MV/cm, a 4 MV/ cm oxide field is considered as the maximum allowed for long term, reliable operation. For example:

For 2.5 volt operation, Xox is set at: Xox = Vdd /Emax

$=2.5 \text{ V/4MV/cm} = 65 \text{\AA}$

Rochester Institute of Technology Microelectronic Engineering

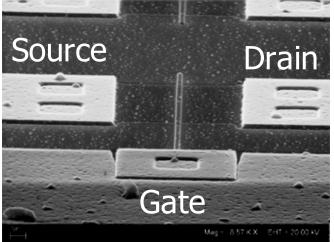

## **SALICIDE**

Ti Salicide will reduce the sheet resistance of the poly and the drain and source regions. Salicide is an acronym for Self Aligned Silicide and Silicide is a material that is a combination of silicon and metal such as Ti, W or Co. These materials are formed by depositing a thin film of the metal on the wafer and then heating to form a Silicide. The Silicide forms only where the metal is in contact with the Silicon or poly. Etchants can remove the metal and leave the Silicide thus the term **S**elf Aligned Silicide or SALICIDE.

Microelectronic Engineering

**Rochester Institute of Technology**

© March 6, 2013 Dr. Lynn Fuller, Professor

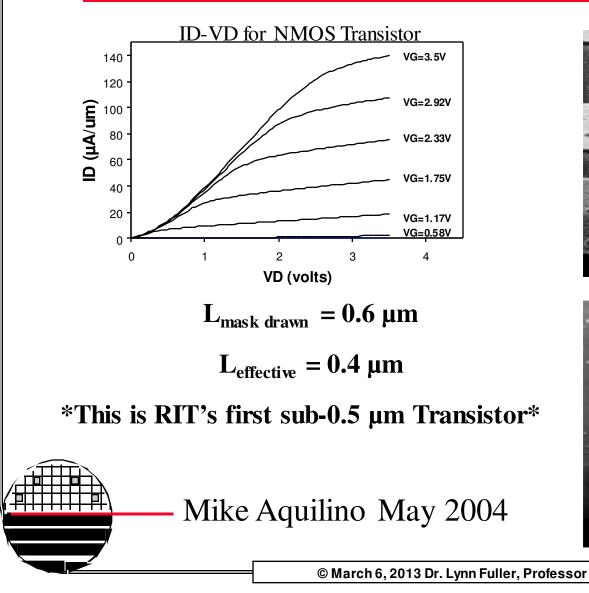

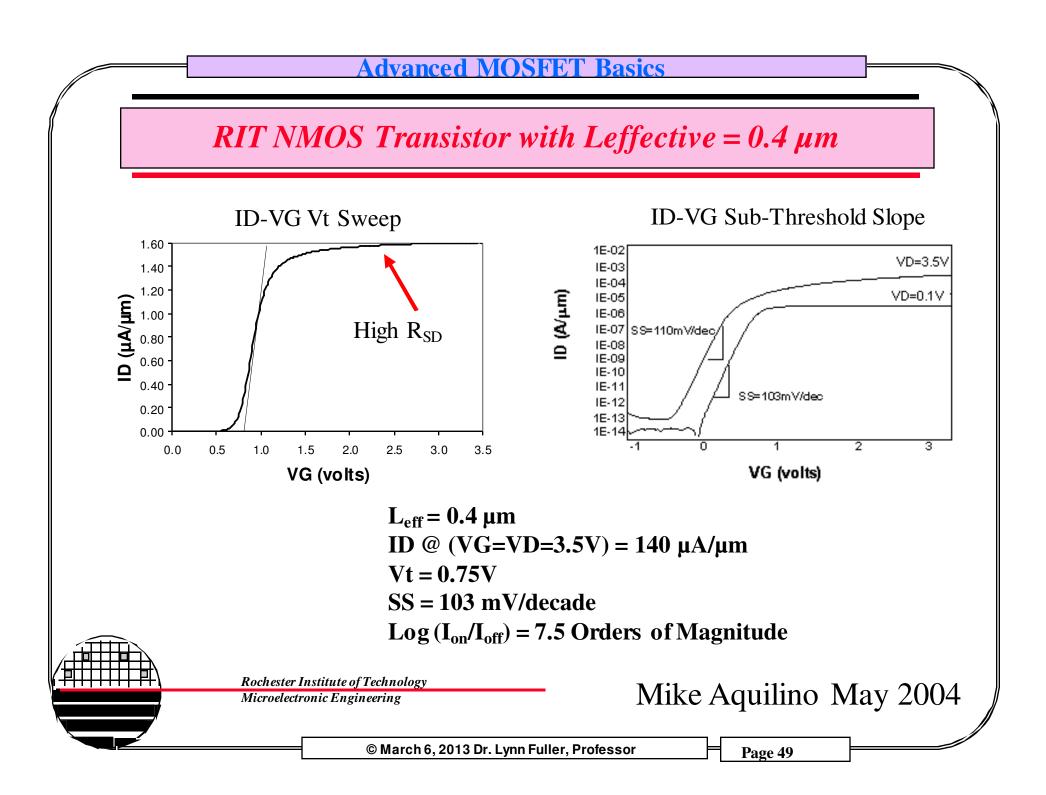

## **RIT NMOS Transistor with Leffective = 0.4 \mu m**

### **RIT NMOS Transistor with Leffective = 0.4 \mu m**

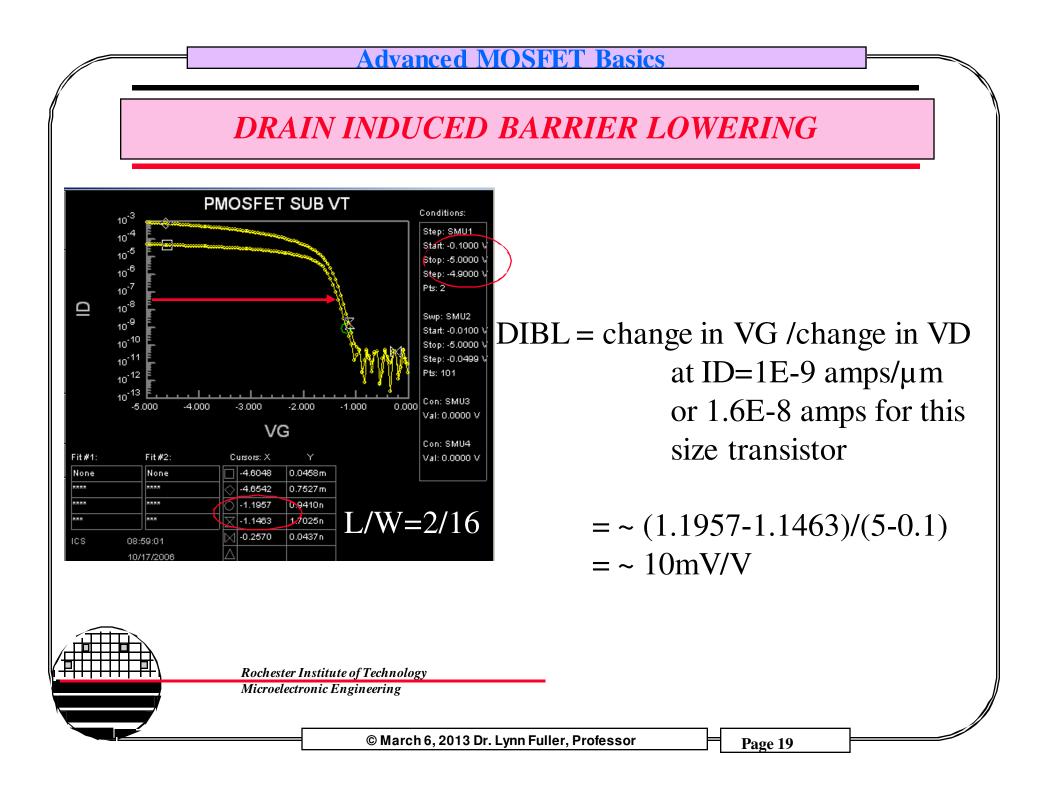

| L <sub>eff</sub><br>(µm) | Vt<br>(V) | SS<br>(mV/dec) | DIBL<br>(mV/V) |

|--------------------------|-----------|----------------|----------------|

| 0.4                      | 0.75      | 103            | 110            |

| 0.5                      | 0.85      | 100            | 29             |

- 0.5 um exhibits well controlled short channel effects

- 0.4 um device can be used depending on off-state current requirements

- 33% Increase in Drive Current compared to 0.5 um device

## Mike Aquilino May 2004

© March 6, 2013 Dr. Lynn Fuller, Professor

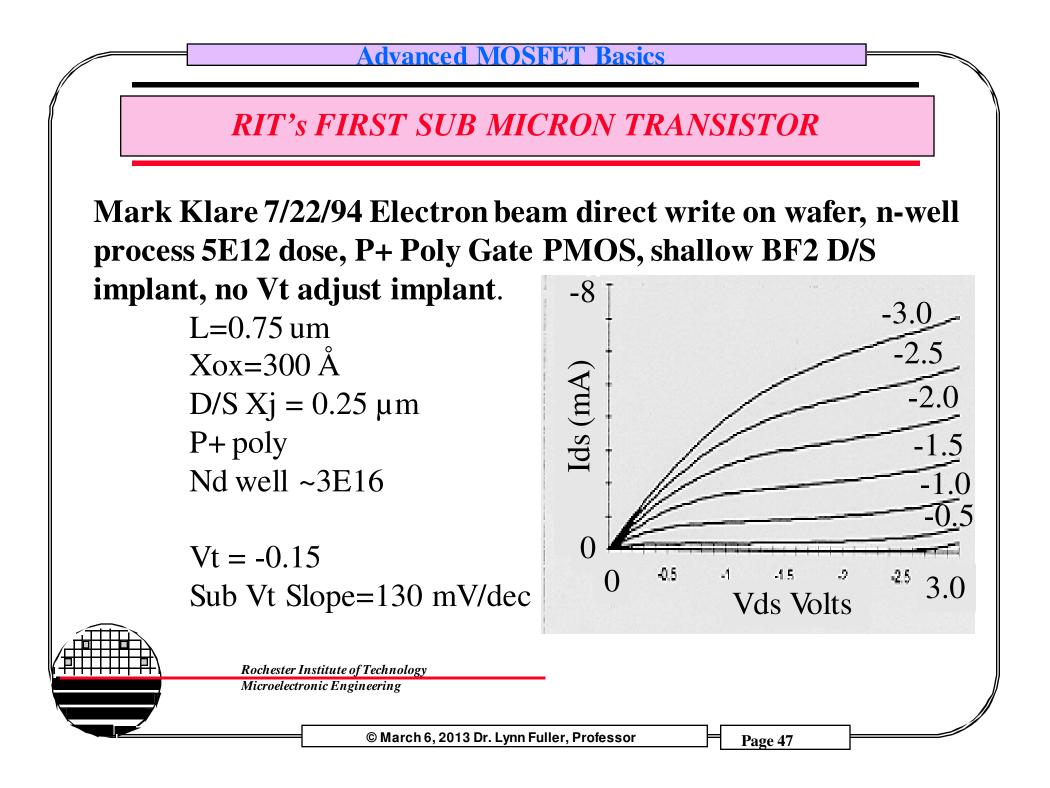

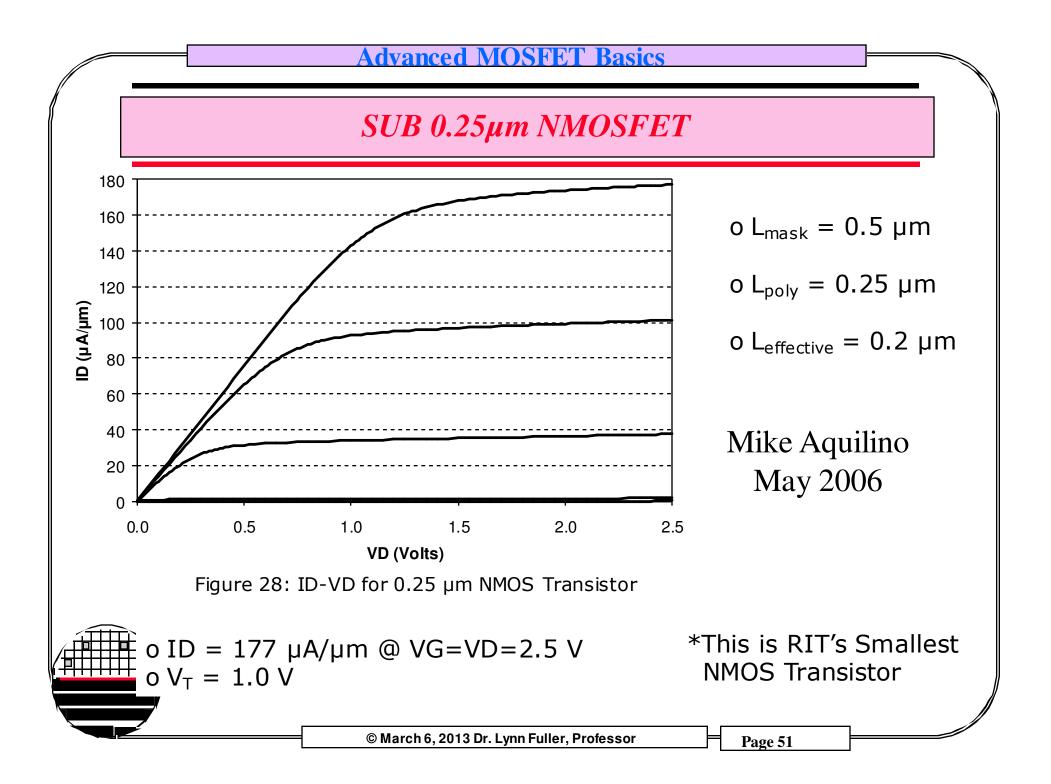

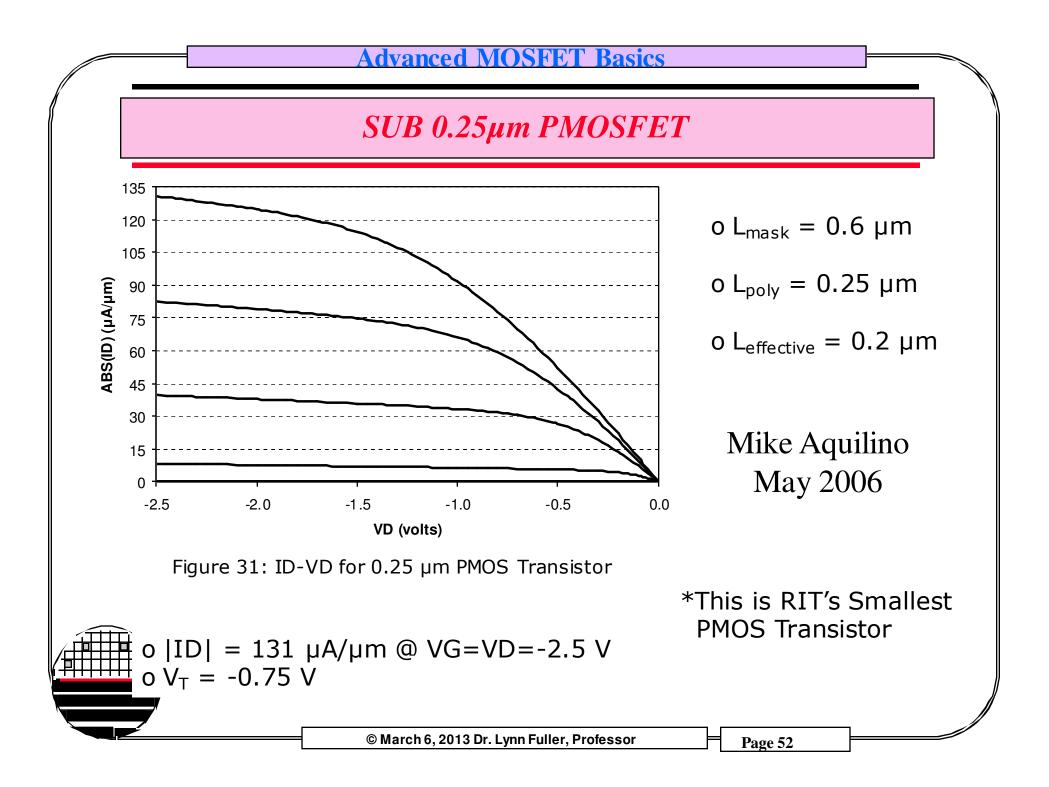

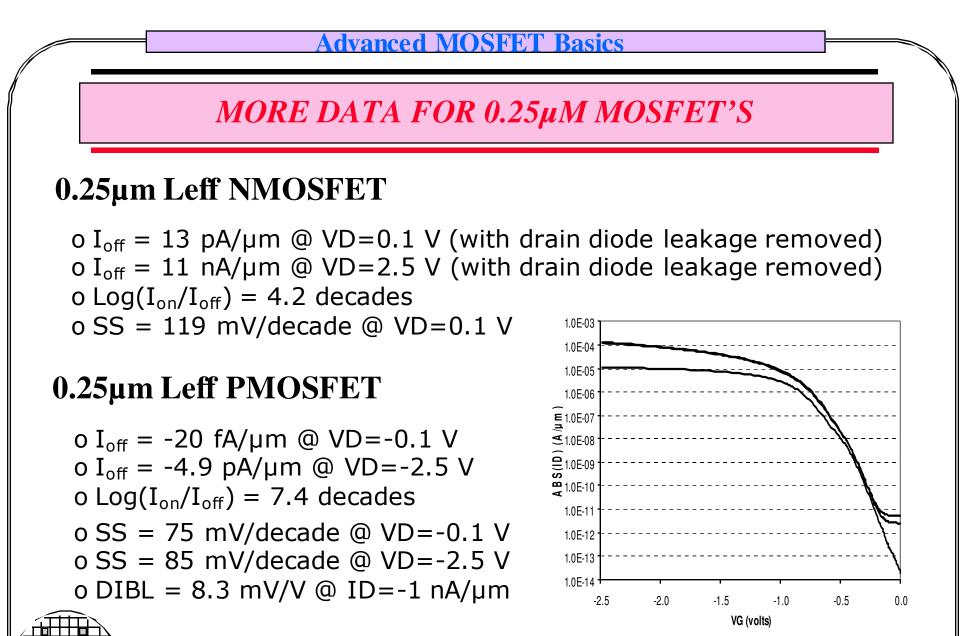

ID-VG for 0.25 µm PMOS Transistor

© March 6, 2013 Dr. Lynn Fuller, Professor

Rochester Institute of Technology Microelectronic Engineering

#### **REFERENCES**

- 1. Device Electronics for Integrated Circuits, Richard S. Muller, Theodore I. Kamins, John Wiley & Sons., 1977.

- 2. Silicon Processing for the VLSI Era, Vol. 2&3., Stanley Wolf, Lattice Press, 1995.

- 3. The Science and Engineering of Microelectronic Fabrication, Stephen A. Campbell, Oxford University Press, 1996.

- The MOS Transistor, Yannis Tsividis, 2<sup>nd</sup> Edition, McGraw Hill, 1999

Rochester Institute of Technology Microelectronic Engineering

© March 6, 2013 Dr. Lynn Fuller, Professor

| Advanced MOSFET Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOMEWORK – SHORT CHANNEL MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

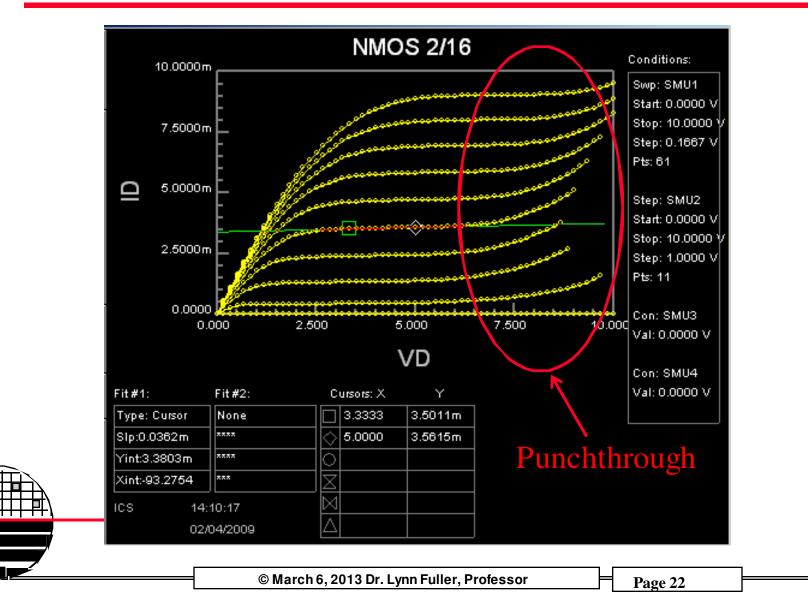

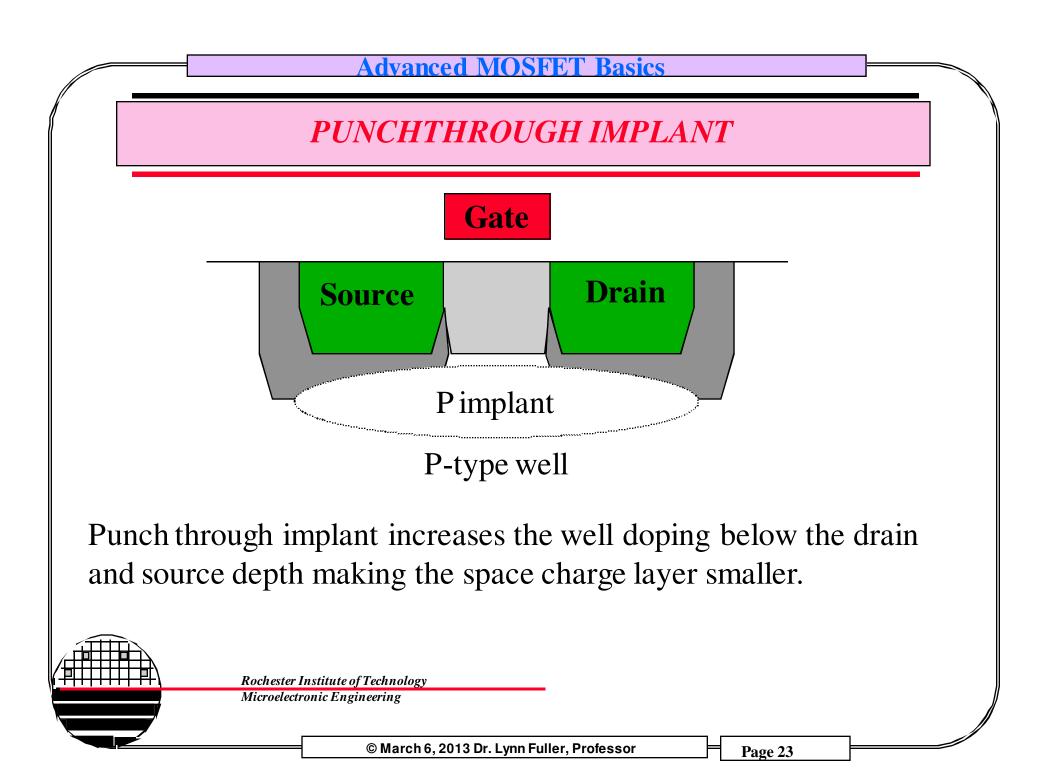

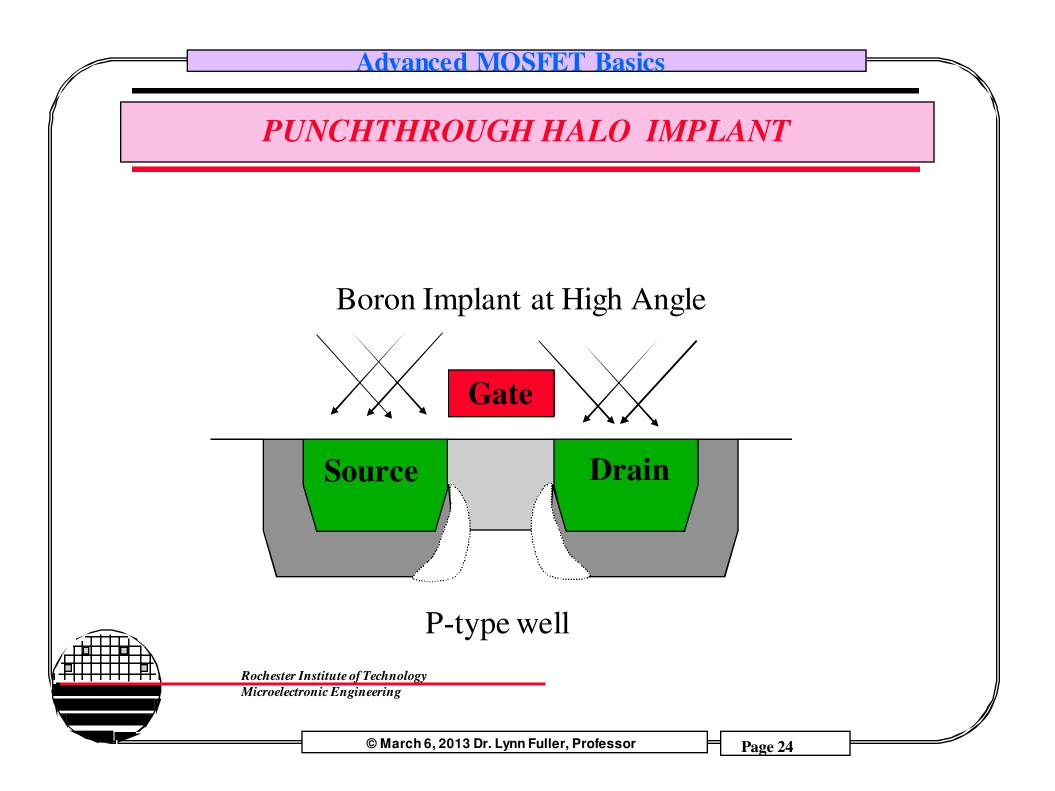

| <ol> <li>In short channel devices the threshold voltage becomes less than expected for<br/>long channel devices. Why.</li> <li>Explain reverse short channel effect.</li> <li>What is the effect of narrow channel width on transistor device<br/>characteristics.</li> <li>What is the purpose of low doped drain structures?</li> <li>How does mobility degradation and velocity saturation effect transistor device<br/>characteristics?</li> <li>Why is P+ doped poly used for PMOS transistors.</li> <li>What is the difference between mask channel length and effective channel<br/>length.</li> <li>What is punchthrough? What processing changes can be made to compensate<br/>for punchthrough?</li> </ol> |

| 9. When scaling from 2 um to 1.5 um give new values for: device dimensions W,L,Xox, doping concentration, bias voltages, bias currents, power dissipation, transit time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10. What is SALICIDE process. Why is it used?  Rochester Institute of Technology Microelectronic Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |