## **ABSTRACT**

DAGTEKIN, MUSTAFA. A Chopper Modulated Amplifier System Design for *in vitro* Neural Recording. (Under the direction of Robert J. Trew.)

Neural recording systems measure very low-amplitude signals of less than 5 kHz bandwidth. Low-frequency noise processes such as flicker noise and DC offset can degrade the quality of recordings made by such systems. A chopper modulated amplifier system is described and shown to reduce the flicker noise in neural recording systems by 10 to 20 dB. The amplifier system was implemented using the MOSIS ABN 1.5 micron technology. While the amplifier system contained an imperfection that prevented it from working with actual tissue samples, it worked well enough to prove that chopper modulation does reduce flicker noise appreciably. All of the details are presented along with studies of gate-metal-free transistors and custom-made MOSIS-based recording electrodes.

# A CHOPPER MODULATED AMPLIFIER SYSTEM DESIGN FOR IN VITRO NEURAL RECORDING

# by MUSTAFA DAGTEKIN

A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

#### **COMPUTER ENGINEERING**

Raleigh 2006

#### **APPROVED BY:**

| Dr. Griff L. Bilbro     | Dr. Veena Misra    |

|-------------------------|--------------------|

|                         |                    |

|                         |                    |

|                         |                    |

| Dr. Robert M. Grossfeld | Dr. John M. Wilson |

|                         |                    |

|                         |                    |

| Dr. Robert              | I Trew             |

| Chair of Advisor        |                    |

# **DEDICATION**

I dedicate this thesis to my grandfathers, Fehmi Dağtekin and Abdullah Dağtekin. Both of them passed away while I was in the PhD program.

## **BIOGRAPHY**

Mustafa Dagtekin, son of Hatice and Ahmet, was born in a small village called Hacıhüseyinler in Elazığ, Turkey. In 1996, he received a B.Sc. degree in Electronics and Telecommunications Engineering at Istanbul Technical University. After starting his Master's program in Biomedical Engineering at Bosphorus University he was awarded by Turkish Ministry of Education a scholarship for graduate education in US. He attended North Carolina State University and got his M.Sc. degree in Computer Engineering in 1999. He finished his PhD program in 2006. His research interests include analog and digital IC Design, board level systems design, FPGAs and biomedical devices.

#### **ACKNOWLEDGEMENTS**

I simply could not have been able to finish this without the help of a lot of people.

First, I want to thank Dr. Wentai Liu for getting me involved in this topic, helping and supporting me as long as he could.

I would like to thank Dr. Robert Grossfeld for permitting access to his lab, teaching me how to work in a zoology lab, and spending a lot of time working with me for my experiments. I am also grateful to his students for extending a helping hand.

I want to thank the chair of my committee Dr. Bob Trew and my committee members Dr. Griff Bilbro and Dr. Veena Misra for scrutinizing and reviewing my work and advising to improve my work. I must especially thank Dr. John Wilson and Dr. Steve Lipa for spending a lot of time to understand my work and help me to reach my research goals.

I would like to thank Rizwan Bashirullah for listening to my problems and counsel me through this ordeal. I also thank Rajeev Ramanath for his kind support and encouragement. I want to thank Chris DeMarco for convincing me to join the group and all the help and support he has given. I want to thank Kasin Vichienchom, Mehmet R. Yüce, Alper Kendir, Guoxing Wang, Liang Zhou and probably so many more people that helped in one way or other.

I must thank Dr. Joel Trussell for his efforts to see me finishing this. I want thank Tara Britt and all the people in the ECE Department's administration for all their help.

I want to thank Dr. J. Fulghum for the great job he has done with my back surgeries, Dr. Mary Bengtson for her care in my medical problems, Dr. Michael Bowman for curing my headaches. I also want to thank Dr. Michael Bachmann, Dr. John Wallace and Dr. Elizabeth King for their help.

I would like to thank my sister, Mukadder (Dağtekin) Bingöl, for selflessly coming here to help me during my most difficult years. I thank my parents, Ahmet and Hatice, for their unconditional love and support. They have been working like no other for as long as remember to see their children educated and taken care for. I thank my sister Meral Dağtekin and Fatih Volkan Dağtekin for their support and love. I must also thank my extended family.

Well, if I forgot any names please forgive me.

# **Table of contents**

| LIST OF  | TABLES                                           | viii         |

|----------|--------------------------------------------------|--------------|

| LIST OF  | FIGURES                                          | ix           |

| СНАРТЕ   | ER I. INTRODUCTION                               | 1            |

| СНАРТЕ   | ER II. LITERATURE REVIEW                         | 3            |

|          | RODUCTION                                        |              |

| 2.2 CUL  | TURED CELL RECORDING METHODS                     | 3            |

| 2.2.1    | Estit decition distributed Electronic Recordings |              |

| 2.2.2    | 1                                                |              |

| 2.2.3    |                                                  |              |

| 2.2.4    | - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1          |              |

|          | V FREQUENCY NOISE SOURCES                        |              |

|          | CKER NOISE AND THERMAL NOISE                     |              |

| 2.4.1    | DC Offset                                        |              |

| 2.4.2    |                                                  |              |

|          | SE CANCELLATION TECHNIQUES                       |              |

| 2.5.1    | Chopper Modulation                               |              |

| 2.5.2    | G                                                |              |

|          | LEMENTATION PROBLEMS AND SOLUTIONS               |              |

| 2.6.1    | Clock Feedthrough and Channel Charge Injection   |              |

|          | NCLUSIONS                                        |              |

| Refer    | ences                                            |              |

| CHAPTE   | ER III. A CHOPPER MODULATED NEURAL RECORDI       | NG SYSTEM 27 |

| 3.1 Inti | RODUCTION                                        | 27           |

| 3.2 Spec | CIFICATIONS                                      | 28           |

| 3.3 ARC  | CHITECTURE                                       | 29           |

| 3.3.1    | Analog Multiplexer                               | 30           |

| 3.3.2    | Chopper Modulator and Demodulator                | 31           |

| 3.3.3    | Bias Circuitry                                   | 33           |

| 3.3.4    | Cascode Amplifier                                |              |

| 3.3.5    | Common-Mode Feedback Circuit                     | 37           |

| 3.3.6    | Offset Correction Circuit                        |              |

| 3.3.7    | 1 0                                              |              |

|          | ULATION RESULTS                                  |              |

|          | PLIFIER SYSTEM                                   |              |

|          | FAL RECORDING SITES ON MOSIS CHIPS               |              |

|          | JRAL INPUT PADS                                  |              |

|          | P OVERALL                                        |              |

|          | JRON TRANSISTORS                                 |              |

| 201      | Dungagg Stang                                    | 56           |

| 3.9.   | .2 Packaging and Bonding Problems           | 58 |

|--------|---------------------------------------------|----|

|        | USING COMMERCIAL ELECTRODE ARRAYS           |    |

| 3.11   | TEST BOARDS AND TEST RESULTS                | 60 |

| 3.1.   | 1.1 Testing the chopper-modulated amplifier | 60 |

|        | 1.2 Flicker noise measurements              |    |

| 3.1.   | 1.3 Testing of Neuron-FETs                  | 63 |

|        | 1.4 Test setups for in-vitro testing        |    |

|        | NEUROCHIP TESTING PROBLEMS                  |    |

| 3.12   | 2.1 Introduction                            | 68 |

|        | 2.2 Analysis of the problem                 |    |

|        | Conclusions                                 |    |

| Ref    | ferences                                    |    |

|        | TER IV. CONCLUSIONS AND FUTURE WORK         |    |

| 4.1 Fi | LICKER NOISE REDUCTION – DOES IT MATTER?    | 80 |

| 4.2 C  | IRCUIT ENHANCEMENTS                         | 80 |

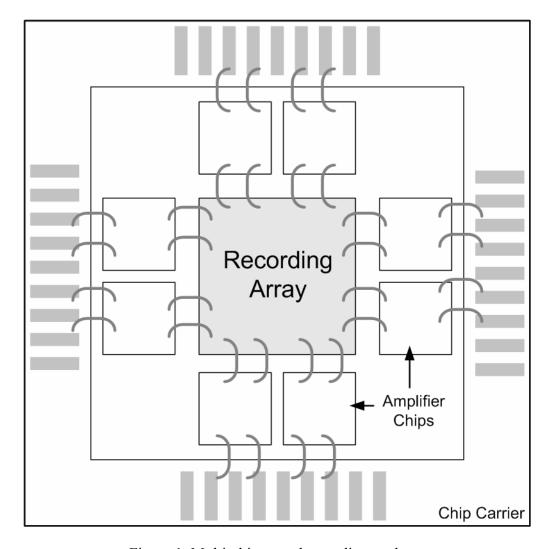

| 4.3 M  | IULTI-CHIP / SINGLE-PACKAGE SOLUTION        |    |

| 4.4 N  | EURON TRANSISTOR                            | 82 |

| 4.5 M  | IOSIS-BASED MICROELECTRODE ARRAYS           | 83 |

|        | ONCLUSIONS                                  |    |

|        | Gerences                                    |    |

# **List of Tables**

| Table 1: Characteristics of the low-pass filter    | 46 |

|----------------------------------------------------|----|

| Table 2: Summary of the results                    |    |

| Table 3: Metal-electrolyte interface common values |    |

# **List of Figures**

# **Chapter II**

| Figure 1. Patch-clamping                                                                                                                                                                                                                                                                                             | 5                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Figure 2. Double Layer                                                                                                                                                                                                                                                                                               | 7                                                              |

| Figure 3. Electrical model of metal-electrode interface                                                                                                                                                                                                                                                              | 8                                                              |

| Figure 4. Neuron Transistor                                                                                                                                                                                                                                                                                          | 9                                                              |

| Figure 5. Circuit model                                                                                                                                                                                                                                                                                              | 10                                                             |

| Figure 6. 2nd generation neuron transistor                                                                                                                                                                                                                                                                           | 11                                                             |

| Figure 7. Synaptically connected neurons                                                                                                                                                                                                                                                                             | 12                                                             |

| Figure 8. Neural network                                                                                                                                                                                                                                                                                             |                                                                |

| Figure 9. Picket fences                                                                                                                                                                                                                                                                                              | 13                                                             |

| Figure 10. Two chip solution                                                                                                                                                                                                                                                                                         | 14                                                             |

| Figure 11. Noise spectrum                                                                                                                                                                                                                                                                                            |                                                                |

| Figure 12: DC Offset                                                                                                                                                                                                                                                                                                 |                                                                |

| Figure 13: Chopper modulation                                                                                                                                                                                                                                                                                        |                                                                |

| Figure 14: Auto-zeroing                                                                                                                                                                                                                                                                                              |                                                                |

| Figure 15: Using dummy switches                                                                                                                                                                                                                                                                                      |                                                                |

| Figure 16: (a) Regular chopper (b) With delayed output modulator                                                                                                                                                                                                                                                     |                                                                |

| Figure 17: Nested-chopper modulation                                                                                                                                                                                                                                                                                 | 24                                                             |

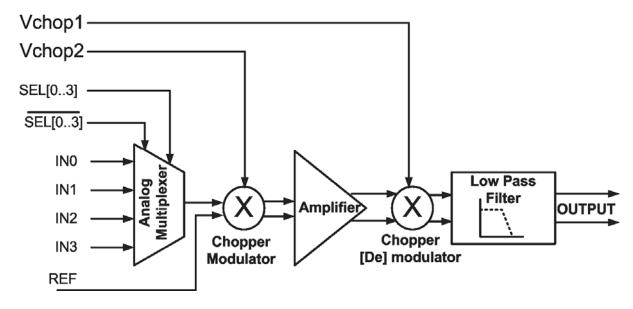

| Figure 1. Toplevel                                                                                                                                                                                                                                                                                                   | 30                                                             |

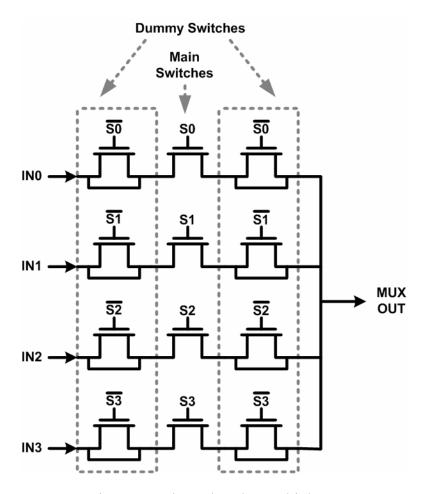

| Figure 2. 4-channel analog multiplexer                                                                                                                                                                                                                                                                               |                                                                |

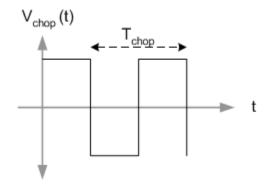

| Figure 3. Chopper Signal                                                                                                                                                                                                                                                                                             |                                                                |

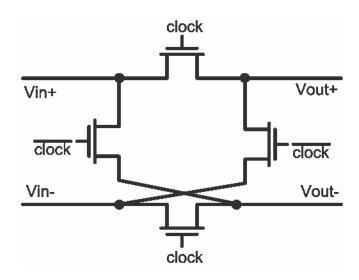

| Figure 4. Chopper modulator/demodulator.                                                                                                                                                                                                                                                                             |                                                                |

| Figure 5. Bias Circuitry                                                                                                                                                                                                                                                                                             |                                                                |

| Figure 6. Cascode amplifier                                                                                                                                                                                                                                                                                          |                                                                |

| Figure 7. CMFB Block Diagram                                                                                                                                                                                                                                                                                         |                                                                |

| Figure 8. Common Mode Feedback circuit                                                                                                                                                                                                                                                                               | 37                                                             |

| E: 0. C. 1.11: 1. 1. C.1. CD (ED.1.                                                                                                                                                                                                                                                                                  | 37<br>38                                                       |

| Figure 9. Stability analysis of the CMFB loop                                                                                                                                                                                                                                                                        | 37<br>38<br>39                                                 |

| Figure 9. Stability analysis of the CMFB loop                                                                                                                                                                                                                                                                        | 37<br>38<br>39<br>40                                           |

|                                                                                                                                                                                                                                                                                                                      |                                                                |

| Figure 10. Offset-cancellation circuit block diagram  Figure 11. Offset correction circuit.  Figure 13. Low Pass Filter.                                                                                                                                                                                             | 37<br>38<br>39<br>40<br>41<br>42                               |

| Figure 10. Offset-cancellation circuit block diagram  Figure 11. Offset correction circuit.  Figure 13. Low Pass Filter.  Figure 14. Linearized transconductance circuit                                                                                                                                             | 37<br>38<br>39<br>40<br>41<br>42<br>44<br>45                   |

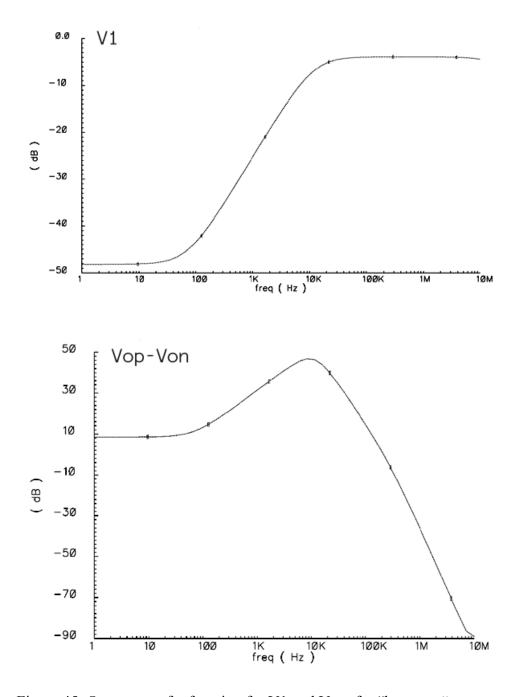

| Figure 10. Offset-cancellation circuit block diagram  Figure 11. Offset correction circuit.  Figure 13. Low Pass Filter  Figure 14. Linearized transconductance circuit  Figure 15. Simulation results                                                                                                               | 37<br>38<br>39<br>40<br>41<br>42<br>44<br>45                   |

| Figure 10. Offset-cancellation circuit block diagram  Figure 11. Offset correction circuit.  Figure 13. Low Pass Filter.  Figure 14. Linearized transconductance circuit.  Figure 15. Simulation results.  Figure 16. Diagram of the manufactured "NeuroChip".                                                       | 37<br>38<br>39<br>40<br>41<br>42<br>44<br>45<br>47             |

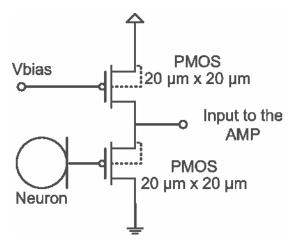

| Figure 10. Offset-cancellation circuit block diagram  Figure 11. Offset correction circuit.  Figure 13. Low Pass Filter  Figure 14. Linearized transconductance circuit  Figure 15. Simulation results  Figure 16. Diagram of the manufactured "NeuroChip"  Figure 17. Front end                                     | 37<br>38<br>39<br>40<br>41<br>42<br>44<br>45<br>47<br>48       |

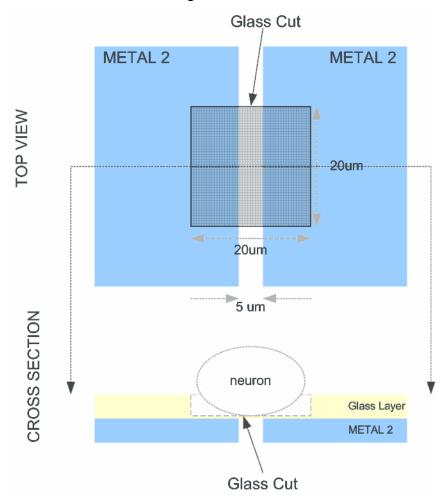

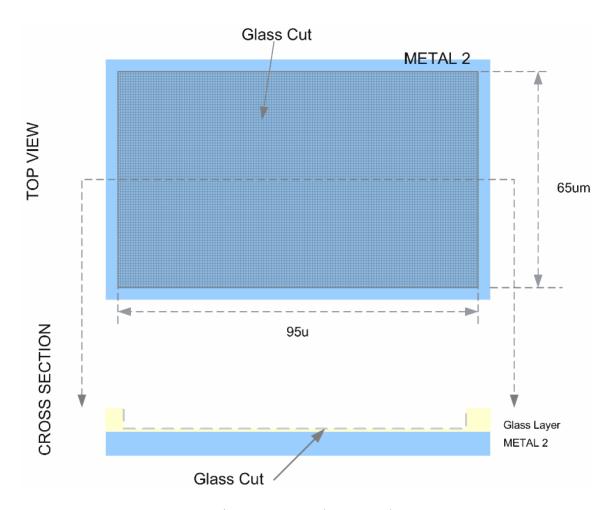

| Figure 10. Offset-cancellation circuit block diagram  Figure 11. Offset correction circuit.  Figure 13. Low Pass Filter.  Figure 14. Linearized transconductance circuit.  Figure 15. Simulation results.  Figure 16. Diagram of the manufactured "NeuroChip"  Figure 17. Front end.  Figure 18. Internal Electrode. | 37<br>38<br>39<br>40<br>41<br>42<br>44<br>45<br>47<br>48<br>49 |

| Figure 10. Offset-cancellation circuit block diagram  Figure 11. Offset correction circuit.  Figure 13. Low Pass Filter  Figure 14. Linearized transconductance circuit  Figure 15. Simulation results  Figure 16. Diagram of the manufactured "NeuroChip"  Figure 17. Front end                                     | 37<br>38<br>39<br>40<br>41<br>42<br>44<br>45<br>47<br>48<br>50 |

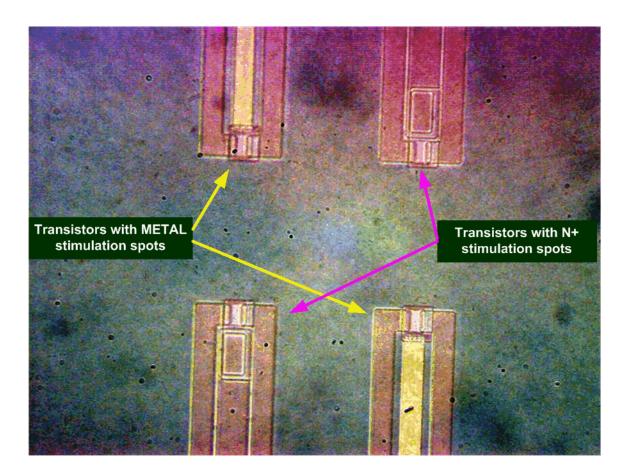

| Figure 21. Encapsulated chip                                                              | . 52  |

|-------------------------------------------------------------------------------------------|-------|

| Figure 22. Neural Input Pads                                                              | . 53  |

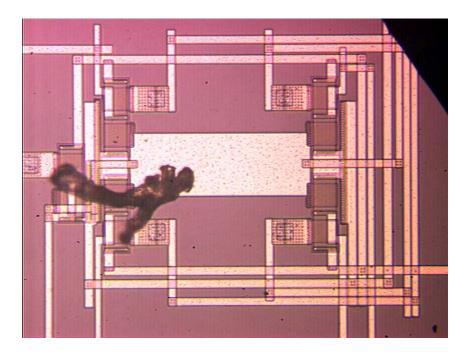

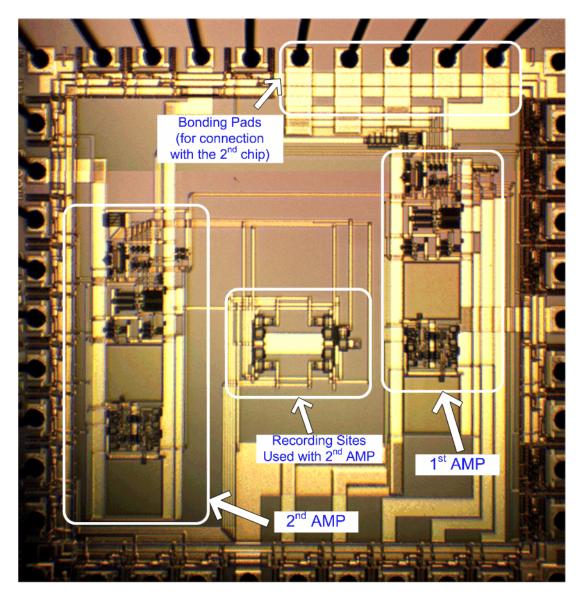

| Figure 23. Picture of the MOSIS chip                                                      | . 54  |

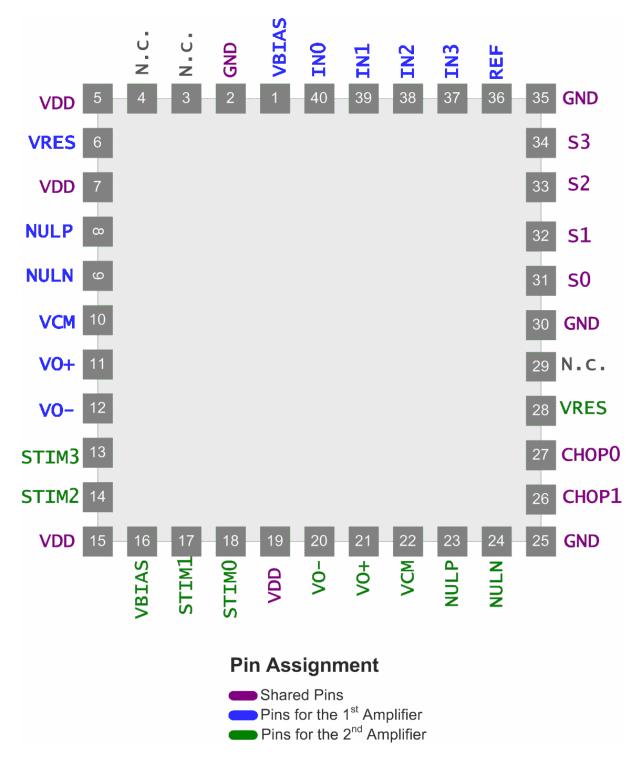

| Figure 24. Pin assignment for the MOSIS chip                                              | . 55  |

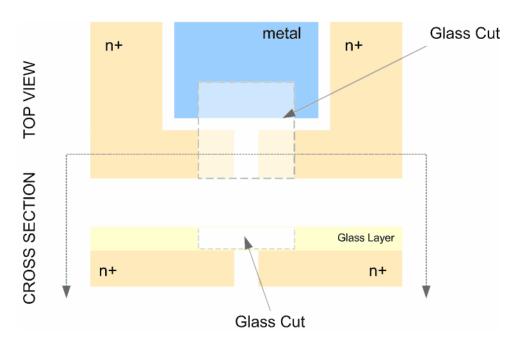

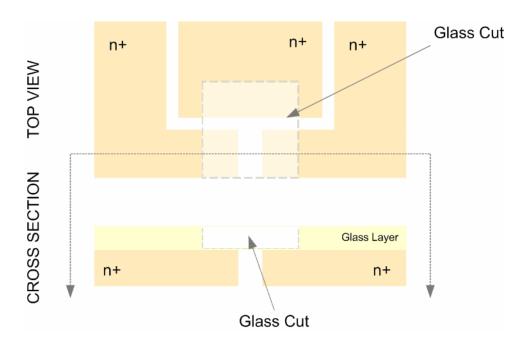

| Figure 25. Neuro-Fet with metal stimulation spots                                         | . 57  |

| Figure 26. Neuro-fet with n+ stimulation spots                                            | . 57  |

| Figure 27. Picture of the Neuron-Fet Devices                                              | . 58  |

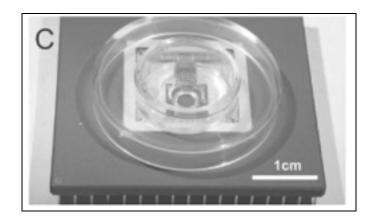

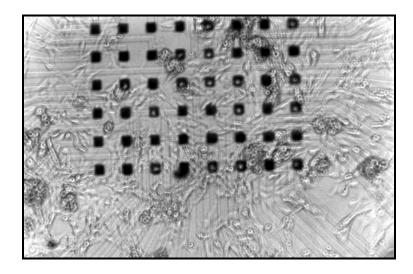

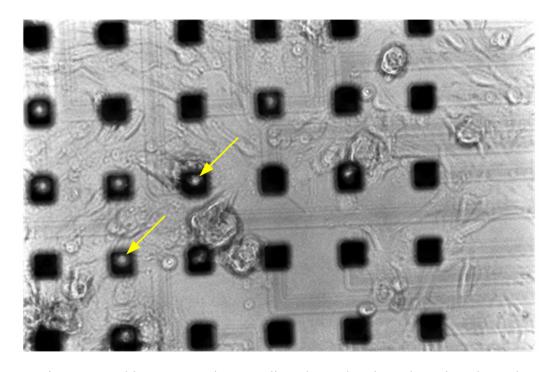

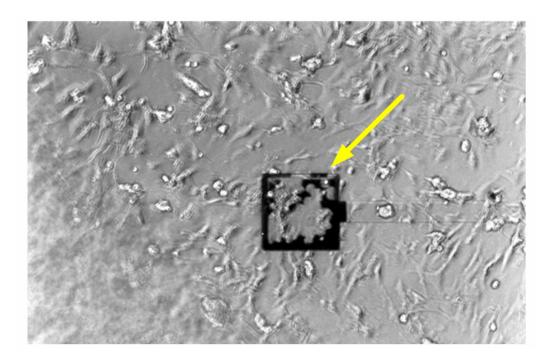

| Figure 29. Chromaffin cells plated on MEA dish                                            |       |

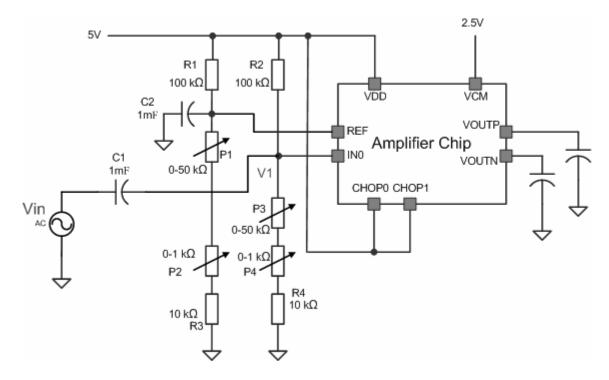

| Figure 30. Test Setup                                                                     |       |

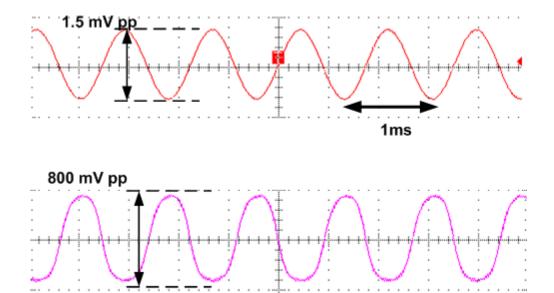

| Figure 31. Amp input & output                                                             | . 61  |

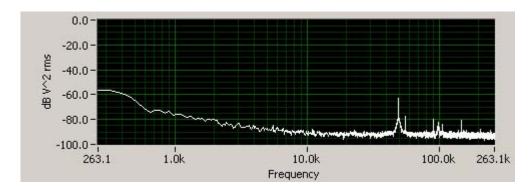

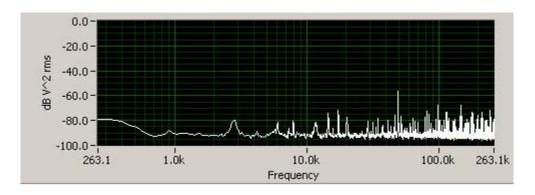

| Figure 32. Spectral analysis of the Neurochip's outputs without chopper modulation. The   |       |

| signal is averaged over 8 samples to reduce the effects of the random noise on the gray   |       |

| Output noise and offset is around -60 dB at 263 Hz. The noise corner is around 10 kF      | łz.   |

|                                                                                           | . 62  |

| Figure 33. Spectral analysis of the Neurochip's outputs with chopper modulation. This tes |       |

| also utilized averaging over 8 samples. The low frequency output noise is reduced to      |       |

| dB at 263 Hz.                                                                             |       |

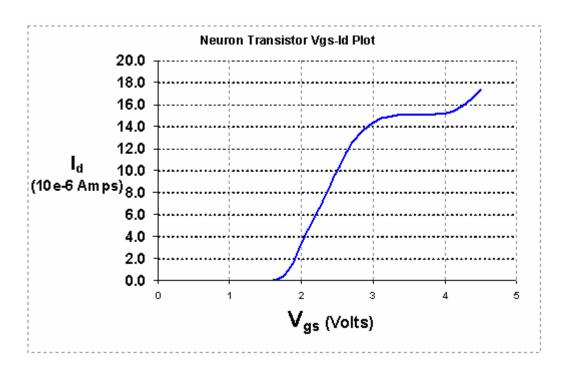

| Figure 34. Neuron transistor VGS - ID curve (VDS=2.5 V)                                   |       |

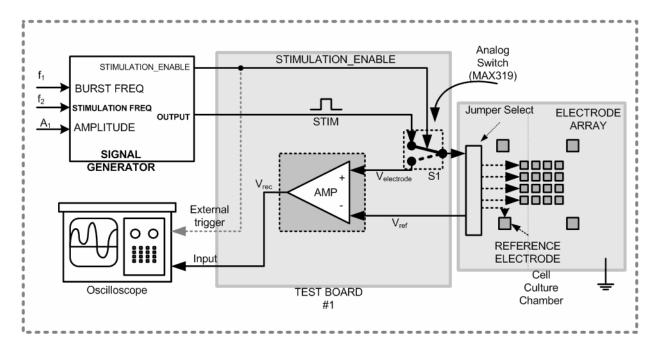

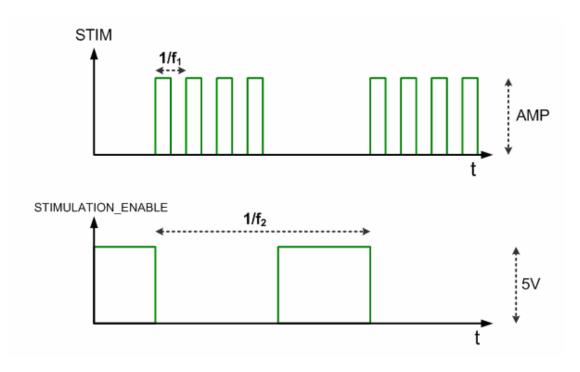

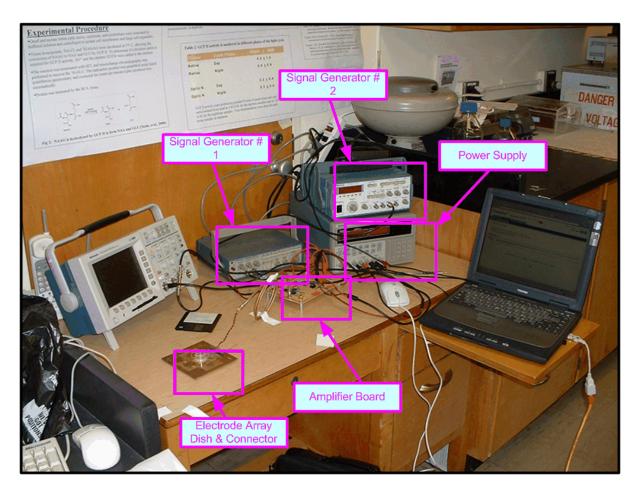

| Figure 35. Test Board # 1                                                                 |       |

| Figure 36. Signals for the Test Board # 1                                                 |       |

| Figure 37. Setup for Test Board # 1                                                       |       |

| Figure 38. Test Board # 2                                                                 |       |

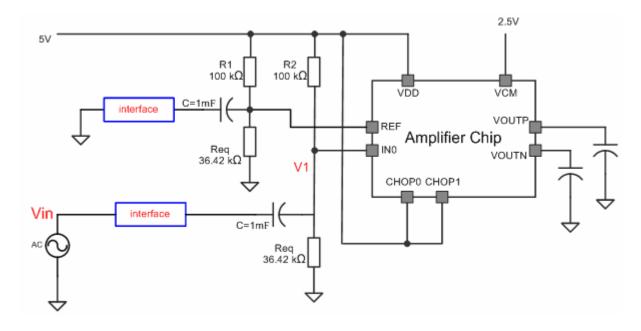

| Figure 39: Model of a voltage source and an amplifier                                     |       |

| Figure 40: White spots on the recording electrodes show the stripped metal                |       |

| Figure 41: A reference electrode almost completely stripped off of its metal              |       |

| Figure 42: Metal-Electrolyte Interface                                                    |       |

| Fig 43: Setup with interface                                                              |       |

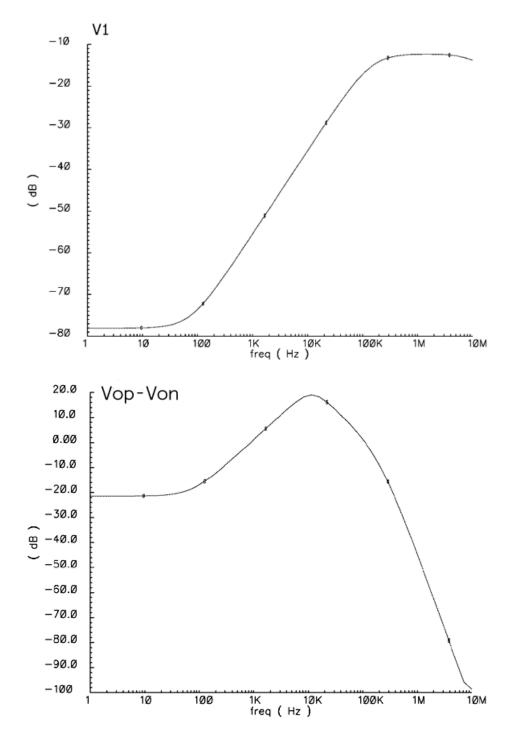

| Figure 44: Output transfer function for V1 and Vout for "worst case" parameters           |       |

| Figure 45: Output transfer function for V1 and Vout for "best case" parameters            | . /// |

|                                                                                           |       |

|                                                                                           |       |

| Chapter IV                                                                                |       |

|                                                                                           |       |

|                                                                                           |       |

| Figure 1. Multi-chip neural recording package                                             | . 82  |

# **Chapter I. Introduction**

Since the beginning of the twentieth century, biologists have been trying to characterize the electrical activity in animal cells that have excitable membranes. The reason that this is important is because it helps scientists understand how nerves work, how the brain works, and how the brain controls bodily functions. It also helps us to diagnose and treat nervous system disorders.

A powerful approach to the characterization of cellular electrical activity is electrical recording from cells or living tissues. Depending on the research goal, the scientist may decide to perform neural recording on a complete live animal (*in vivo*), a tissue sample (*in vitro*), or extracted cells (*in vitro*). Neural recording *in vivo* provides the scientist with the ability to study nervous system diseases, determine how nerves and muscles work, and evaluate an animal's responses to external stimuli. Use of tissue samples simplifies the recording and analysis of the subject. A typical tissue sample would be a slice of brain, a portion of the nervous system, or a slice of the retina. Without the rest of the animal present it is possible to stimulate the tissue electrically or chemically and determine how it reacts. This can be an important tool in the creation of electrical models of the tissue. For example, Hodgkin and Huxley used neural recording of the giant axon of a squid to create models of excitable membranes. Neural recording of extracted cells provides the ability to determine how a cell behaves when it is separated from its host. One common application of the neural recording of extracted cells is to gather information about the characteristics of ion channels.

The object of the research described in this dissertation is to provide improvements in the methods used for performing neural recording. Neural recording is a form of measurement, and all measurement systems contain imperfections. By minimizing these imperfections we can maximize the quality of the results. The electrical information measured by neural recording systems consists mainly of low-frequency signals, and the amplifiers used are generally MOSFET-based. MOSFETS are well-known to be prodigious producers of 1/f, or

flicker noise, a noise process that produces increasing noise as the frequency is reduced. In the past, to mitigate this problem designers have employed very large transistors --- which reduces the flicker noise generated by the transistors --- or employed filtering. Large transistors take up a lot of space which limits the number of channels that can be simultaneously recorded. Filtering loses information in addition to taking up extra space. Instead, the approach proposed here is to use the well-known chopper modulation technique to reduce the effects of low-frequency noise generated by the input stages of the amplifiers. This provides a significant reduction in the required area and therefore allows more channels to be simultaneously recorded.

#### The novel contributions of this work include:

- demonstration that chopper modulation does reduce flicker noise in neural recording systems, resulting in smaller layouts and therefore greater channel density

- ASIC design of amplifier system

- design of a gate-metal-free MOSFET with stimulation electrodes

- design of electrodes using a commercial manufacturing process (MOSIS)

In the next chapter background information is provided on the most common cultured-cell recording methods, information about the associated electrical measurement systems and low-frequency noise issues. In the third chapter, some methods to combat the noise problem will be provided. I provide a practical implementation of a neural recording system that uses the suggested chopper modulation technique and the results that show that it provides the predicted benefits. I end with a discussion of the problems encountered implementing our techniques, and provide solutions for these problems.

# **Chapter II. Literature Review**

#### 2.1 Introduction

The focus of this thesis is *in vitro* electrical recording of cultured cells. In this chapter some background for several recording methods will be presented. These methods include those that involve extracellular electrodes, impaling intracellular microelectrodes, patch clamping, planar microelectrode array recording and neuron-transistor recording.

Neural signals in general have a very small bandwidth, usually no more than a few kHz, so low frequency noise can be a very important consideration for recording quality. Different types of low frequency noise sources will be presented. Afterwards, some methods of removing this unwanted noise will be studied.

The noise removal techniques themselves sometimes create additional problems. Those issues will also be reviewed and some solutions will be presented.

# 2.2 Cultured Cell Recording Methods

Researchers began to culture tissue and cells outside of the body in the beginning of the 20<sup>th</sup> century [1]. The introduction of the model of an excitable membrane by Hodgkin and Huxley [2] — for which they were awarded a Nobel Prize — was a very important technical advance. It made it easier for researchers to study and understand the excitable membranes of cells and recording electrical activity from them. In this chapter, several ways to record from cells *in vitro* will be examined and categorized. The methods introduced here apply only to recordings of isolated nerves, cultured cells and tissue-slices.

### 2.2.1 Extracellular and Intracellular Electrode Recordings

As soon as researchers realized that nerve cells exhibit electrical activity, finding ways to measure these signals became very important. In the case of cultured nerve cells or tissue slices, using electrodes with very small tips became a necessity for confining the measurement location to a small area. Indeed the term "microelectrode" emphasizes the fact that the diameter of the tips of these electrodes is on the order of microns.

In extracellular recording, electrodes are placed in close proximity to a single cell or a group of cells without disturbing any cell membrane. In intracellular recording, sharp microelectrodes are used to punch through the membrane of a cell. Microelectrodes can be made of metal, or they might come in the form of a glass pipette [3] with a very small opening at the end of the tip. Glass microelectrodes are filled with a saline conducting KCl solution that is compatible with the intracellular fluid.

## 2.2.2 The Patch-Clamp Method

Extracellular and intracellular recording are limited because they are inefficient or require large cells or membrane areas. The patch-clamp method, which was first introduced by Neher and Sakmann in 1976 [4], works for fairly small cells; even for a single ion channel. The patch-clamp technique earned Neher and Sakmann the Nobel Prize in 1992.

The patch-clamp technique essentially consists of patching the tip of an electrolyte-filled pipette to the membrane of a cell, clamping it to a preset voltage, and measuring the resulting current.

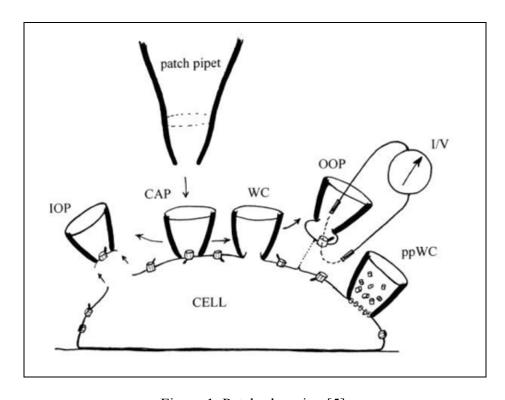

There are five different configurations, which are called "whole-cell," "cell-attached," "inside-out," "outside-out," and "permeabilized-patch whole-cell" recordings, which are shown in Figure 1. The cell-attached method is the least invasive configuration of all. It involves a mild suction of a small patch of membrane that contains a single or a small

number of ion channels into the pipette tip, which seals the membrane completely. During an ion flux, almost all of the ions flowing through the channel will move through the pipette's tip. If the suction is strong enough, the membrane will break and the tip of the pipette will become continuous with the whole membrane, which results in what is called a whole-cell patch. If a piece of the membrane is detached from the whole cell and the inner face of the detached portion is exposed to a solution, it is now an inside-out patch. The outside-out configuration is obtained by slowly pulling the membrane away from both sides of a whole-cell configured patch so that the external faces of the membrane are facing the solution [5].

The permeabilized-patch whole-cell configuration results when the membrane patch is made permeable by adding antibiotics to the pipette solution that create artificial ion channels while the patch is in the cell-attached configuration [6].

Figure 1. Patch-clamping [5].

#### 2.2.3 Planar Microelectrodes

Although using extracellular electrodes are commonly used to record from populations of excitable cells and intracellular microelectrodes or the patch-clamp method to record from single neurons, there are many disadvantages to these techniques that lead researchers to look for non-invasive solutions. For example, the patch-clamp technique cannot be used for long term recordings, it is not easily used *in vivo*, and only a single cell can be observed at any given time.

In 1972, Thomas, et. al. introduced [7] the concept of planar microelectrodes. A planar microelectrode is a thin-film deposit of gold or platinum on a glass substrate. The planar microelectrode is enclosed in a Petri dish or a glass chamber of some sort. The container is filled with an electrolyte, and the sample is then placed upon the electrode. Generally, planar microelectrodes are implemented in arrays. Planar microelectrodes are non-invasive, can accommodate large numbers of cells, and are simple to implement.

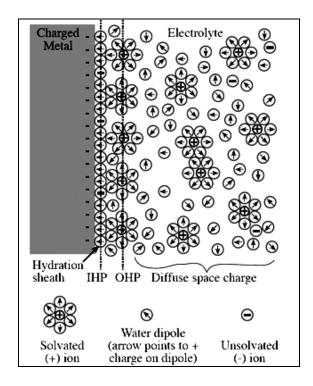

A metal electrode is not generally inert to the electrolyte medium into which it is immersed. There is generally an electrochemical reaction between the electrode and electrolyte [10] [8] [9]. When an unbiased metal item is dipped into an electrolyte, several chemical reactions start at the interface of the metal and the liquid. One of these reactions is *oxidation*, where metal *donors* give out an electron and an *acceptor*, which are metal ions. This reaction is shown in (1). In this equation, donor A gives out an acceptor, A and an electron, e.

$$A \to A^+ + e^- \tag{1}$$

Donated electrons will accumulate at the edge of the metal, because electrons repel each other and are attracted to the metal surface. The ions in the electrolyte will align themselves by forming a double layer called as *inner Helmholtz plane (IHP)* and *outer Helmholtz plane (OHP)* as seen in Figure 2. The space charge layer formed in this equilibrium is usually

modeled as a capacitance known as the "interfacial capacitance." There is equal current flow in both directions which results in zero net current.

Figure 2. Double Layer [10]

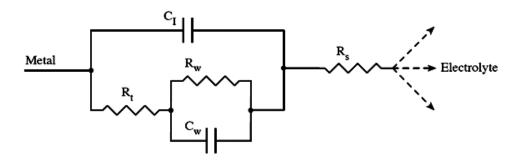

If a DC potential is applied across the interface, there will be a current flow across the plate [10] [11] so we need to add a resistive path to our model. If the potential difference is relatively small, the current flow will be linearly related to the voltage. The equivalent resistance is called "charge transfer resistance."

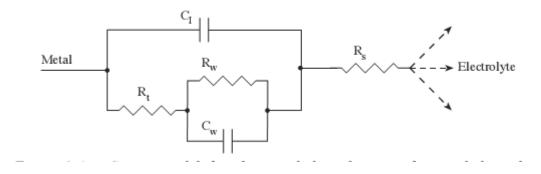

There is also some impedance effects that is caused by diffusion. This effect has been modeled by Warburg [11] using a resistor and capacitor in parallel (shown as  $R_w$  and  $C_w$  in Figure 3). He also suggested that this impedance must be in series with the charge transfer resistance [11].

Spreading resistance, which is shown as  $R_s$  in Figure 3, is modeled for the current that spread outward from the electrode to the solution it is in. There are several methods proposed to calculate this resistance [11]. In general terms, the calculation depends on the shape of the electrode and conductivity of the electrolyte.

So, the model for the electrode-electrolyte interface is given in Figure 3.

Figure 3. Electrical model of metal-electrode interface [11]

Planar microelectrode arrays have been used extensively by many scientists for all kinds of neural recording experiments. In [8], Pine et al used microelectrode arrays to record signals from rat neurons. In [9], gold conductor electrodes were used to record signals from mammalian spinal cord neurons. In [12], a method for manufacturing gold based platinized microelectrodes has been presented. In [13] an electrode array was embedded with a Petri dish, which helped to make long time chronic recordings. The planar electrode arrays were not exclusive to *in vitro* recordings. It was also used to make *in vivo* recordings. In [14], a 3-dimensional recording array was manufactured. Sharp extracellular penetrating electrodes, each of which has a number of thin film microelectrode on them, were placed on a grid formation to obtain a 3D recording of the subject's brain activity. A similar approach were used in [15].

#### 2.2.4 Neuron Transistor

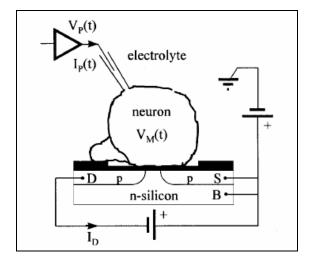

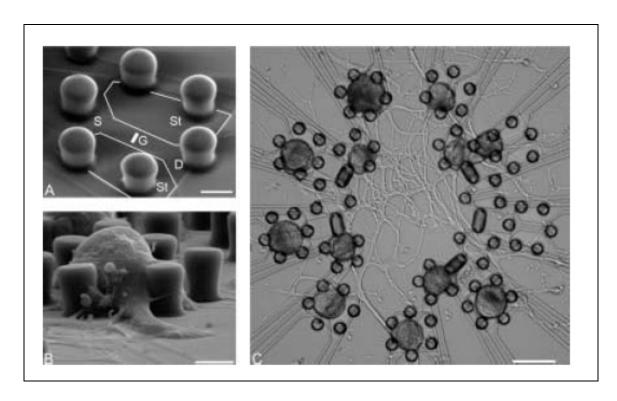

The ability to couple neurons to transistors was first demonstrated by a German group supervised by Fromherz [16]. Several aspects of this concept have been investigated and will be discussed here.

The most important aspect is the use of gate-metal-free MOS transistors as recording devices. The neurons are placed on top of the thin oxide of a MOSFET as shown in Figure 4, which depicts a first-generation neuron transistor implementation. The neuron is stimulated using the patch-clamp technique via a pipette as shown in the top left section of the figure. The voltage changes on the neuron's membrane modulate the transistor, resulting in a changing current. The silica surface of the metal-free gate provides an inert interface for the neuron and the underlying medium.

Figure 4. Neuron Transistor [11]

The MOSFET is biased with  $V_{sd} > |V_{gs}-V_{th}|$  so that it is in the saturation region.  $V_s=V_b=VDD$ , and  $VDD>>V_{sd}$ . This means this circuit will have a current flow even when there is no activity on the neuron's membrane.

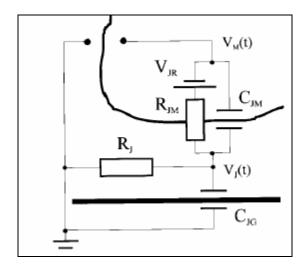

This system has been modeled based on Hodgkin-Huxley equations and basic membraneoxide coupling equations; the resulting circuit model is shown in Figure 5.

Figure 5. Circuit model.

In this model,  $R_j$  is the sealing resistance,  $C_{jm}$  is the membrane capacitance,  $C_{jg}$  is the oxide capacitance,  $V_m(t)$  is the inner membrane potential, and  $V_j(t)$  is the outer membrane potential.  $V_{jr}$ ,  $R_{jm}$  and  $C_{jm}$  are defined by the Hodgkin and Huxley equations.

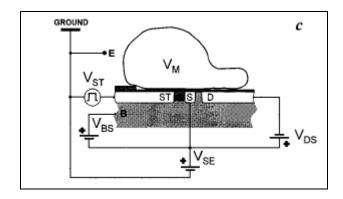

Second-generation implementations of the neuron transistor differ from first-generation implementations in that they introduce a "stimulation spot" [19] which makes the system completely non-invasive. The stimulation spot is p-doped silicon covered with a thin layer of SiO<sub>2</sub>. Figure 6 depicts this configuration.

Voltage pulses are used to elicit an action potential on the neuron which can be recorded by the neuron transistor the same way it was done in first-generation implementations.

Figure 6. 2nd generation neuron transistor

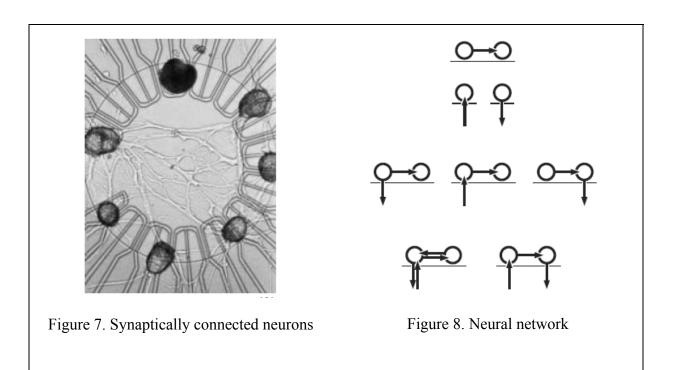

incubation in an appropriate medium and growth factors. In [20], Jenkner chose the pedal ganglia of *Lymnaea Stagnalis* for their neural cells and conditioned the medium with brain tissue of the same species of snail. The brain tissue created an environment that helped neuron outgrowth.

Next, he put multiple neurons on top of neuron transistors. Some of these neurons formed synaptic connections as seen in Figure 7. The system was used to stimulate a neuron, which generated an action potential. Then this activity propagated to the synaptically connected second neuron, which also elicited an action potential. This activity was recorded by the neuron transistor. This was a demonstration of  $chip \rightarrow cell \rightarrow cell \rightarrow chip$  communication. This shows that two-way communication can also be achieved by recording a cell's activity after it is stimulated. This hybrid neuro-electronic unit practically implemented all of the networks shown in Figure 8.

One of the problems with these systems is that neuron cell bodies may not stay at the locations at which they are initially placed. One possible reason for this is that the medium may exert forces on the neuron cell bodies that cause them to move about. The most common method that is used to avoid this problem is to coat the chips with adhesion factors. Poly-1-lysine is one of the most used materials for cell adhesion. But, even after using poly-1-lysine neurons will sometimes still move around. Fromherz et. al, found a good trick to overcome this problem [20] they used so-called "picket fences" made out of polyimide to immobilize the somata of *L. Stagnalis* neurons. These obstacles, as shown in Figure 9, were an effective way to keep the neurons on the recording site.

Figure 9. Picket fences [20]

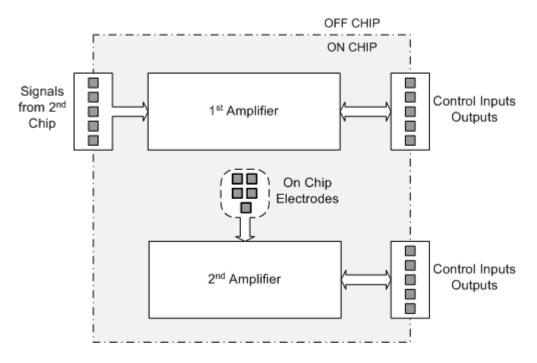

Fromherz et. al. also advanced the research in the area of neuron transistors in several other ways. In earlier work, the electronics were separated from the recording unit. In 2002 Bonifazi et. al. designed a system where the electronics were adjacent to the recording unit. They designed two chips, one with the neuron-transistors and another chip with a preamplifier and some detection circuitry [21] These two chips were bonded in the same package and inter-chip connections were made directly. This system is shown in Figure 11.

Figure 10. Two chip solution [21]

### 2.3 Low frequency noise sources

The neural signals usually have a bandwidth between several hertz to around 5 kHz. In this frequency range, some problems that normally would not make too much difference in high frequency circuits start to become very important. In this section, these noise sources will be identified, some of the methods of low frequency noise reduction techniques will be presented and some implementation issues will be addressed.

#### 2.4 Flicker Noise and Thermal Noise

Flicker noise is a significant noise source for low-frequency applications. It originates in the amplifier. The most significant contributors of this type of noise are the input transistors, because the noise generated by them will be directly added to the signal and amplified by the following stages.

Although there has been extensive research about this topic, it is not entirely known how flicker noise is generated. There are two main theories about the origins of flicker noise. The first theory finds the "random fluctuations in the number of carriers near the Si-SiO2 interface" as a cause of this noise [22]. The second theory accredits mobility fluctuations as a

cause of flicker noise [22]. In general, the following equation is used to quantify flicker noise.

$$v_{n}^{2}(f) = \frac{K}{c_{ox}} \frac{1}{WL} \frac{1}{f^{c}}$$

(2)

The exponent c is usually between 0.7 and 1.2. K is a process-dependent constant and it has been shown to be around  $2x10^{-25}$ . In this equation f is the frequency,  $c_{ox}$  is the oxide capacitance per unit, W is the channel width of the transistor and L is the channel length of the transistor. The exact values of K and c are not known until after testing the device. In most cases, c is considered to be 1, which makes the noise proportional to 1/f. For this reason, flicker noise is also called "1/f noise". The implication of (2) is that flicker noise is dominant at low frequencies and asymptotically approaches infinity as the frequency approaches zero. This means that when we are looking at a signal at very low frequencies and if we observe the signal long enough, the noise may take on very high values. But practical experiments show that 1/f noise does not actually approach infinity [23].

Thermal noise is caused by random fluctuations in the energy of the conducting electrons in any resistive element, including transistors. It is formulated as the following.

$$V_n = \sqrt{4kTR} \tag{3}$$

Where k is Boltzmann's constant, T is the temperature and R is the resistance of the resistive element.

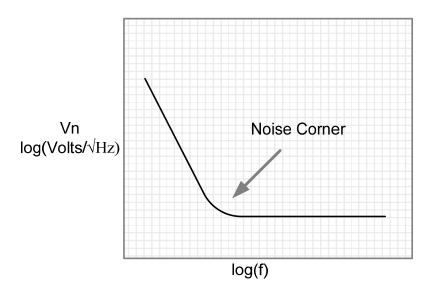

At low frequencies flicker noise dominates, and at higher frequencies thermal noise dominates. Thermal noise has a uniform distribution and both thermal and flicker noises can be added together as seen in Figure 11. The frequency at which these two waveforms intersect is called the *1/f noise corner*.

Figure 11. Noise spectrum

## 2.4.1 DC Offset

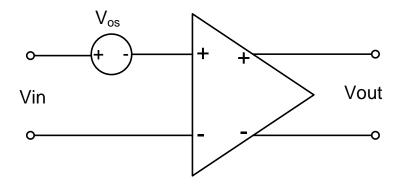

Ideally, the differential outputs of an amplifier should be zero when its differential inputs is also zero, but generally there is an offset voltage between the outputs of the amplifier. This DC offset may be a result of the improper design of the circuit but usually it is caused by mismatches in the circuit. The DC offset seen at the output of an amplifier will decrease the dynamic range of the circuit. This offset voltage can usually be compensated by introducing an offset at the input. This offset is referred to as the amplifier's *input offset voltage*. Figure 12 shows this voltage.

Figure 12: DC Offset

#### 2.4.2 Other noise sources

There are some other noise sources that are specific to the materials chosen and manufacturing processes. In the case of metal electrodes, the resistive elements between metal-electrolyte interfaces create additional thermal noise which will degrade system quality. This noise, especially that created by the spreading resistance (*Rs*), limits the size and the shape of the electrode, adding another constraint to the recording system design [24] [25]. Another noise source is the *random baseline drift*, which is reported to be very slow [26]. and therefore relevant. This drift is usually around 100mV at a frequency of less than a couple of hertz [26]. Designers usually remove this noise with a high-pass filter which has a low cutoff frequency. It is reported that this noise only applies to metal electrodes [24] and doesn't appear on neuron-transistor based systems.

Another noise source that limits the system's performance is EMI or Electro-Magnetic Interference. Any wire that passes a current can be a source of EMI. One of the problematic manifestations of EMI is the 60 Hz noise that is caused by electric lines. Many designers add a notch filter to attenuate this type of noise.

Crosstalk between adjacent lines that connect to recording sites can cause problems. If a large signal is passed through one of these wires, artifacts may appear on the other line. This

is often a problem when one of the lines connects to a stimulation spot while the other carries a recording signal.

## 2.5 Noise Cancellation Techniques

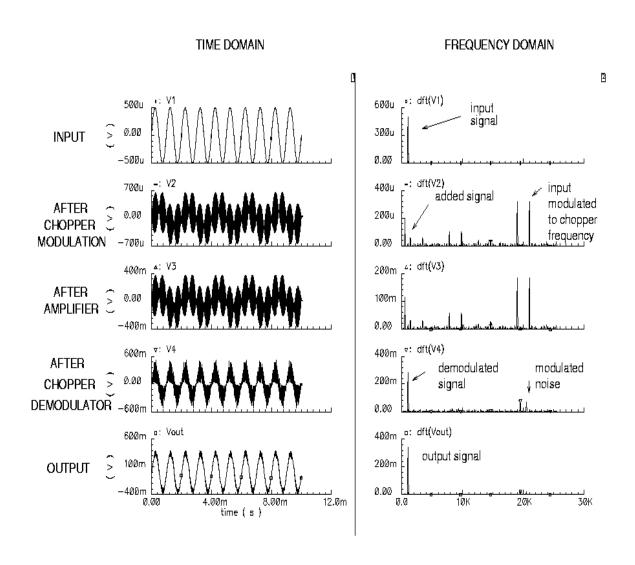

# 2.5.1 Chopper Modulation

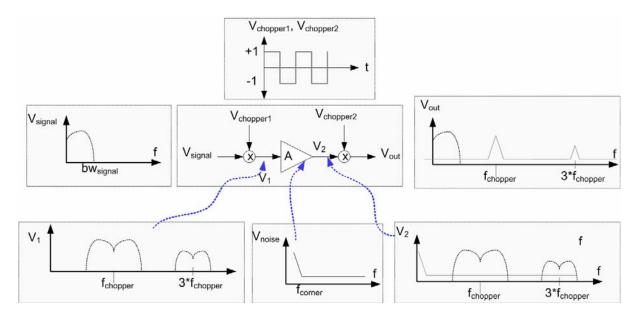

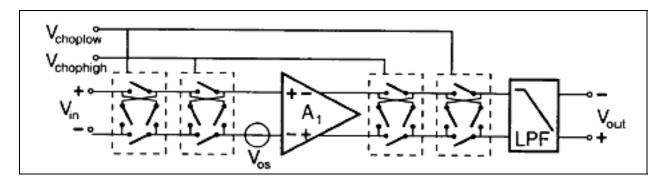

The chopper technique is used to reduce the effects of flicker noise and DC offset in amplification systems. This method does not decrease either types of noise; it simply isolates the noise from the signal in the frequency domain so that the noise can be easily removed without affecting the signal.

In this technique, as seen in Figure 13, the input signal is converted to higher frequencies, specifically the odd harmonics of the chopper frequency, where the flicker noise has an insignificant value. The converted signal is amplified and afterwards a second chopper modulator brings the signal back to its original band. The result is that the amplified signal does not contain a significant flicker noise component.

Figure 13: Chopper modulation

If the amplifier has an infinite bandwidth, the amplified signal can be recovered in its full strength since demodulation, which in this case is exactly the same as modulation, will collect the signal from all of the harmonics it is converted to. However, all amplifiers have a limited bandwidth so complete recovery is not possible [21]. As an example, if a signal with an amplitude of  $V_0$  is used with an amplifier which has bandwidth of  $2*f_{chop}$ , where  $f_{chop}$  is the chopper frequency, and a gain of G, the recovered signal's amplitude would be  $0.8*G*V_0$  [27]. The chopper frequency, amplifier bandwidth or signal bandwidth can be chosen as seen in (4), provided that they can be changed by the designer. This equation assumes that the signal bandwidth is  $BW_{signal}$ , amplifier bandwidth is  $BW_{amp}$  and the chopper modulator is a square wave signal with a frequency  $f_{chop}$ . The noise corner frequency is  $f_{corner}$ .

$$f_{corner} + BW_{signal} < f_{chop} < BW_{amp} - BW_{signal}$$

(4)

This equation implies that the smallest value of  $f_{chop}$  should at least be able to separate the flicker noise from the signal, and the highest value should not push the signals main harmonic out of the amplifier's passband.

# 2.5.2 Auto-zeroing

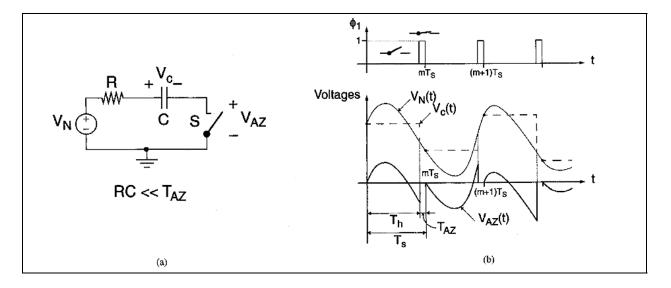

Consider the definition of the DC offset, which was given in the previous pages. Auto-zeroing is essentially subtracting the unwanted offset voltage from the signal, therefore getting an offset-free output. Auto-zeroing consists of two periods: a "sampling phase" and an "offset-free signal" phase. In the sampling phase the offset is sampled and stored and in the offset-free signal phase this stored quantity is subtracted from the signal, which results in a noise-free output [27]. The basic operation is shown in Figure 14.

Figure 14: Auto-zeroing [27].

The input signal to an amplifier is assumed to be changing over time *faster* than the very low frequency signals. So, the capacitor shown in the figure will store the slowly changing signal during the sampling phase, and subtract it from the input signal during the offset-free signal phase.

Auto-zeroing is a sampling technique. One of the drawbacks of this technique is that white noise will be aliased to the baseband, thereby increasing the noise floor of the system.

#### 2.6 Implementation Problems and Solutions

### 2.6.1 Clock Feedthrough and Channel Charge Injection

Every time a MOS switch is turned off, some fraction of the charge that is stored in its channel is injected into the line. These unwanted current spikes will be amplified and low pass filtered by the amplifier and low pass filter, if there is one. This results in a DC offset at the amplifier's output, which is called *residual offset*. Here an important trade-off comes into effect. If the main amplifier's bandwidth is much larger than the chopper frequency, it will result in an increase in the gain as mentioned in previous chapters. However, this will also cause the residual offset voltage to increase because more spectral components of the spikes will be added to the signal and amplified. When choosing amplifier's bandwidth, this trade-off must be taken into account.

One of the important properties of these spikes is that they have relatively low time constant compared to the period of the chopper clock. Therefore much of the energy of the spikes is located at higher frequencies [27]. That being the case, in [27]; the residual offset voltage is quantified in (1) in which  $\tau$  is the time constant of the spike and  $V_{spike}$  is the amplitude of the spike.

$$V_{os} = \frac{2\tau}{T} \times V_{spike} \tag{5}$$

The previous equation assumes that the amplifier has infinite bandwidth. By making the amplifier's bandwidth equal to twice the chopper frequency, the residual offset will reduce to

$$V_{os} = \left(\frac{2\tau}{T}\right)^2 \times V_{spike} \tag{6}$$

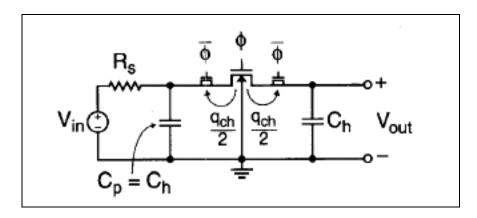

So, even without applying any techniques, the residual offset can be reduced to a very low level. The residual offset can be further reduced using some layout techniques [21], as well as some circuit techniques. One way to reduce this injected noise is to use half-sized dummy transistors as seen in Figure 15. The built up charge on the switch will equally split between source and drain and be compensated by these dummy switches. However, this requires that either the input capacitance (Cp) is equal to output capacitance (Ch), or the chopper clock's transition time is very short [27].

Figure 15: Using dummy switches [27]

Another way of reducing this noise is making the input capacitance much larger than the output capacitance, so that most of the charge is directed to the input capacitance. Furthermore, using a differential configuration will also help to reduce this offset [27].

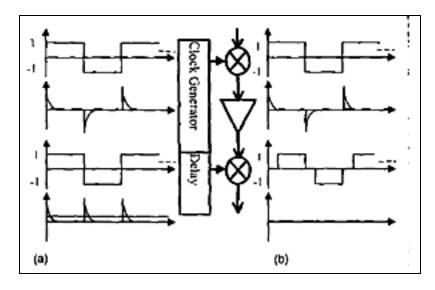

In chopper modulation, the residual offset is directly added to the signal because the chopper demodulator will bring this offset back to the baseband. One of the ways to prevent this noise from being added to the signal is to use a small delay between the modulator's and demodulator's chopper signal, as seen in Figure 16 [28].

Figure 16: (a) Regular chopper (b) With delayed output modulator [28]

This gap, compared to the chopper period, will be very small thus it will not effect the circuit's operation. During this time, the charge, which would normally cause a residual offset, will decay and a clean signal is passed to the following stages.

Another way of dealing with this problem is proposed in [29]. This idea is depicted in Figure 17. In this technique, another chopper pair, operating at much lower frequencies than the first chopper pair, is included in the circuit. The spikes, which were originally caused by the first chopper modulator, will be inverted by the second chopper modulator, resulting in zero offset. The outer pair will still introduce an offset, but since they operate at much lower frequencies, it will be much lower than that of the version without the second pair. Using this technique, 100 nV offset has been achieved by the authors.

Figure 17: Nested-chopper modulation [29]

#### 2.7 Conclusions

In this literature review, we presented some of the methods that are used to interface electronics with living organisms, specifically cultured cells. We presented the patch clamp technique, metal electrodes and neuron transistors and explained some of the aspects of each technique. We also presented noise sources that will interfere with the neural signals, and some possible solutions and ways to avoid further problems.

#### References

- [1] R. G. Harrison, "Observations on the living developing nerve fiber." Proceedings of the Society for Experimental Biology and Medicine, 1907, 4: 140-143.

- [2] A. L. Hodgkin and A. F. Huxley, "A quantitative description of membrane current and its application to conduction and excitation in nerve," *J.Physiol.*, vol. 117, pp. 500-544, Aug. 1952.

- [3] J. Halliwell, M. Whitaker and D. Ogden, "Using microelectrodes" in *Microelectrode techniques, The Plymouth workshop handbook.* 2nd Edition. Edited by D.C. Ogden. Company of Biologists, Cambridge, UK. 1994.

- [4] E. Neher and B. Sakmann, "Single-channel currents recorded from membrane of denervated frog muscle fibres," *Nature*, vol. 260, pp. 799-802, Apr 29. 1976.

- [5] D. Ypey and L. DeFelice, "The patch-clamp technique: theoretical and practical introduction using simple electrical equivalent circuits," *Biophys. J. (Annual Meeting Abstracts)*, vol. 80, pp. 244e-245, January 1. 2001.

- [6] R. Horn, and A. Marty, "Muscarinic activation of ionic currents measured by a new whole-cell recording method" *J. Gen. Physiol.* 1992: 145-159.

- [7] C.A. Thomas Jr, P.A. Springer, G.E. Loeb, Y. Berwald-Netter and L.M. Okun, "A miniature microelectrode array to monitor the bioelectric activity of cultured cells," *Exp.Cell Res.*, vol. 74, pp. 61-66, Sep. 1972.

- [8] J. Pine, "Recording action potentials from cultured neurons with extracellular microcircuit electrodes," *J.Neurosci.Methods*, vol. 2, pp. 19-31, Feb. 1980.

- [9] G.W. Gross, A.N. Williams and J.H. Lucas, "Recording of spontaneous activity with photoetched microelectrode surfaces from mouse spinal neurons in culture," *J.Neurosci.Methods*, vol. 5, pp. 13-22, Jan. 1982.

- [10] D.A. Borkholder and Stanford University. Dept. of Electrical Engineering, "Cell based biosensors using microelectrodes", 1998, pp. 229.

- [11] G. T. A. Kovacs, "Introduction to the theory, design and modeling of thin-film microelectrodes for neural interfaces", *Enabling Technologies for Cultured Neural Networks*, Edited by D.A. Stenger, T.M. McKenna, Academic Press, London, pp 121-165, 1994

- [12] L.J. Breckenridge, R.J. Wilson, P. Connolly, A.S. Curtis, J.A. Dow, S.E. Blackshaw and C.D. Wilkinson, "Advantages of using microfabricated extracellular electrodes for in vitro neuronal recording," J.Neurosci.Res., vol. 42, pp. 266-276, Oct 1. 1995.

- [13] W.G. Regehr, J. Pine, C.S. Cohan, M.D. Mischke and D.W. Tank, "Sealing cultured invertebrate neurons to embedded dish electrodes facilitates long-term stimulation and recording," J.Neurosci.Methods, vol. 30, pp. 91-106, Nov. 1989.

- [14] Q. Bai; K. D. Wise; D.J. Anderson, "A high-yield microassembly structure for three-dimensional microelectrode arrays," *Biomedical Engineering, IEEE Transactions on*, vol.47, no.3pp.281-289, Mar 2000

- [15] Kipke, D.R.; Vetter, R.J.; Williams, J.C.; Hetke, J.F., "Silicon-substrate intracortical microelectrode arrays for long-term recording of neuronal spike activity in cerebral cortex," *Neural Systems and Rehabilitation Engineering, IEEE Transactions on [see also IEEE Trans. on Rehabilitation Engineering]*, vol.11, no.2pp. 151- 155, June 2003

- [16] P. Fromherz, C.O. Muller and R. Weis, "Neuron transistor: Electrical transfer function measured by the patch-clamp technique," *PHYSICAL REVIEW LETTERS*, vol. 71, pp. 4079-4082, Dec 13. 1993.

- [17] R. Weis and P. Fromherz, "Frequency dependent signal transfer in neuron transistors," *Physical Review E*, vol. 55, pp. 877-889, JAN. 1997.

- [18] A. Stett, B. Müller and P. Fromherz, "Two-way silicon-neuron interface by electrical induction," *Physical Review E*, vol. 55, pp. 1779-1782, 1997.

- [19] M. Jenkner, B. Muller and P. Fromherz, "Interfacing a silicon chip to pairs of snail neurons connected by electrical synapses," *Biol. Cybern.*, vol. 84, pp. 239-249, Apr. 2001.

- [20] G. Zeck and P. Fromherz, "Noninvasive neuroelectronic interfacing with synaptically connected snail neurons immobilized on a semiconductor chip," *Proc.Natl.Acad.Sci.U.S.A.*, vol. 98, pp. 10457-10462, Aug 28. 2001.

- [21] P. Bonifazi and P. Fromherz, "Silicon Chip for Electronic Communication Between Nerve Cells by Non-invasive Interfacing and Analog–Digital Processing," *Adv Mater*, vol. 14, pp. 1190-1193, 2002.

- [22] Y. Tsividis, *Operation and modeling of the MOS transistor*, Boston: WCB/McGraw-Hill, 1999, pp. 620.

- [23] B. Razavi, *Design of analog CMOS integrated circuits*, Boston, MA: McGraw-Hill, 2001, pp. 684.

- [24] D. J. Edell, L.D. Clark and V.M. McNeil, "Optimization of electrode structure for chronic transduction of electrical neural signals", *Proceedings of the Eighth Annual Conference of the IEEE/Engineering in Medicine and Biology Society* 7-10 Nov. 1986, pp. 1626-9, 1986.

- [25] D. Banks, "Neurotechnology: Microelectronics" *Handbook of Neuroprosthetic Methods*, J.K. Petersen, W.E. Finn and P.G. Lopresti, CRC Press, 2002, .

- [26] A. P. Chandran, K. Najafi and K. D. Wise, "A new dc baseline stabilization scheme for neural recording microprobes," Engineering in Medicine and Biology, 1999.21st Annual Conf. and the 1999 Annual Fall Meeting of the Biomedical Engineering Soc.] BMES/EMBS Conference, 1999. Proceedings of the First Joint, vol. 1, pp. 386, Oct 13-15, 1999.

- [27] C.C. Enz and G.C. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization," Proceedings of the IEEE, vol. 84, pp. 1584-1614, 1996.

- [28] Q. Huang and C. Menolfi, "A 200 nV offset 6.5 nV/√Hz noise PSD 5.6 kHz chopper instrumentation amplifier in 1 μm digital CMOS," in 2001 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, 5-7 Feb. 2001, pp. 362-3, 2001.

- [29] A. Bakker, K. Thiele and J. H. Huijsing, "A CMOS nested-chopper instrumentation amplifier with 100-nV offset," *IEEE J Solid State Circuits*, vol. 35, pp. 1877-1883, EC. 2000.

# Chapter III. A chopper modulated neural recording system

#### 3.1 Introduction

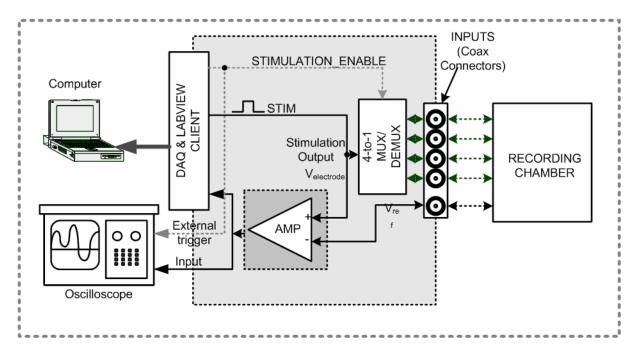

In this chapter we present practical implementations of some neural recording systems. These systems are designed to stimulate and monitor the electrical activity of a large population of cultured neurons using an array of recording sites within a shared substrate.

First, the design of a multi-channel chopper modulated amplifier is presented. The details of chopper modulation were explained in Chapter II. The compact amplifier cells use the well-known chopper technique [1] [2] instead of large amplifier input devices and high pass filters to reduce problems associated with flicker noise and DC offset. A local voltage reference is used to eliminate DC drift of the recorded signals via differential path amplification. Compact analog switches are used to multiplex the recording signal before amplification to minimize area and power. The amplifier chip is designed to use external neural signals as its inputs, or to use an internal electrode array for interfacing with neurons. The internal array is designed to have probe pads for interfacing with neurons.

Three different approaches were attempted. The first was to use open-gate, metal-free, insulated-gate field-effect transistors [3] for direct coupling of neuron to silicon without the interfering metal interface exhibited in microelectrode arrays [4]. This device was manufactured by the local processing facility at NC State University. The second approach was to use commercial micro-electrode arrays as the recording sources. In this case, commercially available recording devices were interfaced to the amplifier. The third approach was to use extracellular recording electrodes as used in tissue recording as the recording source.

### 3.2 Specifications

The target in this design is to be able to record neural signals using either planar electrodes, neuron-transistors or impaled microelectrodes. The voltage levels for the neural signals can be as low as  $500 \,\mu\text{V}$  [5] and the bandwidth is usually not more than  $10 \,\text{kHz}$  [5].

One of the problems with working with low frequency signals is that low frequency noise can interfere with the neural signals. The flicker noise and the DC offset of the amplifier itself can be problematic since their effects increase with the decrease of the frequency. Our system uses the *chopper modulation* technique to reduce the effects of this type of noise.

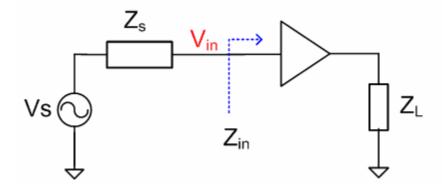

The output impedance of the recording device is a significant factor in determining the specifications. In the case of using planar or impaled electrodes, the output impedance is higher than  $2.2~k\Omega$ . Thus our amplifier should have a high input impedance to transfer the most of the signal. This is usually not hard to achieve because at low frequencies the input impedance of a CMOS-based amplifier is generally high.

The gain of this system is also very important. The signals must be amplified to a reasonable level for the detection of the neural signals. The neural signals can be as low as 500  $\mu$ V, but they can get higher for situations when there is a very high sealing resistance. Assuming that the maximum amplitude is not higher than 2 mV, a gain between 500 and 1000 seems reasonable. We selected a gain of 650 (56 dB) for this project. Also, to achieve optimum noise performance, we designed the system to be fully differential.

The bandwidth of the system is also an important issue for our application. Neural signals generally have a bandwidth of at most 10 kHz, but chopper modulation requires additional bandwidth to work properly. The internal system, which consists of the amplifier and the chopper modulator/demodulator, has a bandwidth of 130 kHz.

To avoid aliasing in the analog-to-digital conversion process, the signal bandwidth has to be reduced to a low level. To achieve this, we added a  $2^{nd}$  order low-pass filter with a cutoff frequency of  $5kHz \sim 10$  kHz. The output signal can also be further filtered by additional filters, if needed.

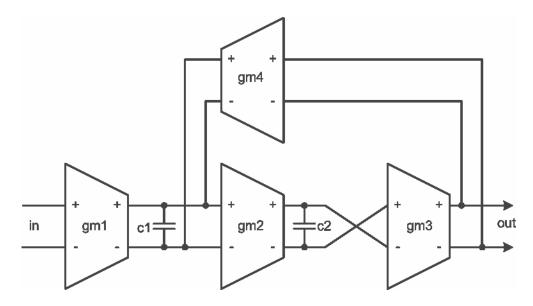

#### 3.3 Architecture

The top-level architecture of the chopper modulated amplifier is shown in Figure 1. The front-end system consists of an analog multiplexer, a chopper modulator, a cascode amplifier, a chopper demodulator and a low-pass filter. The inputs to the system are 4-to-1 multiplexed using an analog multiplexer. There is also a *reference* input, which is connected to the reference node of the recording environment.

One of the 4 inputs to the system is selected using the analog multiplexer, then it passes through a fully differential chopper modulator, which up-converts the signal to the chopper frequency. The signal is then amplified and demodulated back to the baseband by the output chopper demodulator. A final low-pass filter stage removes the remaining out-of-band noise for subsequent analog-to-digital conversion and signal processing.

Figure 1. Toplevel

### 3.3.1 Analog Multiplexer

The analog multiplexer allows the use of a single amplifier to service multiple recording sites. The circuit details of the 4-channel analog multiplexer are shown in Figure 2. The input and select signals are labeled IN0-IN3 and S0-S3, respectively. The select signals go off-chip allowing user control. The multiplexers are simply NMOS transmission gates that pass the signal when their gates are turned on and become high-impedance when their gates are turned off.

Charge injection cancellation is achieved by inserting dummy switches, which are driven by complementary select signals [1]. The dummy switches are also inserted between the recording sites and main switches to isolate the effect of charge feed-through from the neural signal.

Figure 2. 4-channel analog multiplexer

# 3.3.2 Chopper Modulator and Demodulator

The purpose of the modulator is to multiply the input with the waveform seen in Figure 3.

Figure 3. Chopper Signal

The simplest way to do this is using the circuitry is shown in Figure 4 [1]. The modulator inverts the signal when CLOCK is low and does not invert the signal when CLOCK is high. The demodulator is identical. However, the modulator and demodulator can be independently controlled which makes it possible to adjust for phase delay problems [1].

Figure 4. Chopper modulator/demodulator

# 3.3.3 Bias Circuitry

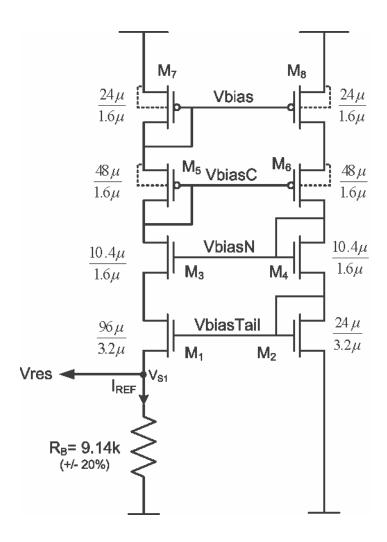

The purpose of the bias circuitry is to provide bias signals to the amplifiers in the chip. The bias circuitry is shown in Figure 5.

Figure 5. Bias Circuitry

This circuit is a modified version of a common biasing approach used in operational amplifier design [6]. In Figure 5, we can assume  $I_{DI} = I_{D2}$ , so we can write the following:

$$V_{GS_2} = V_{GS_1} + I_{ref} \times R_B \tag{7}$$

Assuming that threshold voltage is equal for both M1 and M2, we can write ...

$$V_{eff_2} = V_{eff_1} + I_{ref} \times R_B \tag{8}$$

... which can also be written as:

$$\sqrt{\frac{2I_{D2}}{\mu_n c_{ox}(W/L)_2}} = \sqrt{\frac{2I_{D1}}{\mu_n c_{ox}(W/L)_1}} + I_{D2}R_B$$

(9)

Since  $I_{D1} = I_{D2}$ , we can write ...

$$\sqrt{\frac{2I_{D1}}{\mu_n c_{ox}(W/L)_1}} = \sqrt{\frac{2I_{D1}}{\mu_n c_{ox}(W/L)_2}} + I_{D1}R_B$$

(10)

... which leads to:

$$\frac{2}{\sqrt{2\mu_{n}c_{ox}(W/L)_{1}I_{D1}}}\left[1-\sqrt{\frac{(W/L)_{1}}{(W/L)_{2}}}\right]=R_{B}$$

(11)

Remembering that

$$g_m = \sqrt{2\mu_n c_{ox}(W/L)I_D} \tag{12}$$

we can write

$$g_{m1} = \frac{2\left[1 - \sqrt{\frac{(W/L)_1}{(W/L)_2}}\right]}{R_R}$$

(13)

This means that the  $g_m$  values of the transistors will be determined by geometric ratios of the transistors and  $R_b$ . In this design, we selected  $(W/L)_1=4(W/L)_2$ , which results in:

$$g_{m1} = \frac{1}{R_B} \tag{14}$$

One of the advantages of this circuit is that the bias voltages can be adjusted even after the design using an external resistor. One of the resistor's terminals, which is labeled as *Vres*, is connected to a pad to externally set the resistor value.

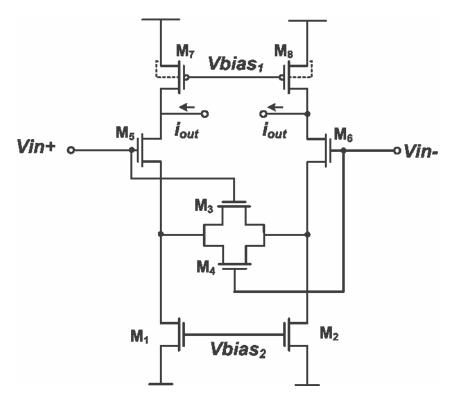

### 3.3.4 Cascode Amplifier

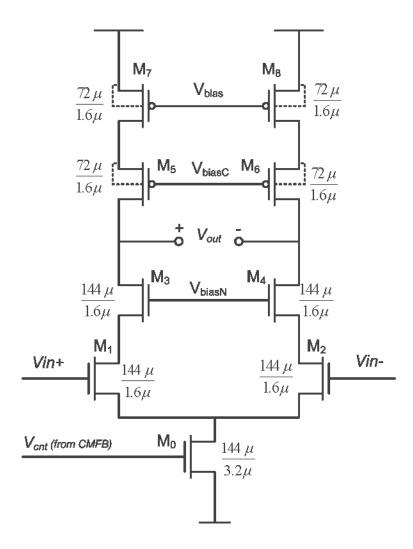

The amplifier used in this system is a fully-differential cascode amplifier which can be seen in Figure 6. A cascode amplifier topology is used because it achieves the highest gain with a single stage. The area of the input transistors can be reduced because their flicker noise contribution will be reduced by the chopper technique.

The principal factors that effected the amplifier type selection were:

*Input Dynamic Range*: The inputs to the amplifier may range between microvolts to 1 mV. Therefore, a gain somewhere in the range of 500-1000 was required.

*Noise:* Although our chopper implementation helped with the flicker noise, it offered no reduction in thermal noise. We needed to have a reasonably small amount of noise compared to the signal measured.

*Area:* The area available is fairly small in a cultured tissue and cell recording environment. Although multiplexing the input signals does reduce the area, it may still not be enough for recording via massive arrays.

The cascode amplifier is the best choice for the following reasons:

- It provides a large gain in a single stage.

- Area is reduced because there is no need for a second stage.

The cascode amplifier has an important drawback, which is the dynamic range of the output is somewhat limited due to the stacking of the transistors.

This amplifier exhibits a gain of 56 dB with a 115 kHz bandwidth. This configuration results in more than 80 dB CMRR.

Figure 6. Cascode amplifier

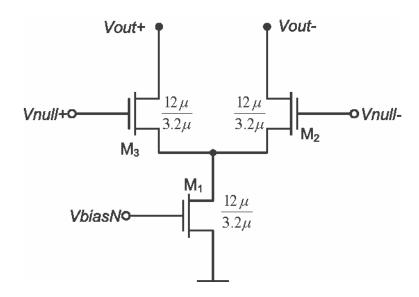

# 3.3.5 Common-Mode Feedback Circuit

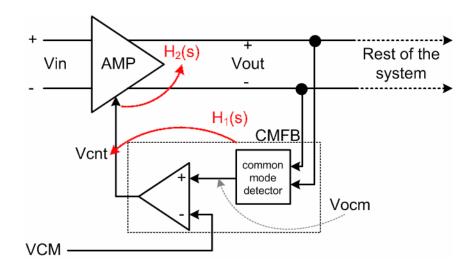

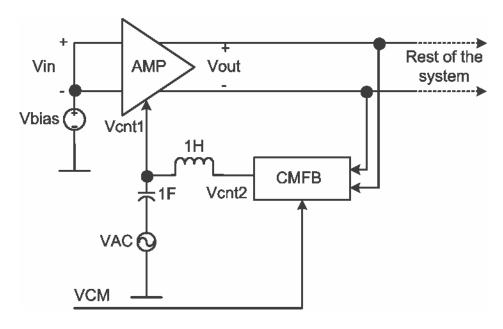

The common mode feedback circuit (CMFB) is used to suppress any variations in the quiescent point of the output voltage. The block diagram of the CMFB circuit is shown in Figure 7.

Figure 7. CMFB Block Diagram

The output common mode of the circuit can be is given as

$$Vout, cm = \frac{Vout(+) + Vout(-)}{2} = Vocm$$

(15)

The CMFB circuit forces the common mode voltage to be equal to *VCM*. The feedback equation can be written as follows:

$$\frac{Vocm}{Vcnt} = \frac{H_2(s)}{1 + H_1(s)H_2(s)}$$

(16)

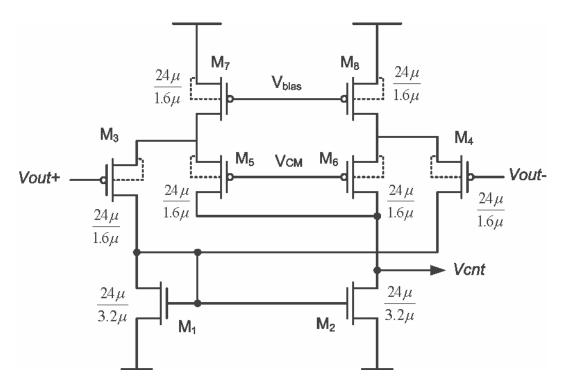

Figure 8 shows the circuitry we used to implement the CMFB system.

The circuit operates like this: as the common mode voltage at the amplifier output rises, drain current at  $M_3$  and  $M_4$  increases. The sum of these currents is equal to the drain current of  $M_1$ . This current mirrors to  $M_2$ . As the drain current,  $I_d$ , of  $M_2$  increases,  $V_{cnt}$  increases.

Figure 8. Common Mode Feedback circuit

# Stability Analysis

For stability analysis, we turn to the Figure 9 which is a depiction of a block diagram of the amplifier-CMFB loop.

Figure 9. Stability analysis of the CMFB loop

Assuming:

$$V_{cm} = \frac{V_{o+} + V_{o-}}{2} \tag{17}$$

The transfer function of the CMFB circuit is given as:

$$H_1(s) = \frac{V_{cnt}}{V_{cm}}(s) \tag{18}$$

And the loop completes with the second stage:

$$H_2(s) = \frac{V_{cm}}{V_{cnt}}(s) \tag{19}$$

In order to determine the stability of the system following method was used. The system was modified as shown in Figure 9. An AC sweep was conducted using the Spectre simulator. The loop gain and phase margin (PM) can be found using

$$\frac{V_{cnt2}(s)}{V_{cnt1}(s)} = H_1(s)H_2(s) \tag{20}$$

The simulation results showed that the PM of the system is 40 degrees and the gain is 120 (41 dB).

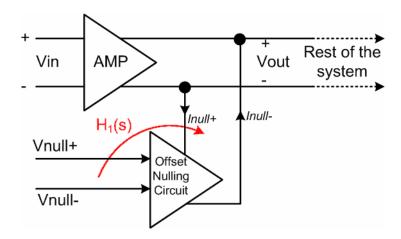

#### 3.3.6 Offset Correction Circuit

This system is also provided with a manual offset-cancellation circuit in case the chopper technique does not completely eliminate the offset. The block diagram of the offset-cancellation circuit and its connection to the amplifier is shown in Figure 10.

Figure 10. Offset-cancellation circuit block diagram

This block introduces a current mismatch at the output of the amplifier, which in turn creates a voltage offset at the output of the system, which allows any offset to be nullified.

The output offset can be reduced by the gain of the nulling circuit, which is found to be equal to 24 at low frequencies. So,

$$V_{offset(nulling)} = \frac{V_{offset(no-nulling)}}{24}$$

(21)

This device can be turned off by connecting its inputs to ground.

Figure 11. Offset correction circuit

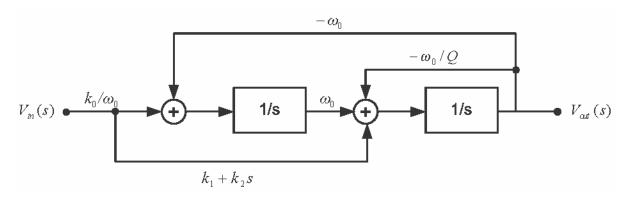

### 3.3.7 Low pass filter

The chopper demodulator's output will have the neural signal at the baseband and modulated flicker noise at higher frequencies. After that, a data-acquisition unit may be used to capture and analyze the signal. The modulated noise can be removed later with software. This

approach requires the sampling rate of the analog-to-digital converter to be at least twice the bandwidth of the previous stages. In order to reduce the required bandwidth, an analog low-pass filter is added to remove the noise beyond the desired signal range. This reduces the sampling rate requirement to a very low value. We chose a second order GM-C filter to filter out the noise.

The design of this filter involves several steps. The transfer function of a generalized 2<sup>nd</sup> order filter is given in (22) [6].

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{k_2 s^2 + k_1 s + k_0}{s^2 + (\frac{\omega_0}{Q})s + \omega_0^2}$$

(22)

The block diagram of this function can be seen in Figure 12.

Figure 12. 2nd degree filter block diagram

For a low pass filter, the values of  $k_2$  and  $k_1$  will be zero. Using transconductance cells, a low-pass circuit can be designed as seen in Figure 13. Equation (17) shows the transfer function.

Figure 13. Low Pass Filter

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{\frac{G_{m1}G_{m2}}{C_1C_2}}{s^2 + s\frac{G_{m3}}{C_2} + \frac{G_{m2}G_{m4}}{C_1C_2}}$$

(23)

Linearized transconductance circuits have been used to implement  $g_m$  stages [6, 7], as shown in Figure 14. The transconductance of such a cell is given in (24).  $G_m$  depends on bias current  $I_d$  and sizes of the transistors are  $M_1$  and  $M_2$ . Equation (25) defines  $k_3$  and  $k_1$ . In this circuit,  $M_1$  and  $M_2$  operate in the triode region, which improves the linearity of the circuit. Linearity is rather important in our system, because the input to the low-pass filter has a large signal swing. The common-mode voltages of the transconductance circuits are set by the common-mode feedback circuit shown in Figure 8.

$$G_m = \frac{4k_3\sqrt{k_1I_d}}{4k_3 + k_1} \tag{24}$$

$$k_k = \frac{\mu_k C_{ox}}{2} \frac{W_k}{L_k} \tag{25}$$

Figure 14. Linearized transconductance circuit

To better understand the  $g_m$  circuit, first we consider that it does not have any source degeneration at all. The output current, then, will be a function of  $V_{gs}^2$ :

$$I_{out} \propto k \times V_{gs}^{2}$$

(26)

This is not a good setup because it has a non-linear association. In order to increase linearity, we can use resistors across the sources of the input transistors. In this case, most of the output current will be a function of the voltage across the resistors, reducing the effect of the squared input voltage.

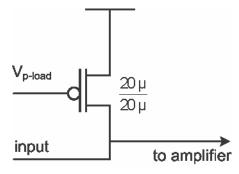

$$I_{out} \propto R \times V_{in} + k \times V_{in}^{2} \tag{27}$$